## DESIGN OF A CONFIGURABLE 3D NETWORK ON CHIP BASED ON THE DIRECT ELEVATOR 3D ROUTING ALGORITHM

By

Maha Ramadan Mohamed Beheiry

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics and Communications

FACULTY OF ENGINEERING , CAIRO UNIVERSITY GIZA, EGYPT OCTOBER 2017

## DESIGN OF A CONFIGURABLE 3D NETWORK ON CHIP BASED ON THE DIRECT ELEVATOR 3D ROUTING ALGORITHM

By

Maha Ramadan Mohamed Beheiry

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics and Communications

Under the Supervision of

Prof. Ahmed M. Soliman

Dr. Hassan Mostafa

Emeritus Professor Electronics and Communications Department Faculty of Engineering , Cairo University Assistant Professor Electronics and Communications Dept. Faculty of Engineering , Cairo University

FACULTY OF ENGINEERING , CAIRO UNIVERSITY GIZA, EGYPT OCTOBER 2017

## DESIGN OF A CONFIGURABLE 3D NETWORK ON CHIP BASED ON THE DIRECT ELEVATOR 3D ROUTING ALGORITHM

By

Maha Ramadan Mohamed Beheiry

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics and Communications

Approved by the Examining Committee:

Prof. First S. Name, External Examiner

Prof. Second S. Name, Internal Examiner

Prof. Ahmed M. Soliman, Thesis Main Advisor

### FACULTY OF ENGINEERING , CAIRO UNIVERSITY GIZA, EGYPT OCTOBER 2017

| Engineer's Name:          | Maha Ramadan Mohamed Beheiry   |

|---------------------------|--------------------------------|

| Date of Birth:            | 25/6/1990                      |

| Nationality:              | Egyptian                       |

| E-mail:                   | mahabehiry@gmail.com           |

| Phone:                    | 01064479725                    |

| Address:                  |                                |

| <b>Registration Date:</b> | 20/9/2012                      |

| Awarding Date:            | -/-/2017                       |

| Degree:                   | Master of Science              |

| Department:               | Electronics and Communications |

|                           |                                |

#### **Supervisors:**

Prof. Ahmed M. Soliman Dr. Hassan Mostafa

#### **Examiners:**

Prof. First S. Name Prof. Second S. Name Prof. Ahmed M. Soliman (External examiner) (Internal examiner) (Thesis main advisor)

#### Title of Thesis:

Design of a Configurable 3D Network on Chip Based on the Direct Elevator 3D Routing Algorithm

#### **Key Words:**

3D technology; 3D routing algorithm; SoCs; 3D-NoCs tool; 3D-NoCs generator.

#### **Summary:**

The main goal of the thesis is to provide the designers with a tool to create different configurations of the Three-Dimensional Network-On-Chips. These different configurational Three Dimensional (3D) Network-On-Chips (NoCs) will be then evaluated to determine which configuration is the best for a specific design or application. The 3D-NoCs are implemented based on a 3D routing algorithm denoted by Direct Elevator algorithm.

## **Table of Contents**

| Li | st of ' | <b>Fables</b> |                                                           | iv   |

|----|---------|---------------|-----------------------------------------------------------|------|

| Li | st of ] | Figures       |                                                           | V    |

| A  | cknov   | vledgen       | nents                                                     | viii |

| De | edicat  | ion           |                                                           | ix   |

| Al | bstrac  | et            |                                                           | x    |

| 1  | Intr    | oductio       | 'n                                                        | 1    |

|    | 1.1     | Motiva        | ation                                                     | . 1  |

|    | 1.2     | Contri        | bution                                                    | . 2  |

|    | 1.3     | Organ         | ization of The Thesis                                     | . 3  |

| 2  | Lite    | rature 1      | Review                                                    | 4    |

|    | 2.1     | 3D Ro         | outing Algorithms                                         | . 4  |

|    |         | 2.1.1         | LA-XYZ: A high throughput look-ahead routing algorithm    | . 4  |

|    |         | 2.1.2         | Topology Aware Adaptive Routing for irregular Mesh 3D-NoC |      |

|    |         |               | systems                                                   |      |

|    |         | 2.1.3         | Layered Routing in Irregular Networks                     |      |

|    |         | 2.1.4         | Elevator-First Routing Algorithm                          |      |

|    | 2.2     |               | ators and Tools to Create Various 3D-NoCs                 |      |

|    |         | 2.2.1         | Booksim Simulator                                         |      |

|    |         | 2.2.2         | Noxim Simulator                                           |      |

|    |         | 2.2.3         | NIRGAM: A simulator tool for NoC interconnect routing     |      |

|    |         | 2.2.4         | CONNECT tool to create different 2D-NoCs                  | . 23 |

| 3  | An      |               | w About The Three Dimensional Network-On-Chips            | 28   |

|    | 3.1     | Three         | Dimensional Technology                                    |      |

|    |         | 3.1.1         | 6 6                                                       |      |

|    |         |               | Vertical Interconnects Technologies                       |      |

|    | 3.2     | Differe       | ent Implementations and Applications with 3D Technology   |      |

|    |         | 3.2.1         | 3D Chip Structure with an iA32 Microprocessor             |      |

|    |         | 3.2.2         | CMOS Based Image Sensors Using 3D Technology              |      |

|    | 3.3     |               | enges of the 3D Integration Technology                    |      |

|    | 3.4     |               | ork-On-Chips                                              |      |

|    | 3.5     |               | rchitecture of NoCs                                       |      |

|    |         | 3.5.1         | Router Design                                             |      |

|    |         | 3.5.2         | Network Design                                            |      |

|    | 3.6     |               | Reconfiguration Using NoCs                                |      |

|    | 3.7     | The Tl        | hree Dimensional Network-On-Chips                         |      |

|    |         | 3.7.1         | The Architecture os 3D-NoCs                               | . 36 |

| 4 | Intr | oduction To The Network-On-Chip Methodology in FPGAs                                                                      | 38       |

|---|------|---------------------------------------------------------------------------------------------------------------------------|----------|

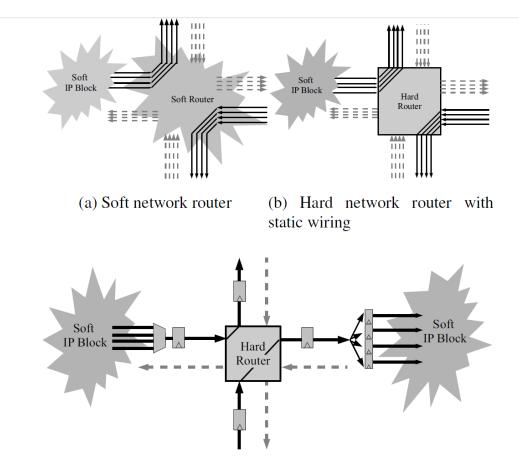

|   |      | 4.0.1 A comparison between the soft NoC and hard NoC on FPGA                                                              | 38       |

|   |      | 4.0.1.1 Router Architecture in the NoC hard implementations .                                                             | 39       |

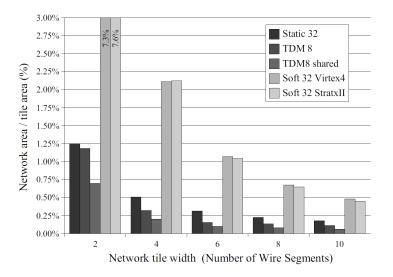

|   |      | 4.0.2 Area Results                                                                                                        | 40       |

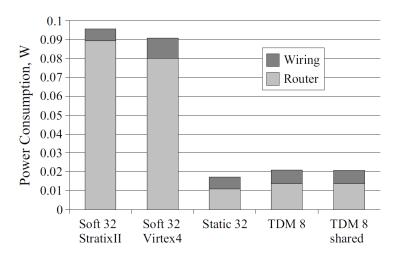

|   |      | 4.0.3 Power Results                                                                                                       | 41       |

|   | 4.1  | Impact of NoC parameters on the FPGA Network-On-Chips (NoCs)                                                              | 42       |

|   | 4.2  | A NoC design with debug features on Field-Programmable Gate Array                                                         |          |

|   |      | (FPGA)                                                                                                                    | 42       |

| 5 | The  | Direct Elevator Three Dimensional Routing Algorithm                                                                       | 45       |

|   | 5.1  | Introduction                                                                                                              | 45       |

|   | 5.2  | Elevator-First Three Dimensional Routing Algorithm                                                                        | 47       |

|   | 5.3  | The Direct-Elevator Three Dimensional Routing Algorithm                                                                   | 48       |

|   |      | 5.3.1 A packet routing path using Elevator-First mechanism                                                                | 48       |

|   |      | 5.3.2 A packet routing path using Direct-Elevator mechanism                                                               | 49       |

|   | 5.4  | Comparative Performance Analysis                                                                                          | 50       |

|   |      | 5.4.1 Network Load                                                                                                        | 51       |

|   |      | 5.4.2 Vertical Complexity                                                                                                 | 52       |

|   |      | 5.4.3 Tier Complexity                                                                                                     | 53       |

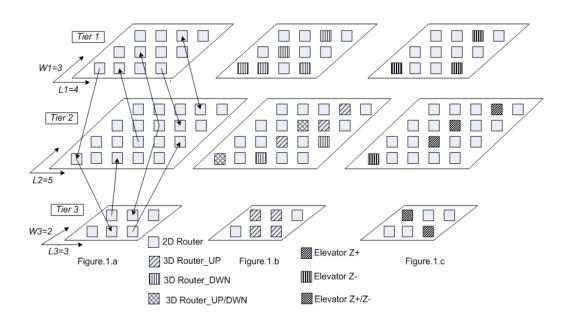

|   |      | 5.4.3.1 Regular Distributed 3D-NoC                                                                                        | 53       |

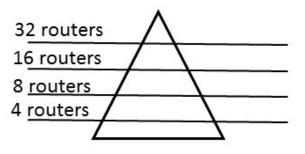

|   |      | 5.4.3.2 Hierarchical Distributed 3D-NoC                                                                                   | 55       |

|   | 5.5  | Summary                                                                                                                   | 55       |

| 6 | 3D-  | NOCET: A Tool for Implementing 3D-NoCs based on Direct-Elevator                                                           |          |

| U |      | orithm                                                                                                                    | 56       |

|   | 6.1  | Introduction                                                                                                              | 56       |

|   | 6.2  | The 3D-NOCET Tool User Guide                                                                                              | 58       |

|   | 0.2  | 6.2.1 Automation Infrastructure Scripts                                                                                   | 58       |

|   |      | 6.2.2 Register Transfer Level Design files                                                                                | 59       |

|   |      | 6.2.3 The 3D-NOCET tool implementation and execution flow                                                                 | 60       |

|   |      | 6.2.4 How to use the 3D-NOCET tool suite                                                                                  | 81       |

|   |      |                                                                                                                           | 01       |

| 7 |      | ussion on A Comparative and Performance Study for Different Struc-<br>s of 3D-NoCs                                        | 82       |

|   | 7.1  | Introduction                                                                                                              | 82       |

|   | 7.1  | Comparative Results Analysis                                                                                              | 82       |

|   | 1.2  | 7.2.1 Vertical Network Complexity                                                                                         | 82       |

|   |      | 7.2.1 Vertical Network Complexity                                                                                         | 82<br>82 |

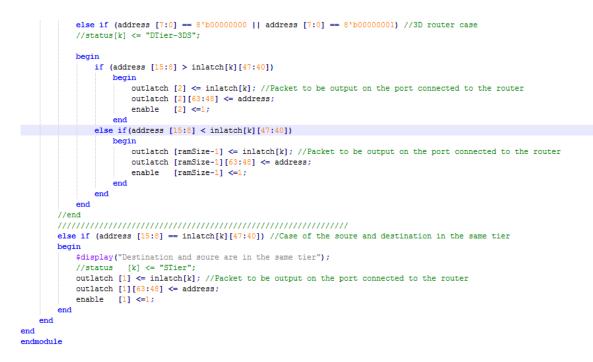

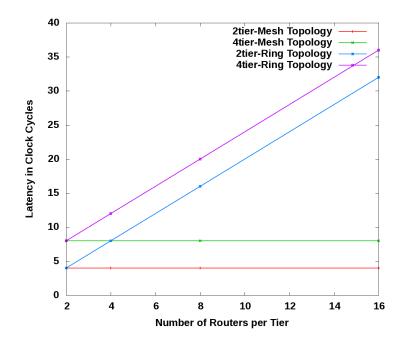

|   |      | 7.2.1.2 Impact of Vertical Complexity on The Eatency                                                                      | 82<br>83 |

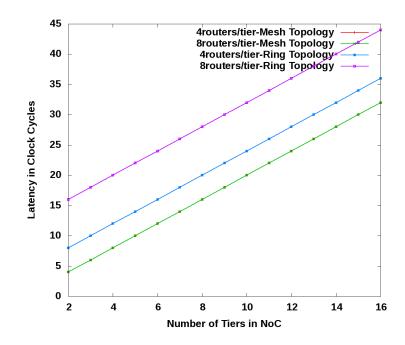

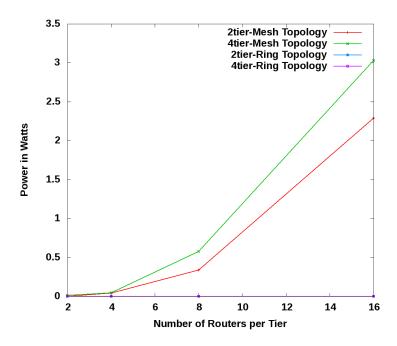

|   |      | 1 1 2                                                                                                                     | 83<br>84 |

|   |      |                                                                                                                           |          |

|   |      | 7.2.2 Tier Network Complexity                                                                                             | 85<br>86 |

|   |      | <ul><li>7.2.2.1 Impact of Tier Complexity on The Latency</li><li>7.2.2.2 Impact of Tier Complexity on The Power</li></ul> |          |

|   |      | 1 1 2                                                                                                                     | 86       |

|   | 7 2  | 7.2.2.3 Impact of Tier Complexity on The Area                                                                             | 87       |

|   | 7.3  | Work Conclusion                                                                                                           | 89<br>80 |

|   | 7.4  | Future Work                                                                                                               | 89       |

#### References

| Appendix A | <b>3D-NOCET Tool Source Files</b> | 93 |

|------------|-----------------------------------|----|

|            |                                   | 20 |

90

## **List of Tables**

| 2.1 | Some Parameters of the Booksim Simulator (Available in both versions of |    |

|-----|-------------------------------------------------------------------------|----|

|     | Booksim)[1]                                                             | 20 |

| 2.2 | Different NoC simulator and synthesizers[2]                             | 26 |

| 2.3 | A comparison between different simulators[2]                            | 27 |

| 2.4 | Nomenclature of the comparison table[2]                                 | 27 |

| 3.1 | Comparison between different stacking techniques[3]                     | 29 |

| 3.2 | Comparison of vertical interconnect technologies[4]                     | 29 |

|     | The evaluated hard NoC implementations[5]                               |    |

| 4.2 | Router areas[5]                                                         | 40 |

# **List of Figures**

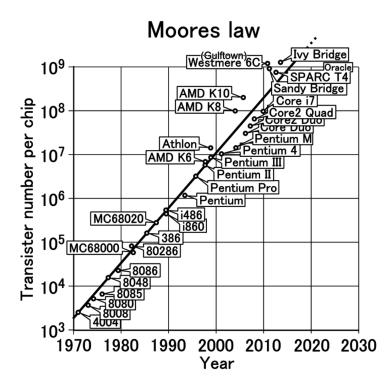

| 1.1  | Moore's law effect[6]                                                      | 1        |

|------|----------------------------------------------------------------------------|----------|

| 2.1  | Conventional XYZ routing algorithm[7]                                      | 5        |

| 2.2  | LA-XYZ routing algorithm flow[7]                                           | 5        |

| 2.3  | Step 1: LA-XYZ routing algorithm[7]                                        | 6        |

| 2.4  | Step 2: LA-XYZ routing algorithm[7]                                        | 8        |

| 2.5  | By-pass in LA-XYZ routing algorithm[7]                                     | 9        |

| 2.6  | The architecture of the 3D-NoC's router[7]                                 | 9        |

| 2.7  | The module of input-port[7]                                                | 10       |

| 2.8  | Larger path variety in TAAR routing aglorithm[8]                           | 11       |

| 2.9  | Operation flowchart of a transport layer and a network layer[8]            | 11       |

| 2.10 | (a) Packet B is waiting for Packet A, (b) Packet A is prepared to retrans- |          |

|      | mitted, and (c) Packet B start to enter the temporal storage[8]            | 11       |

| 2.11 | (a) Operation flow of TAMRA, and (b) An example[8]                         | 12       |

|      | Vertically partially connected 3D-NoC[9]                                   | 13       |

|      | Different routers in Vertically partially connected 3D-NoC systems[9]      | 14       |

|      | X-First 2D and Elevator-First Routing Algorithms[9]                        | 15       |

|      | Elevator First Routing in LOCAL input ports[9]                             | 16       |

|      | Elevator First Routing in 2D input ports[9]                                | 17       |

|      | Different routers in Vertically partially connected 3D-NoC systems[9]      | 18       |

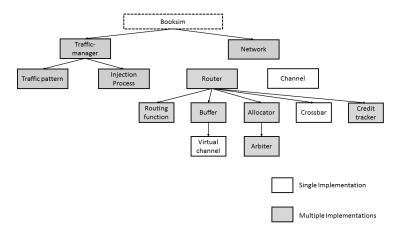

|      | Module hierarchy of the simulator[1]                                       | 19       |

|      | Top-level block diagram of the simulator[1]                                | 19       |

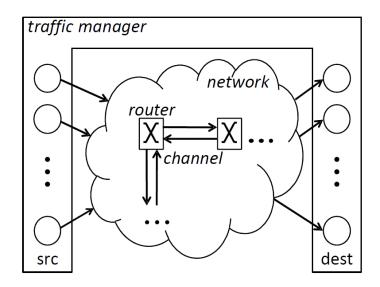

|      | Router module of Booksim tool[1]                                           | 20       |

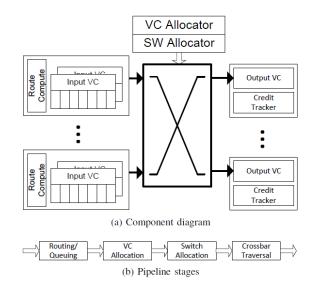

|      | Internal architecture of hub nodes with wireless communication[10]         | 20       |

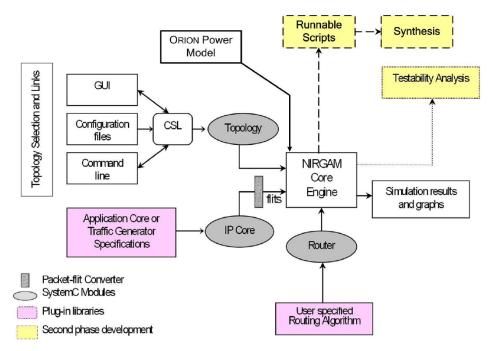

|      | NIRGAM Simulator Flow Diagram[11]                                          | 22       |

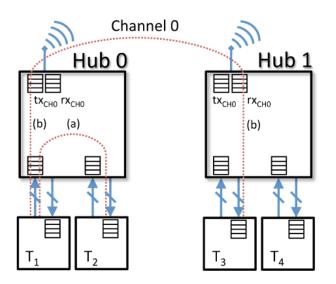

|      | CONNECT Router Architecture[12]                                            | 22       |

|      | CONNECT Tool[12]                                                           | 23<br>24 |

|      | Comparison between FPGA cost of SOTA and CONNECT router[12]                |          |

| 2.23 | comparison between 11 GA cost of SOTA and CONVLCT Touter[12]               | 23       |

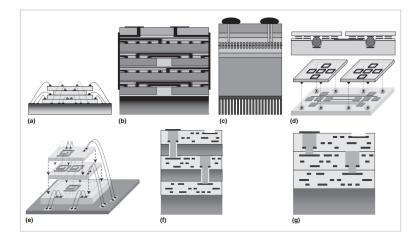

| 3.1  | Illustration of vertical interconnect technologies: wire bonded (a); mi-   |          |

|      | crobump3D package (b) and face-to-face (c); contactlesscapacitive with     |          |

|      | buried bumps (d) and inductive (e); through viabulk (f) and silicon on     |          |

|      | insulator (g)[4]                                                           | 30       |

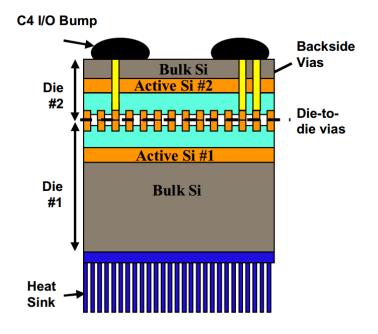

| 3.2  | 3D Structure[13]                                                           | 31       |

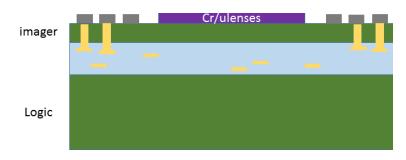

| 3.3  | A cross-section of an imager die schematic[14]                             | 32       |

| 3.4  | SAM image[14]                                                              | 32       |

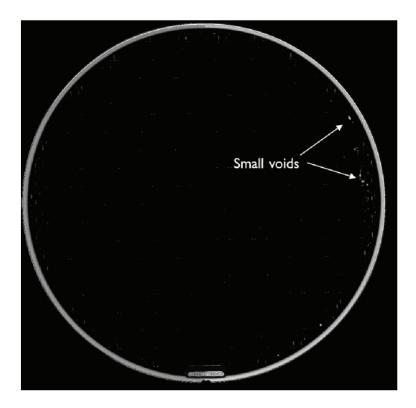

| 3.5  | Cooling used over a 3D structure[15]                                       | 33       |

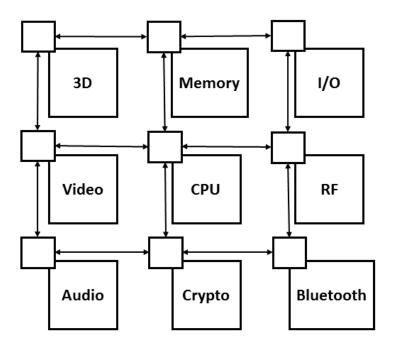

| 3.6  | Example of a NoC[16]                                                       | 34       |

| 3.7  | Two Inputs/Two Outputs router Implementation[17]                           | 35       |

| 3.8  | A NoC DPR Architecture[18]                                                 | 36       |

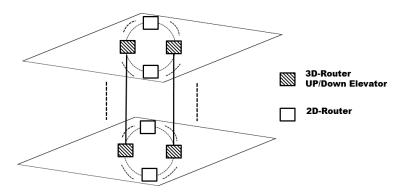

| 3.9  | 3D Mesh based network[19]                                                  | 37       |

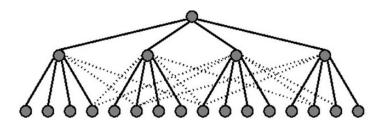

| 3.10 | Fat Tree Model[20]                                                         | 37       |

| 4.1  | Three NoC implementations[5]                                               | 40       |

| 4.2   | Percentage of router area to chip area[21]                                    | 41       |

|-------|-------------------------------------------------------------------------------|----------|

| 4.3   | Hard NoC and Soft NoC power consumption[21]                                   | 41       |

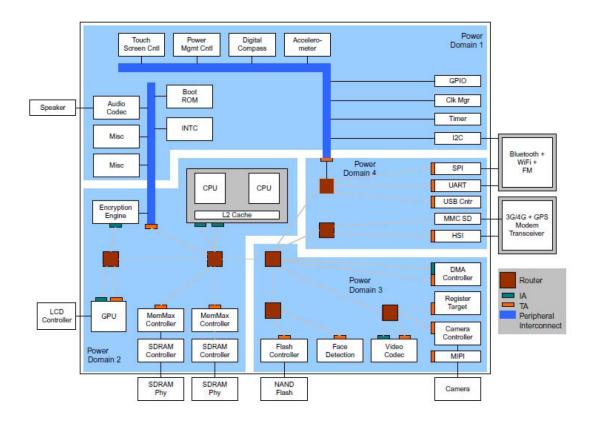

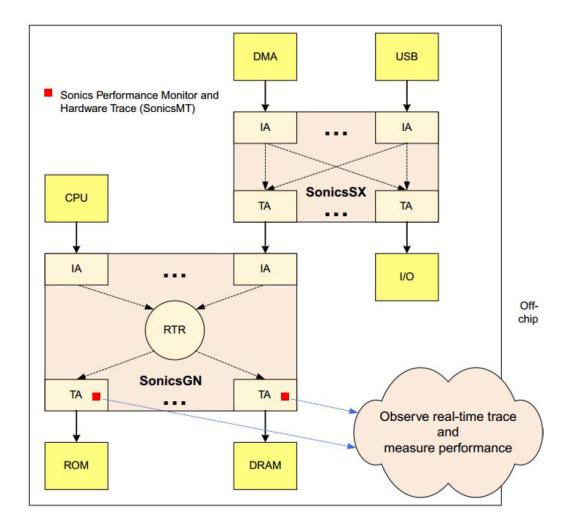

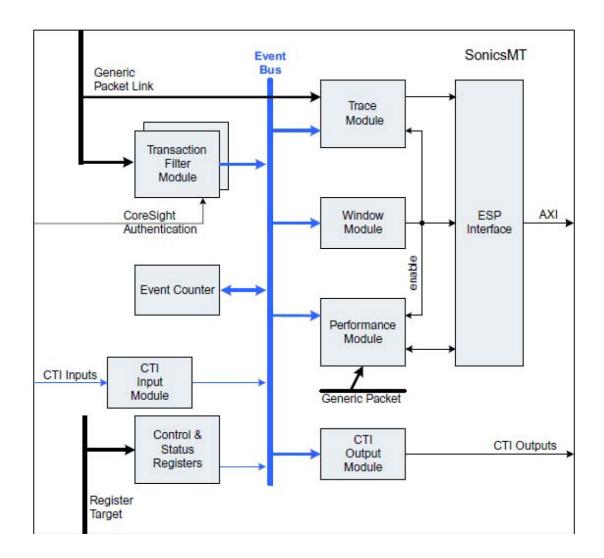

| 4.4   | SonicsGN NoC Architecture [22]                                                | 42       |

| 4.5   | The location of the performance tool in the SonicsGN NoC[22]                  | 43       |

| 4.6   | The Architecture of the performance and monitoring tool[22]                   | 44       |

|       |                                                                               |          |

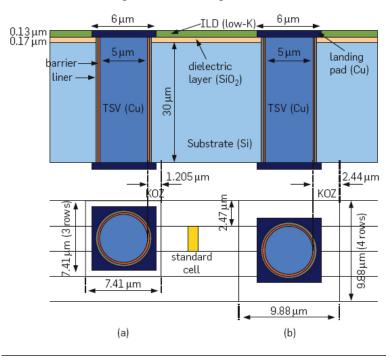

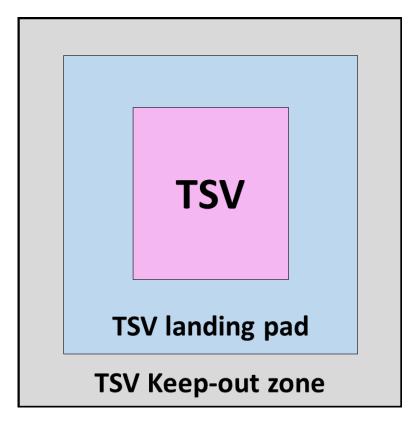

| 5.1   | TSV interconnect with landing pad[23]                                         | 45       |

| 5.2   | TSVA cell occupying three standard cell rows (KOZ = 1.205 m) and TSVB         |          |

|       | cell occupying four standard cell rows (KOZ = 2.44 m)[24]                     | 46       |

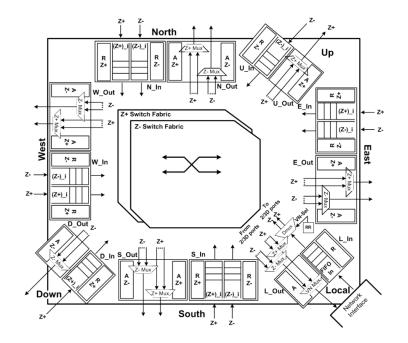

| 5.3   | Elevator-First 3D Router[9]                                                   | 47       |

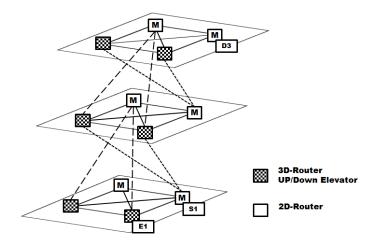

| 5.4   | Elevator-First routing mechanism[25]                                          | 49       |

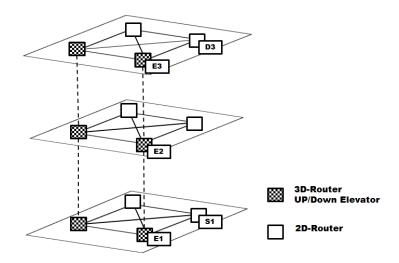

| 5.5   | Direct-Elevator routing mechanism[25]                                         | 50       |

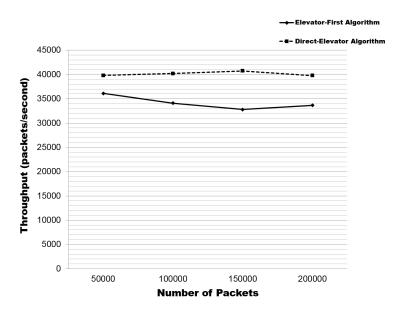

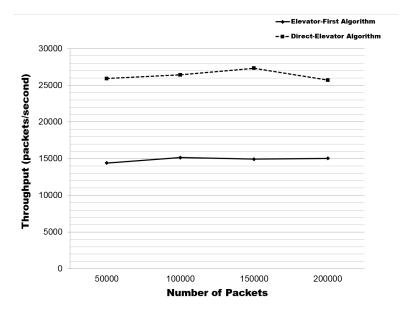

| 5.6   | Throughput Vs. Packets (random test case)[25]                                 | 51       |

| 5.7   | Throughput Vs. Packets (worst path test case)[25]                             | 51       |

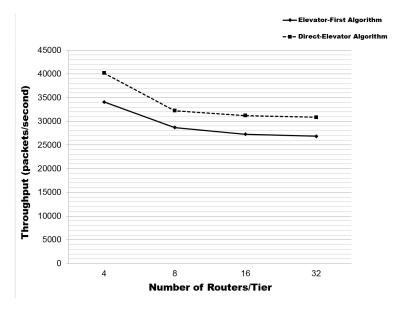

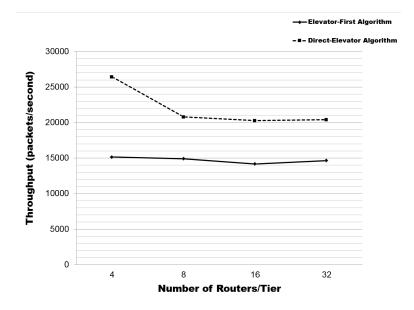

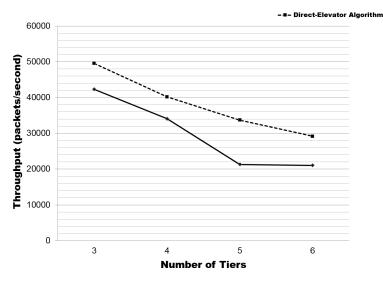

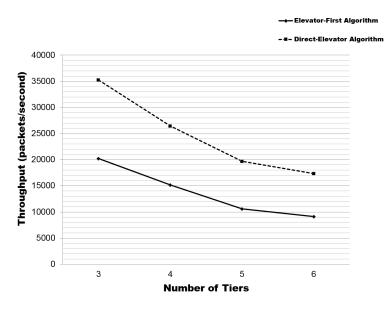

| 5.8   | Throughput Vs. Tiers (random test case)[25]                                   | 52       |

| 5.9   | Throughput Vs. Tiers (worst path test case)[25]                               | 53       |

| 5.10  |                                                                               | 54       |

|       | Throughput Vs. Routers/Tier (worst path test case)[25]                        | 54       |

|       | Hierarchical Structure of a 3D-NoC example                                    | 55       |

| 0.112 |                                                                               |          |

| 6.1   | The Graphical User interface of the 3D-NOCET tool                             | 57       |

| 6.2   | The 3D-NoC in 2D Mesh Topology                                                | 58       |

| 6.3   | The 3D-NoC in 2D Ring Topology                                                | 58       |

| 6.4   | The 3D-NOCET tool final information message                                   | 59       |

| 6.5   | The flow chart of the 3D-NOCET tool implementation                            | 60       |

| 6.6   | The main GUI window structure and the different valid topologies              | 61       |

| 6.7   | The implementation of the functionality buttons                               | 61       |

| 6.8   | Selection of the topology type                                                | 62       |

| 6.9   | Evaluating the parameters in the header file                                  | 62       |

| 6.10  | Determining the script flow according to the toplology type                   | 63       |

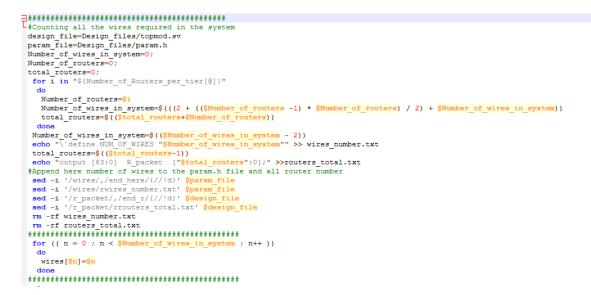

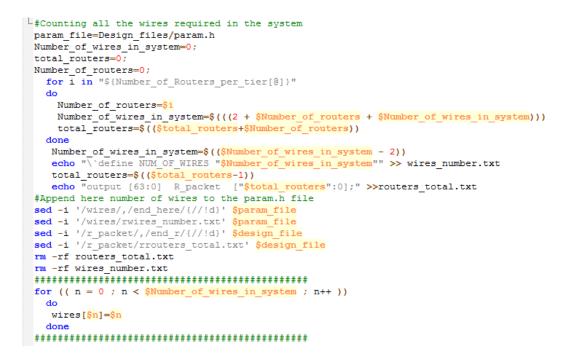

|       | Evaluating the number of wire in the 3D-NoC system using mesh topology        |          |

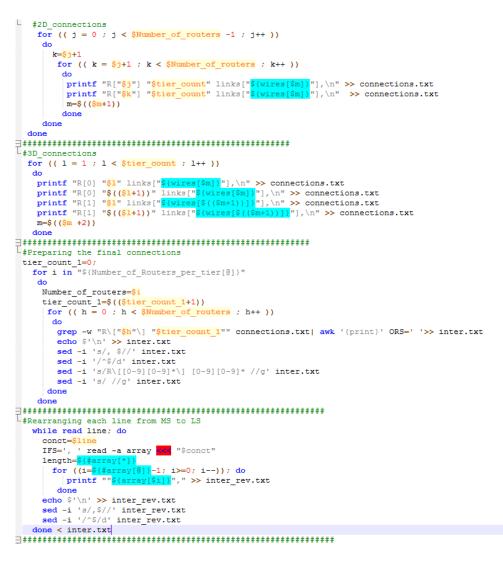

|       | Creating the connections between the routers in the mesh topology             |          |

|       | The instantiaions of the mesh routers                                         | 66       |

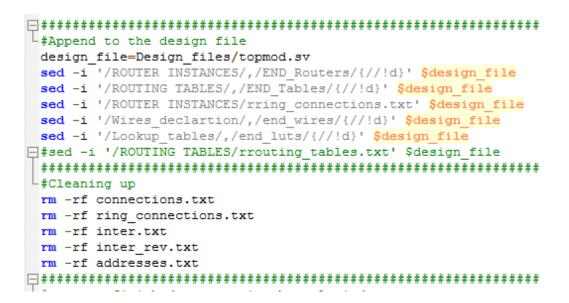

|       | Adding the mesh routers' instantiaions into the SystemVerilog top design file | 66       |

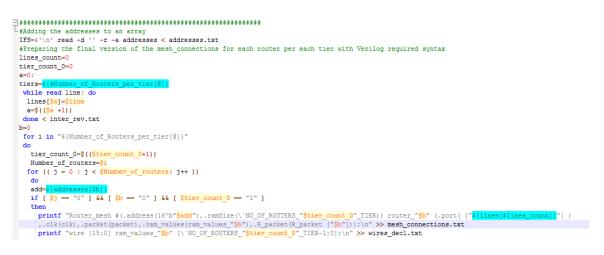

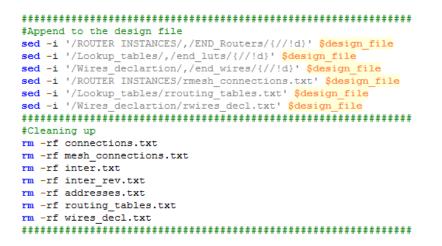

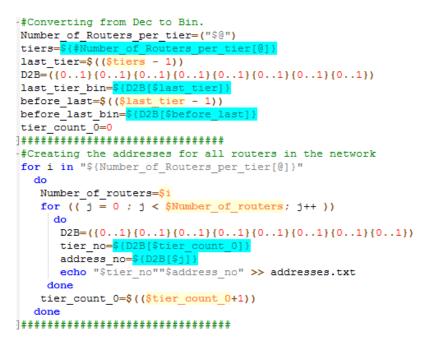

|       | Creating address for each router in mesh topology                             | 67       |

|       | Creating the routing tables in mesh topology                                  | 68       |

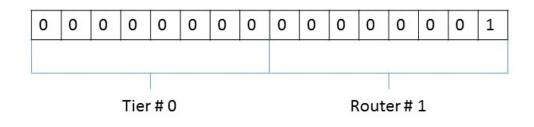

|       | The router address                                                            | 69       |

|       | Evaluating the number of wire in the 3D-NoC system using ring topology        | 69       |

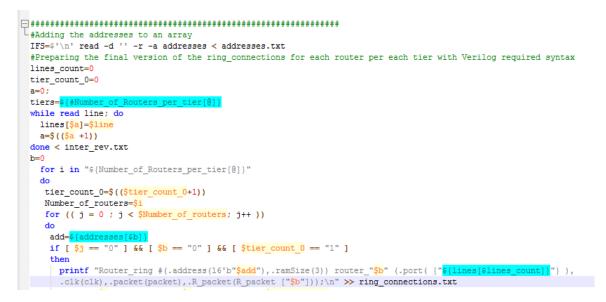

|       | Creating the connections between the routers in the ring topology             | 70       |

|       | The instantiaions of the ring routers                                         | 71       |

|       | Adding the ring routers instantiaions into the SystemVerilog top design file  | 71<br>71 |

|       |                                                                               | 72       |

|       | Creating address for each router in ring topology                             |          |

|       | The router instantiations in the top module design                            | 73       |

|       | The data in the routing table                                                 | 73       |

|       | The global parameters of the 3D-NoC system                                    | 73       |

|       | The testbench for simulations                                                 | 74       |

| 6.27  | The parameters of the mesh router module                                      | 75       |

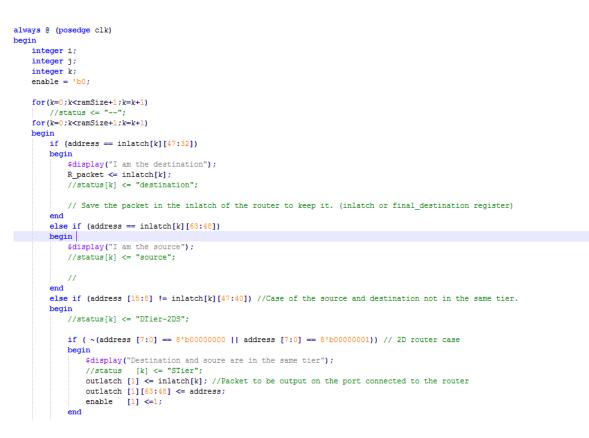

| 6.28                                                                        | The implementation of the 2D routing with mesh topology                | 76                               |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|

| 6.29                                                                        | The implementation of the Direct-Elevator algorithm in the 3D mesh     |                                  |

|                                                                             | router module                                                          | 77                               |

| 6.30                                                                        | The parameters of the mesh router module                               | 78                               |

| 6.31                                                                        | The implementation of the 2D routing with ring topology                | 79                               |

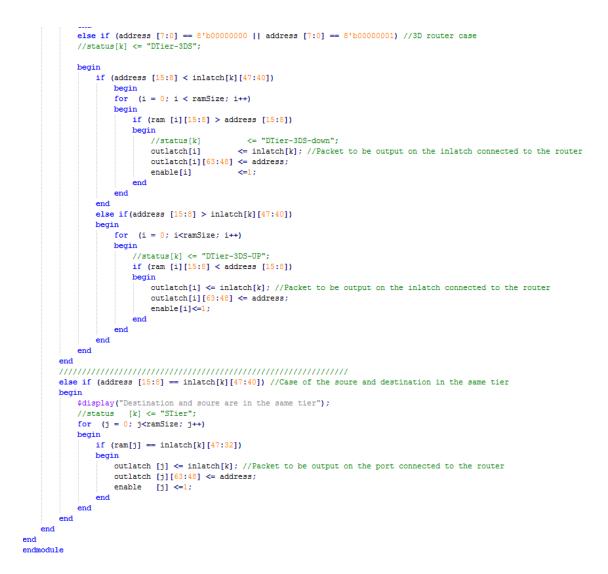

| 6.32                                                                        | The implementation of the Direct-Elevator algorithm in the ring router |                                  |

|                                                                             | module                                                                 | 79                               |

| 6.33                                                                        | The final information message                                          | 80                               |

| 6.34                                                                        | Design_files directory                                                 | 81                               |

|                                                                             |                                                                        |                                  |

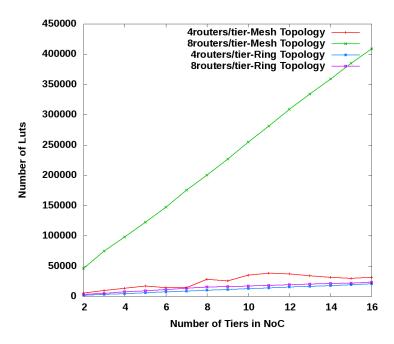

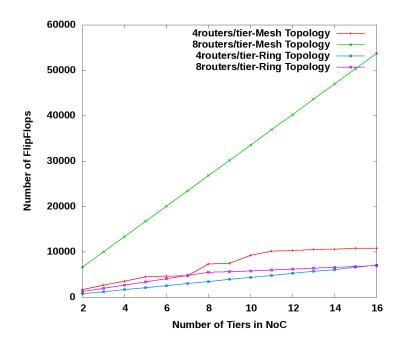

| 7.1                                                                         | Latency in Clock Cycles Vs. Number of Tiers in NoC                     | 83                               |

| 7.1<br>7.2                                                                  | Latency in Clock Cycles Vs. Number of Tiers in NoC                     | 83<br>84                         |

|                                                                             |                                                                        |                                  |

| 7.2                                                                         | Power in Watts Vs. Number of Tiers in NoC                              | 84                               |

| 7.2<br>7.3                                                                  | Power in Watts Vs. Number of Tiers in NoC                              | 84<br>85                         |

| 7.2<br>7.3<br>7.4                                                           | Power in Watts Vs. Number of Tiers in NoC                              | 84<br>85<br>85                   |

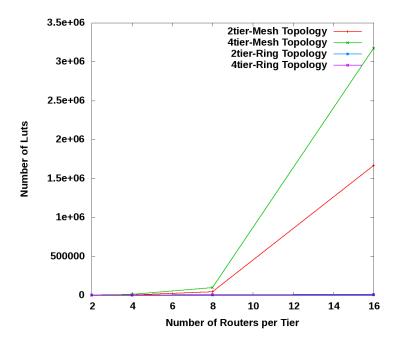

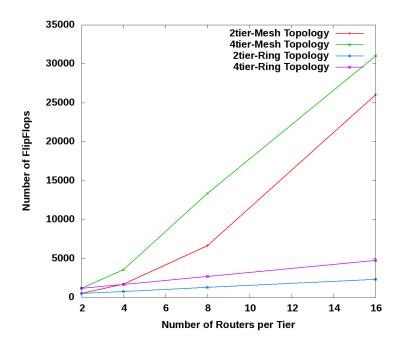

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>              | Power in Watts Vs. Number of Tiers in NoC                              | 84<br>85<br>85<br>86<br>87       |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul> | Power in Watts Vs. Number of Tiers in NoC                              | 84<br>85<br>85<br>86<br>87<br>88 |

## Acknowledgements

I would like first to thank my thesis supervisor Dr. Hassan Mostafa and Prof. Ahmed Soliman for their continuous support, patience and motivation. Besides my advisors, I would like to express my sincere gratitude to my awesome manager Rasha El Atfy for her generous support and encouragement. I would also like to thank my amazing workmates who helped me alot with their immense knowledge Hanan Moharam, Hager Fathy, Ali Mahgoub, Ahmed Emara and Rami Ahmed. Also, I am so grateful to Mennatallah Amer and Ahmed Maher for reviewing most of my work and give me insightful comments. Furthermore, My sincere thanks goes to my husband Ahmed Aly for helping me with his knowledge to implement and develop many ideas into my thesis and supporting me to finish this. Finally, I would like to thank my mother for her spiritual support throughout my life.

## Dedication

This work is dedicated to my lovely parents, to my wonderful brothers, and my beloved husband who always keeps pushing me out of all my comfort zones.

## Abstract

Three Dimensional integration technology offers a huge opportunity to implement different powerful applications. Moreover, the Network-On-Chip methodology solves the new challenges with the long wiring with new communication approach between the different nodes in one chip. Combining the 3D integration technology and the NoCs leads to such an attractive solution for many applications that have been impossible before. The 3D-NoCs come with variety of research challenges in maintaining the performance efficieny, the vertical interconnections design and placement, and manufacturing process steps. The routing challenge is one of the most vital challenges in implementing the 3D-NoCs. Therefore, implementing and developing a flexible and reliable routing algorithm to communicate between the different 3D stacked tiers is essential. As a part of this thesis work, a 3D routing algorithm, Direct-Elevator algorithm is independent on the number of the number of interconnects, placement of interconnects and the planar network topology. The Direct-Elevator is tailored for the 3D-NoC different structures. It offers a lower communication latency approach in comparison to Elevator-First routing algorithm.

A new tool is proposed in this thesis to provide a solution for the implementation of generic Three Dimensional (3D) Network-on-Chips (NoCs) to serve different applications and designs. The proposed tool denoted by 3D-NOCET, is based on the 3D Direct-Elevator routing algorithm. The 3D-NOCET tool allows the user to create different combinations of 3D-NoCs based on the 2D-routing topology, number of tiers and number of routers per each tier through a fully automation infrastructure.

That paves the road to perform diverse experimental evaluations for the different 3D-NoC structures. The future experimental evaluations and the performance comparative analyses help to find the optimal network configuration for different applications.

## **Chapter 1: Introduction**

### 1.1 Motivation

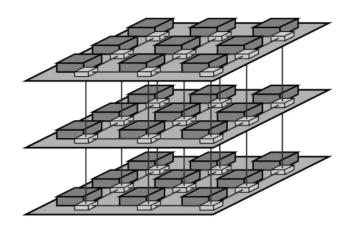

The Three Dimensional (3D) technology becomes very essential in overcoming the new design challenges. As the size of the transistor keeps shrinking, Moore's law continues to yield high transistor density with each new generation[26] as shown in Figure 1.1. The 3D technology enables the designer to stack and fabricate multiple dies in one chip. The 3D technology is such a powerful solution, but it comes with many other research challenges such as the thermal effect, the parastic capacitance between the vertical links and the floor planning techniques.

Figure 1.1: Moore's law effect[6]

On the other hand, The Network-On-Chip methodology offers vital solutions to the new wiring challenges in the chip fabrication process. The physical wiring connect the different cores in the System-On-Chip (SoC). The wires become thicker and longer in the top level of the design, which leads at last to very lossy global wiring[27]. The Network-On-Chip (NoC) technique introduces a new a new approach to communicate between the different cores in one chip. The NoC depends on different routers which communicate together to transfer the data from different sources to different destinations on the chip. The NoC design depends on different metrics such as: the router design, the network topology, the switching technique and other factors.

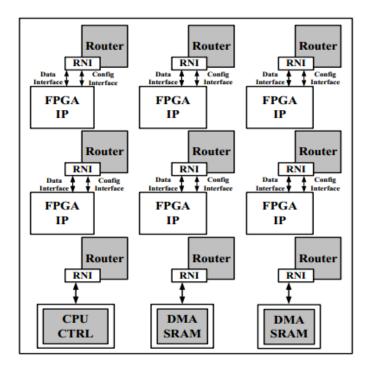

The NoC in the Field-Programmable Gate Array (FPGA) methodology is widely used in many applications. The NoCs in FPGA is able to enhance the system efficiency, increase the design production and reduce the system compilation time. The NoCs on FPGAs open the door to many innovative approaches such as the parial dynamic reconfiguration (PDR), in which the user can reconfigure a part of the FPGA while other parts are operating normally.

The combination between the 3D and the NoC approaches yields into a very powerful solution for many design challenges as illustrated above. The Three-Dimensional Network-On-Chips (3D-NoCs) have innumerous configurations based on many factors such as the network topology, the number of vertical stacked tiers, the number of routers per each tier and the switching techniques. The ability to create different configuration of the 3D-NoCs paves the road to the designers to explore the optimal configural 3D-NoC design that suits the most their applications. Moreover, creating these different configural 3D-NoCs using automated solution saves a lot of time and certainly gives a wide flexibility for performing many experiments. That is the main motivation behind this thesis work which is providing the designers with a powerful tool to create synthesizable 3D-NoCs.

### **1.2** Contribution

This work includes the following contribution:

- Implementing a 3D routing algorithm denoted by Direct-Elevator based on Elevator-First routing algorithm. The routing algorithm Direct-Elevator is used to route the packets vertically between the source and destination nodes. It is proved that it offers a lower communication latency than the Elevator-First algorithm.

- The two routing algorithms Elevator-First and Direct-Elevator are implemented using C programming language and a comparison study had been conduced to compare between the two algorithms.

- Creating a new tool denoted by 3D-NOCET to create different configural synthesizable 3D-NoCs based on the number of tiers in the system, the number of routers in each tier and the network planar topology.

- An analysis study has been conducted to evaluate different configurations for the 3D-NoCs and study the effect while varying the system aspects which are the number of tiers, the number of routers per each tier and the planar topology.

- A simple Graphical User Interface has been implemented for the tool to ease the usage and also to elaborate more on how the tool works.

### **1.3 Organization of The Thesis**

This thesis is oranized as follows. Chapter 2 contains a survey of the most significant previous work. The survey includes details different implemented 3D routing mechanisms and variety of distinct developed simulator and tools which are used to create 3D-NoCs and 2D-NoCs. Chapter 3 provides a detailed overview about the 3D-NoCs. In which, an overview about the 3D technology is presented followed by a brief about the NoC methodology. Then, a deep elaboration on the powerful combination between the 3D technology is detailed.

Chapter 4 includes a specific introduction to the NoC on FPGAs. The introduction highlights the benefits using the NoC methology on the FPGA and also the new challenges in designing the NoC for FPGAs. While in Chapter 5, the Direct-Elevator 3D routing mechanism is illustrated. The illustration spots the main differences between the two routing algorithms Elevator-First and Direct-Elevator. Moreover, a detailed comparison study is presented to evaluate the two routing algorithm with respect to the system total latency while changing the number of transmitted packets, the number of routers per each tier and the number of tiers in the system.

Chapter 6 presents the 3D-NOCET tool though a detailed user's guide that illustrates how the tool works exactly. Eventually, Chapter 7 contains a comparative and performance study on differnet configurations for the 3D-NoCs. The study illustrates the effect of the vertical network and tier network complexitiy on the 3D-NoC design. Moreover, it concludes the whole thesis work in a conclution section and also the future work that can be done.

## **Chapter 2: Literature Review**

## 2.1 3D Routing Algorithms

Many research work has been conducted to solve the challenges appear while using the 3D-NoCs. One of these challenges is developing and implementing a 3D routing algorithm to route the packets through the 3D stacked chips. The main target of the developed routing mechanisms is to keep the flexibility and utilization provided by the 3D-NoCs.

### 2.1.1 LA-XYZ: A high throughput look-ahead routing algorithm

This routing algorithm is developed to minimize the system communication latency and power consumption, also to improve the system overall throughput The 3D-NoC systems mainly depend on the Dimension Order Routing (DOR) XYZ algorithm. The routing algorithm routes the first packet flit to the X dimension, then to the Y and eventually to the Z dimension to reach its target. The output port is determined in this algorithm by comparing the processing node with the address of the final destination node[7]. Despite the face of that the routing algorithm is simple to be implemented and also free of lifelock and deadlock, but it has problems with inefficiency in the pipelining.

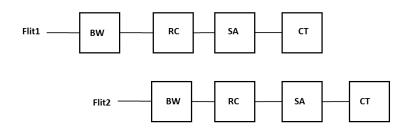

Figure 2.1 shows a router pipleline based on the XYZ routing in which the virtual channels are not considered to enhance the performance of the routing algorithm. The router pipline in Figure 2.1 is consisted of four pipelining as follows:

- Buffer Writing (BW).

- Routing Calculation (RC).

- Switch Arbitration (SA),

- Crossbar Traversal stage (CT).

The router introduces a latency overhead and power consumption as the packet needs to pass by all these four stages to reach its final destination. That will cause a very large decay in the performance of the whole system, also this problem is related proportionally to the network size.

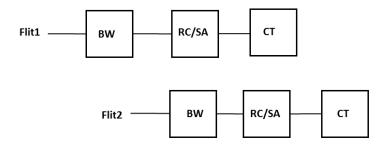

To solve this problem, the authors in this work proposed a Look-Ahead-XYZ routing algorithm which is denoted by LA-XYZ[7]. In this routing algorithm, a precomputition to the next port direction of the router is done then adds this information to the packet. When the packet arrives at the downstream node, the switch arbiter will use the next port identifier added to the packet to route the packet to the neighbour node. At the same time the routing calculation works in parallel to determine the next output port that the packet will take. This parallel procedure optimizes the pipelining time in the LA-XYZ routing algorithm as shown in Figure 2.2.

Figure 2.1: Conventional XYZ routing algorithm[7]

Figure 2.2: LA-XYZ routing algorithm flow[7]

The LA-XYZ routing algorithm mainly takes two steps to route the packets as follows:

1. Extracting the information of the next output port which is embedded in the packet. According to the direction of the output port, the address of the next node is calculated to be used in the next step. This step is illustrated in Figure 2.3.

### Algorithm 1: LA-XYZ 1st phase: Assign next address

```

// Current node address

Input: Xcur, Ycur, Zcur

// Next port identifier

Input: Next-port

// Next node address

Output: X_{next}, Y_{next}, Z_{next}

// Evaluate Next node x address

if (Next-port is EAST) then

X_{next} \leftarrow X_{cur} + 1;

else

if (Next-port is WEST) then

X_{next} \leftarrow X_{cur} - 1;

else X_{next} \leftarrow X_{cur};

end

// Evaluate Next node y_address

if (Next-port is NORTH) then

Y_{next} \leftarrow Y_{cur} + 1;

else

if (Next-port is SOUTH) then

Y_{next} \leftarrow Y_{cur} - 1;

else Y_{next} \leftarrow Y_{cur};

end

// Evaluate Next node z_address

if (Next-port is UP) then

Z_{next} \leftarrow Z_{cur} + 1;

else

if (Next-port is DOWN) then

Z_{next} \leftarrow Z_{cur} - 1;

else Z_{next} \leftarrow Z_{cur};

end

```

Figure 2.3: Step 1: LA-XYZ routing algorithm[7]

2. A comparison takes place between the current processing node and the destination address to know if the packet reaches its target or not. This step is illustrated in Figure 2.4.

### Algorithm 2: LA-XYZ 2nd phase: Define new Next-port

```

// Destination address

Input: X<sub>dest</sub>, Y<sub>dest</sub>, Z<sub>dest</sub>

// Next node address

Input: X<sub>next</sub>, Y<sub>next</sub>, Z<sub>next</sub>

// New next port for next node

Output: New-next-port

if (X_{next} \text{ is equal to } X_{dest}) then

if (Y_{next} is equal to Y_{dest}) then

if (Z_{next} is equal to Z_{dest}) then

New-next-port \leftarrow LOCAL;

else

if (Z_{next} \text{ is smaller than } Z_{dest}) then

New-next-port \leftarrow UP;

else New-next-port← DOWN;

end

end

else

if (Y_{next} \text{ is smaller than } Y_{dest}) then

New-next-port \leftarrow NORTH;

else New-next-port← SOUTH;

end

end

else

if (X_{next} \text{ is smaller than } X_{dest}) then

New-next-port \leftarrow EAST;

else New-next-port← WEST;

end

```

Figure 2.4: Step 2: LA-XYZ routing algorithm[7]

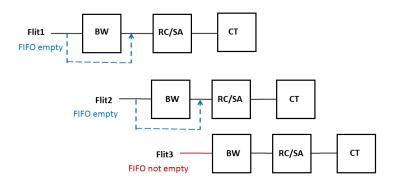

As an optimization approach in the LA-XYZ routing algorithm, a no-load bypass approach is taken as shown inFigure 2.5. The number of the pipelining stages can be optimized by overlapping the buffer writing stage. In this approach, if the input FIFO buffer is empty, the packet does not need to e stored and it will continue its path straight to the routing calculation and switch arbiteration stages which are still done in parallel.

Figure 2.5: By-pass in LA-XYZ routing algorithm[7]

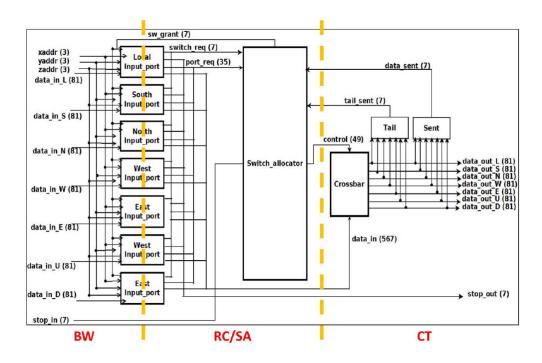

Figure 2.6, a full 3D-NoC's router system is shown. The architecture contains seven input modules for every direction in addition to the switch allocator and crossbar modules. While the input-port module is shown in Figure 2.7, each module contains two componenets: input buffer and router module[7].

Figure 2.6: The architecture of the 3D-NoC's router[7]

Figure 2.7: The module of input-port[7]

The 3D-NoC system which is using the LA-XYZ routing algorithm is evaluated with respect to the area utilization, power consumption and clock frequency. The authors used two famous benchmarks to evaluate their work which are as follows:

1. JPEG encoder application. The application is suitable to be used in evaluating the 3D-NoCs[28]. Additionally, the JPEG is a small application that can be mapped into eight nodes only.

That can show the benefits of the 3D-NoC and the LA-XYZ routing algorithm clearly.

2. Matrix multiplication application. This application has the potential in reaching the best performance in parallel architectures and also creating enough netowork traffic to evaluate the system performance.

# 2.1.2 Topology Aware Adaptive Routing for irregular Mesh 3D-NoC systems

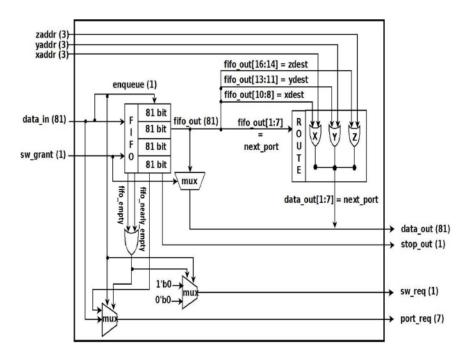

The thermal issue is such a critical challenge in the 3D-NoC systems. Therefore, the topology in these systems becomes irregular mesh topology. The routing algorithm here is proposed to balance the traffic load in the irregular Mesh 3D-NoCs[8]. The routing algorithm is denoted by Topology Aware Adaptive Routing (TAAR).

The traffic becomes more in balance in the irregular mesh systems as shown in Figure 2.8 because of the larger path variety in the proposed routing algorithm.

Figure 2.8: Larger path variety in TAAR routing aglorithm[8]

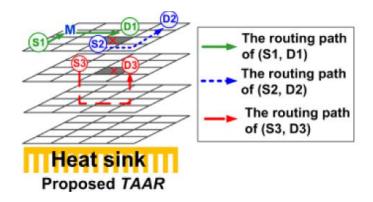

For the diversity of the packet routing path, an adjustment is proposed, denoted by Topology-Aware Multiple Routing Adjustment (TAMRA)[8]. In another adopted routing algorithms, the virtual channels technique is used to solve the deadlock issue. This technique comes with a very large area cost. In TAAR routing algorithm after considering the area issue caused by the virtual channels, a Store-and-Forward (SAF) policy is used to avoid the deadlock problem in the routing algorithm by cutting the violated turn as shown in Figure 2.9. The TAMRA has two stages of serial routing as shown in Figure **??**[8], the routed packets are temporarily saved in a network interface first.

The switching takes place, if there are two packets request the same output port direction. For the rerouted packets, an overhead latency happens due to the switching process.

The worse case is when each router transmits one packet per cycle, the excess overhead of the latency will equal to (the largest packet size) x 3 clock cycles. While comparing this worst case overhead latency to the overhead of the SAF policy which is at least 10 to the power seven cycles, the re-routed packets can be easily neglected.

Figure 2.9: Operation flowchart of a transport layer and a network layer[8]

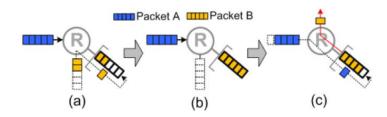

Figure 2.10: (a) Packet B is waiting for Packet A, (b) Packet A is prepared to retransmitted, and (c) Packet B start to enter the temporal storage[8]

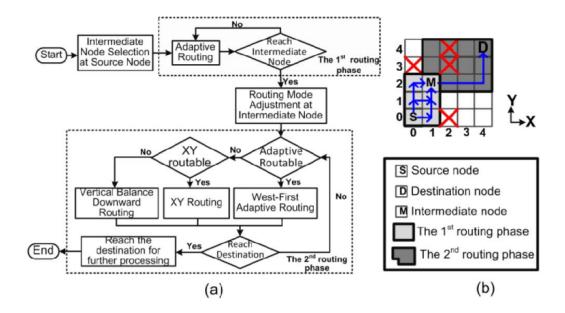

The flow charts of the TAMRA is shown in Figure 2.11. The first routing stage, the adaptive routing mechanism is used to reliver the routed packet from the source node S to the intermediated node M. The routing mode is then will be detemined according to the topology, then the packet will be routed from the M node to the final destination[8].

Figure 2.11: (a) Operation flow of TAMRA, and (b) An example[8]

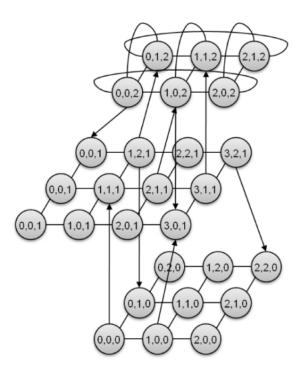

#### 2.1.3 Layered Routing in Irregular Networks

In this routing algorithm, the authors proposed a routing algorithm with groups of virtual channels in each network layer. For each virtual channels group, some source and destination address pairs are assigned[29]. That distribution in the traffic leads to an increase in the routing efficiency in the whole system.

The routing algorithm is easy to be implemented with no extra switch features than the already exist virtual channels.

The routing algorithm divides the the physical network intro number of layers. Each layer represent a virtual network with the same connection to the original physical network. The packets will remain in each layer where they are first injected. Moreover, a routing function will include all the necessary information on the routing in a specific layer. As a conclusion, the routing algorithm provides no restrictions on the paths that the packet may take through the network. Meanwhile, the deadlock issue is avoided by forcing the packets to use specific layers. That leads to a shortest path routing with also a load balancing routing approach.

The routing algorithm can be used in many applications. The simulation results show that the used techniques lead to a significant performance gains in comparison with the standard UpDown routing algorithm.

#### 2.1.4 Elevator-First Routing Algorithm

The Elevator-First routing algorithm is the most flexiable and generic routing algorithm proposed in all the previous mentioned routing algorithms. It is designed for vertically partially connected in regular 2D dies as shown in Figure 2.12, the different regular 2D dies can be in various shapes and sizes such as mesh, ring, star and torus.

Figure 2.12: Vertically partially connected 3D-NoC[9]

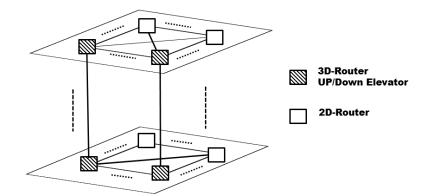

The authors proved that the routing algorithm is fully independent of the shapes and dimensions of the 2D topologies, and also the number and location of the TSVs in the 3D-NoC system. A Vertically-Partially-Connected 3DNoC which is supported by this routing mechanism can come with different numbe, placement and location of the vertical interconnects, as well as the topology in each stacked die. Figure 2.13, shows an example of such architecture in which the routers are divided into four types as follows:

- 1. 2D routers which have five conventional ports.

- 2. 3D routers which have up links to connect the stacked dies together.

- 3. 3D routers which have down links to connect the stacked dies together.

- 4. 3D routers which have both up and down links

Figure 2.13: Different routers in Vertically partially connected 3D-NoC systems[9]

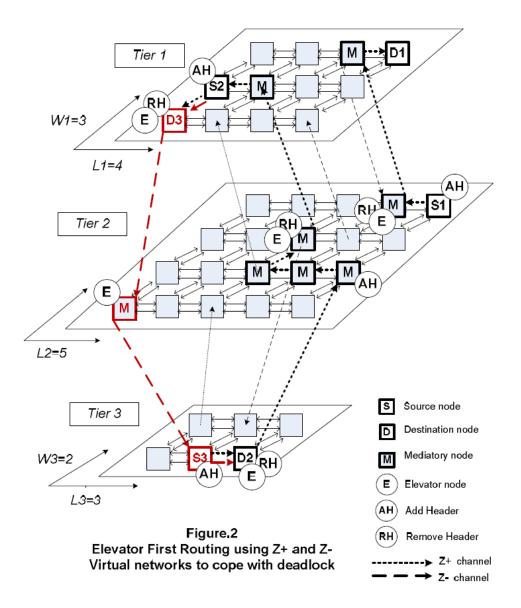

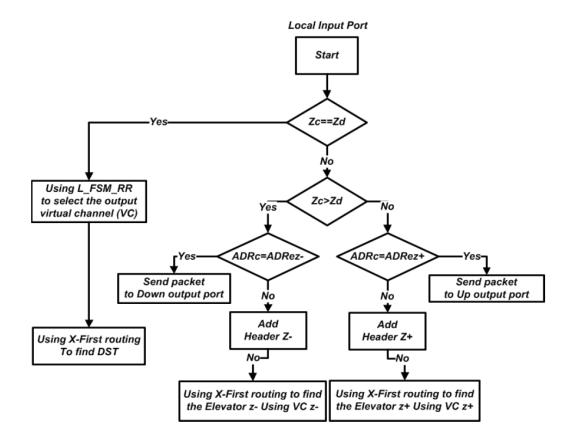

When issuing a packet through the 3D-NoC, if the source and destination nodes are in the same tier. Then, the packet will be routed directly according to the 2D topology in this tier. Otherwise, if the source and destination nodes are not in the same tier, an algorithmic dimension routing technique such as Z-first algorithm[9]. Figure 2.14 shows the Elevator-First algorithm flow, In tier two, a node S1 transmits a packet to a destination node D1 in an upper tier from the S1 node's tier. S1 has no direct vertical interconnect to the destination node D1. So, S1 will route the packet first to the Elevator Z+ in the same tier. It adds a temporary header to the packet that includes: Elevator address and two other flags. T and U flags are set to one, which means that the Elevator Z+ is not the final destination and that the packet is going up in the 3D-NoC. When the Elevator gets the packet and by checking the flag T. It realized that the header is temporary and will route the packet up as U flag is set to one.

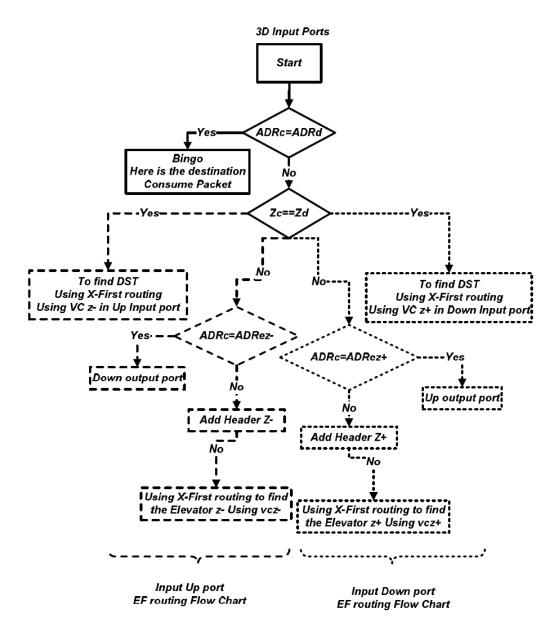

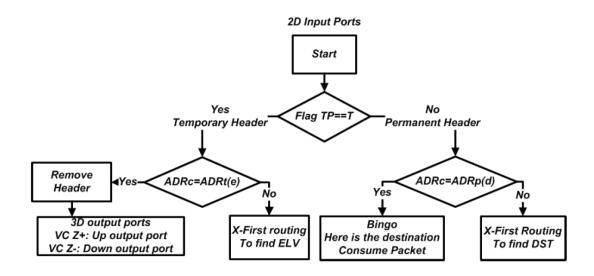

The packet will be forwarded to the upper link and gets into the intermediate stage through a mediatory node M. The check will then occur again to see if the M and D nodes are on the same tier, if not same sequence of logic will take place[9]. The flow charts of the Elevator-First algorithm are shown in Figure 2.15, Figure 2.16 and Figure 2.17[9].

Figure 2.14: X-First 2D and Elevator-First Routing Algorithms[9]

Figure 2.15: Elevator First Routing in LOCAL input ports[9]

Figure 2.16: Elevator First Routing in 2D input ports[9]

Figure 2.17: Different routers in Vertically partially connected 3D-NoC systems[9]

As a further work to implementing the Elevator-First algorithm, a 3D router is implemented to support the Elevator-First algorithm functionalities. The Elevator-First routing algorithm is the base of the Direct-Elevator algorithm which is proposed in this work which is illustrated in Chapter 4.

### 2.2 Simulators and Tools to Create Various 3D-NoCs

#### 2.2.1 Booksim Simulator

Booksim simulator tool is proposed to create different NoC architectures. A simulator is implemented to be a cycle-accurate simulator for the NoCs, it can also model the interconnects between the network nodes. The author released two versions of the tool. First. Booksim1 was a simulator that produces a generic networks that did not target the NoCs environmental setup. consequently, the simulator has been used in many network contexts. Also, it has been used to study many network aspects such as network topology, routing technique, flow control, router architecture and the quality of the networks. From the perspective of the system, Booksim offers a wide flexibility, that comes from paramitizing all the network components within the tool.

The simulator is designed in modules to ease the modification process that may take place in any module of the system. However, the benefits provided by Booksim1, yet it did not support some important features and topologies which are implemented in Booksim2. Booksim2 was implemented and developed to include many other modifications as it reflects in a better way the state-of-art in the NoC research. Specifically, its features are more detailed in moduling the router architecture, the communication channel delay and support for the additional traffic load models.

As a similator overview, the booksim is divided into hierarchical modules that imeplement different functionalities supported by the simulator as shown in Figure 2.18. Each module of these simulator modules has an interface which eases the replacement and modification of the module implementations without affecting other parts in the hierarchy.

Moreover, a top level block diagram is shown in Figure 2.19. The top lebel modules of Booksim are the traffic manager and the network. The traffic manager is a wrapper around the network that model the source and destination endpoints in the network. The wrapper injects packets into the network according to the user selected configuration which depends on the traffic pattern, packet size, packet injection rate and other aspects. The traffic manager is also responsible for ejecting the packets out of the network from the destination endpoints and terminating the simulation.

The network top level includes a group of routers and channels, which are connected according to the selected topology. The communication between all nodes accross the channels.

Figure 2.18: Module hierarchy of the simulator[1]

Figure 2.19: Top-level block diagram of the simulator[1]

A router has been implemented to support the Booksim tool funcionalities. The components of the router are divided into four stage pipelined design as shown in Figure 2.20.

Figure 2.20: Router module of Booksim tool[1]

The tool comes with alot of parameters as shown in Table 2.1, that provides the user with a large range of possible networks. The tool is available as open source tool in which the user can also access its source files[1].

Table 2.1: Some Parameters of the Booksim Simulator (Available in both versions of Booksim)[1]

| BookSim parameters                                   | Description                                                                              |

|------------------------------------------------------|------------------------------------------------------------------------------------------|

| Topology                                             |                                                                                          |

| topology                                             | Specifies the network connectivity based on well known topologies (e.g mesh, butterfly). |

| K,n                                                  | Specify the network size and configuration, for the selected topology.                   |

| Routing                                              |                                                                                          |

| routing_function                                     | Determines the routing algorithm for the selected topology (e.g., dimension order).      |

| Flow Control                                         |                                                                                          |

| num_vcs                                              | Number of virtual channels per physical channel.                                         |

| vc_buf_size                                          | Input buffer size of each virtual channel.                                               |

| wait_for_tail_credit                                 | Enable atomic VC allocation.                                                             |

| Router Microarchitecture                             |                                                                                          |

| vc_allocator, sw_allocator                           | The type of allocator used for switch and virtual channel allocation.                    |

| credit_delay, routing_delay,<br>vc_alloc_delay, etc. | Latency parameters for the router pipeline.                                              |

| input_speedup, output_speedup,<br>internal_speedup   | Speedup in the crossbar and router pipeline compared to network channels.                |

| Traffic                                              |                                                                                          |

| traffic_pattern                                      | Synthetic traffic pattern used in the simulation (e.g., uniform, transpose, etc. ).      |

| injection_rate                                       | Average injection rate for each node.                                                    |

#### 2.2.2 Noxim Simulator

Noxim simulator is developed based on SystemC, which is a system description library written in C++[10]. The main motivation behind implementing Noxim tool is allowing a scalable performances to the different generated NoCs. The architecture of the NoCs depends on two components which are as follows:

- The network nodes: which represent the main items of the Noxim architecture. Howeverthe network nodes are always related to the input and storage elements, buut they are also required to support different funcionalities related ro the data distribution.

- Processing elements: which are considered as the main components that actually performing storage and computation functionalities. The processing elements are also responsible for generating and consuming the data network packets.

- Routers: which are responsible for routing the data packets, communication techniques in the network and also implementing the flow control through the whole network system.

- Hubs: These components are playing a vital role in Noxim tool architecture as they allow the communications between any two non-adjacent nodes. The hub acts as an intermediate stage between the two nodes. The Noxim also provides an interesting possible architecture which is Hub-to-Hub wireless connection as shown in Figure 2.21.

Figure 2.21: Internal architecture of hub nodes with wireless communication[10]

• Channels: in which the packet is transmitted using a known wireless frequency. The frequency of the transmittion is taken by only one hub at a time.

Noxim offers a wide range of the NoCs that can be evaluated with respect to the power and performance. It is also available on the web as an open source tool for users.

#### 2.2.3 NIRGAM: A simulator tool for NoC interconnect routing

NIRGAM tool is implemented based on SystemC, which allow the user to experiment and evaluate different applicationd and routing mechanisms. It enables the user to analyze the performance with respect to the latency and the throughput[11]. Currently, the NIRGAM simulator supports mesh and torus topologies with wormhole switching technique.

The users can choose of the available embedded routing algorithms such as deterministic XY, deadlock free odd-even, source and Q-routing[11]. The Quality of Service is also taken into consideration as the user can reserve a certain amount of the available band width for Guaranteed Throughput (GT) load traffic.

Figure 2.22shows the flow diagram of the NIRGAM tool and its different modules.

Figure 2.22: NIRGAM Simulator Flow Diagram[11]

Currently the following parameters are supported by the NIRGAM simulator as follows:

- Topology: 2D Mesh and 2D Torus.

- Switching mechanism: Wormhole.

- Routing Algorithms: Source routing, deterministic XY and adaptive Odd-Even (OE).

- Applications: sender, reciever and traffic generator.

- Plug in to support network routers.

- Plug in to support the applications.

NIRGAM tool is also available on the web for downloading and usage

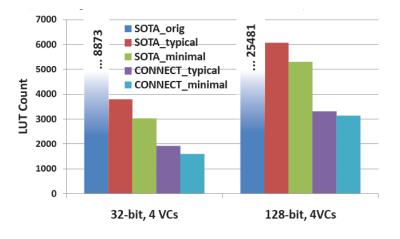

### 2.2.4 CONNECT tool to create different 2D-NoCs

CONNECT is a NoC generator that provide the user with synthesizable RTL designs. The NoCs produced from CONNECT are evaluated against high-quality RTL NoC based on ASICs. CONNECT NoC is meant to be part of an FPGA system[12]. Therefore, the CONNECT NoCs have to balance between two main tradeoffs:

- 1. Providing efficient performance to satisfy the application requirements.

- 2. Minimizing the usage of the FPGA resources to utilize them for the rest of the system components.

CONNECT takes both tradeoffs into consideration by makeing the NoC implementation as efficient as possible.

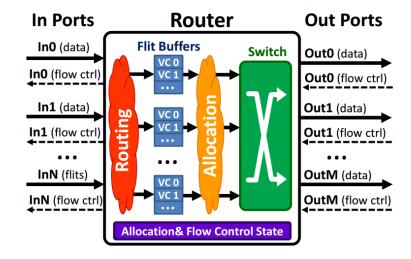

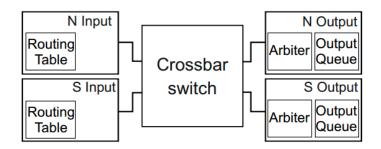

A router has been implemented for the communications over the NoCs created by CON-NECT. The routers are configurable due to many parameters, the router architecture is shown inFigure 2.23.

Figure 2.23: CONNECT Router Architecture[12]

The CONNECT tool comes with a web-based Graphical User Interface (GUI) as shown in Figure 2.24 that allows the user to enter all the 2D-NoC specifications regarding the following components:

- Network topology.

- Number of Endpoints.

- Router type.

- Number of virtual channels.

- Flow control type.

- Flit data width.

| Parameter                          | Value                               | Preview ( hide endpoints)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Network Topology                   |                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Topology 🛈                         | Double Ring -                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Number of Endpoints                | 8 -                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Network and Router Op              | tions                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Router Type 🛈                      | Virtual Channel (VC)                | R4 2 2 R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Number of VCs 🛈                    | 2 -                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |