# LOW POWER NANOMETER FPGA DESIGN TECHNIQUES AT THE DEVICE AND CITCUIT LEVELS

By

# Osama Ahmed Mohamed Ahmed Abdelkader

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics engineering

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT September - 2016

# LOW POWER NANOMETER FPGA DESIGN TECHNIQUES AT THE DEVICE AND CITCUIT LEVELS

By Osama Ahmed Mohamed Ahmed Abdelkader

> A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics engineering

> > Under the Supervision of

Ahmed M. Soliman

Hassan Mostafa

Professor of electronics Electronics and communications Faculty of Engineering, Cairo University Assistant Professor Electronics and communications Faculty of Engineering, Cairo University

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT September - 2016

# LOW POWER NANOMETER FPGA DESIGN TECHNIQUES AT THE DEVICE AND CITCUIT LEVELS

By Osama Ahmed Mohamed Ahmed Abdelkader

> A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Electronics engineering

Approved by the Examining Committee

Prof. Dr. First S. Name, External Examiner

Prof. Dr. Second E. Name, Internal Examiner

Prof. Dr. Third E. Name, Thesis Main Advisor

Prof. Dr. Fourth E. Name, Member

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT September – 2016

| Engineer's Name:          | Osama Ahmed Mohame    | d Ahmed               |

|---------------------------|-----------------------|-----------------------|

| Date of Birth:            | 21/12/1989            |                       |

| Nationality:              | Egyptian              |                       |

| E-mail:                   | Osama_abdelkader@me   | entor.com             |

| Phone:                    | +201114140997         |                       |

| Address:                  | 2 Nahda st – Hawamdia | - Giza                |

| <b>Registration Date:</b> | 1/1/2014              |                       |

| Awarding Date:            | /                     |                       |

| Degree:                   | Master of Science     |                       |

| Department:               | Electronics           |                       |

| Supervisors:              |                       |                       |

|                           | Prof. Ahmed M.Soliman | 1                     |

|                           | Dr. Hassan Mostafa    |                       |

| Examiners:                |                       |                       |

|                           | Prof                  | (External examiner)   |

|                           | Prof                  | (Internal examiner)   |

|                           | Porf                  | (Thesis main advisor) |

|                           | Porf                  | (Member)              |

#### **Title of Thesis:**

Low power nanometer FPGA design techniques at the device and circuit levels

#### **Key Words:**

FPGA; DTMOS; FinFET; Charge recycling; Low power

#### **Summary:**

We studied in this work replacing the conventional MOSFETs in FPGA with DTMOS and evaluated FPGA cluster and MUXs based on performance, power, and energy. DTMOS shows better energy for cluster (FPGA logic block), and MUXs (FPGA routing). We also studied using FinFET for technology nodes from 20nm down to 7nm, and also studied the impact of environmental variations on FinFET FPGAs metrics. Finally, we present a novel technique for FPGA power reduction on circuit level, the multiple charge recycling technique shows power saving by 32% in SPICE simulations.

# Acknowledgments

First, thanks God for everything that he has presented to me in life. I would like to express my appreciation and gratitude to the people who supported and encouraged me during my MSc study. Without their help I would not be able to complete this work.

I would like to express my sincerest appreciation and gratitude to my advisor Prof. Ahmed Soliman, for his continual guidance, support, motivating suggestions and encouragement during my research. His endless energy and enthusiasm in research has motivated all of his students including me. I wish him all the best. Also, I would like to express my gratitude to Dr. Hassan Mostafa for his important advices and comments for my thesis. It was an honor to have Dr. Hamdy Abdelhamid in my thesis work. I am grateful for their comments and objective directions to complete the master's thesis work.

Last but not least, I would like to extend my gratitude to the people who have helped and inspired me during my research. My heartfelt appreciation goes toward my family and my dearest parents. They were always supportive whenever it was a hard time for me.

# **Table of Contents**

| TABLE OF CONTENTS       II         LIST OF TABLES       IV         LIST OF FIGURES       V         ABSTRACT       VIII         CHAPTER 1 : INTRODUCTION       I         1.1.       FIELD-PROGRAMMABLE GATE ARRAYS.       1         1.2.       Technology scaling and emerging devices       2         1.3.       MOTIVATION.       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS.       3         CHAPTER 2 : LITERATURE REVIEW       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES.       4         2.3.       POWER DISSIPATION IN FPGA       12         2.3.1.       Dynamic power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY.       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.3.1.       Predictive technology models       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       22                                                                                  | ACKNOWLED     | GMENTS                                   | I    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|------|

| LIST OF FIGURES       V         ABSTRACT       VIII         CHAPTER 1 : INTRODUCTION       1         1.1.       FIELD-PROGRAMMABLE GATE ARRAYS       1         1.2.       TECHNOLOGY SCALING AND EMERGING DEVICES       2         1.3.       MOTIVATION       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS       3         CHAPTER 2 : LITERATURE REVIEW       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES       4         2.3.       POWER DISSIPATION IN FPGA       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.3.1.       Predictive technology models       27         3.3.1.       Predictive technology models       32         3.3.2.       FinFET FIGA components       33         3.3.3.       FinFET TFOGA co                                                                         | TABLE OF CO   | NTENTS                                   | II   |

| ABSTRACT       VIII         CHAPTER 1 : INTRODUCTION       1         1.1.       FIELD-PROGRAMMABLE GATE ARRAYS       1         1.2.       TECHNOLOGY SCALING AND EMERGING DEVICES       2         1.3.       MOTIVATION       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS       3         CHAPTER 2 : LITERATURE REVIEW       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES       4         2.3.       POWER DISSIPATION IN FPGA       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES       17         3.1.       INTRODUCTION       17         3.2.1.       DTMOS       17         3.2.1.       DTMOS       17         3.3.2.1.       Critical path simulation       32         3.3.2.1.       Critical path simulation       33         3.3.2.2.       FinFET FPGA components       33         3.3.3.       Fi                                                                                  | LIST OF TABL  | ÆS                                       | IV   |

| CHAPTER 1 : INTRODUCTION       1         1.1.       FIELD-PROGRAMMABLE GATE ARRAYS.       1         1.2.       TECHNOLOGY SCALING AND EMERGING DEVICES.       2         1.3.       MOTIVATION.       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS.       3         CHAPTER 2 : LITERATURE REVIEW.       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES.       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES.       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.1.       INTRODUCTION       17         3.2.1.       DTMOS FPGA structure       26         3.3.1.       Predictive technology models       27         3.3.1.       Predictive technology models       27         3.3.2.1.       DTMOS FPGA components       32         3.3.2.1.       Gritical path simulation <td< th=""><th>LIST OF FIGU</th><th>RES</th><th>V</th></td<> | LIST OF FIGU  | RES                                      | V    |

| 1.1.       FIELD-PROGRAMMABLE GATE ARRAYS.       1         1.2.       TECHNOLOGY SCALING AND EMERGING DEVICES.       2         1.3.       MOTIVATION.       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS.       3         CHAPTER 2: LITERATURE REVIEW       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES.       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3: DEVICE LEVEL POWER REDUCTION TECHNIQUES.       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.2.1.       DTMOS FPGA structure       26         3.3.1.       Predictive technology models       27         3.3.2.       FinFET Theoremotes       32         3.3.1.       Predictive technology models       27         3.3.1.       FinFET FPGA cluster       66 <th>ABSTRACT</th> <th></th> <th>VIII</th>                                    | ABSTRACT      |                                          | VIII |

| 1.2.       TECHNOLOGY SCALING AND EMERGING DEVICES.       2         1.3.       MOTIVATION.       2         1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS.       3         CHAPTER 2 : LITERATURE REVIEW         4       2.1.       INTRODUCTION       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES.       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES.         17       3.1.       INTRODUCTION       17         3.2.       DTMOS FPGA structure       26       26         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.       FinFET FPGA components       33         3.3.1.       Ortical path simulation       32         3.3.2.       FinFET FPGA cluster       66         CHAPTER 4 :                                                                                 | CHAPTER 1 : I | NTRODUCTION                              | 1    |

| 1.3.       MOTIVATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.1.          | FIELD-PROGRAMMABLE GATE ARRAYS           | 1    |

| 1.4.       THESIS CONTRIBUTIONS       3         1.5.       ORGANIZATION OF THE THESIS       3         CHAPTER 2 : LITERATURE REVIEW         4       4         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.2.          | TECHNOLOGY SCALING AND EMERGING DEVICES  | 2    |

| 1.5.       ORGANIZATION OF THE THESIS       3         CHAPTER 2 : LITERATURE REVIEW         2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES         17       3.1.       INTRODUCTION       17         3.1.       INTRODUCTION       17         3.2.1.       DTMOS       17         3.3.1.       Predictive technology models       27         3.3.1.       Predictive technology models       27         3.3.2.1.       Critical pats simulation       32         3.3.2.2.       FinFET FPGA components       32         3.3.3.       FinFET FPGA cluster       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES       67         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING                                                                         | 1.3.          | MOTIVATION                               | 2    |

| CHAPTER 2 : LITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.4.          | THESIS CONTRIBUTIONS                     | 3    |

| 2.1.       INTRODUCTION       4         2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES       4         2.3.       POWER DISSIPATION IN FPGA.       12         2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES         17       3.1.       INTRODUCTION       17         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.1.       INTRODUCTION       17         3.2.       DTMOS FPGA structure       26         3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.1.       Critical path simulation       32         3.3.2.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES       67         4.1.       INTRODUCTION       67                                                                                                       | 1.5.          | ORGANIZATION OF THE THESIS               | 3    |

| 2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHAPTER 2 : I | LITERATURE REVIEW                        | 4    |

| 2.2.       FPGA ARCHITECTURE AND HARDWARE STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.1.          | INTRODUCTION                             | 4    |

| 2.3.1.       Dynamic power       12         2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.2.       DTMOS       17         3.3.       FINFET       26         3.3.       FINFET       26         3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.       FinFET flip-flops       42         3.3.3.       FinFET FPGA cluster       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES       67         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                           | 2.2.          |                                          |      |

| 2.3.2.       Leakage power       13         2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES         17       3.1.       INTRODUCTION         3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.2.       DTMOS       17         3.2.1.       DTMOS FPGA structure       26         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET filp-flops       42         3.3.3.       FinFET FPGA cluster       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES       67         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                  | 2.3.          | POWER DISSIPATION IN FPGA                | 12   |

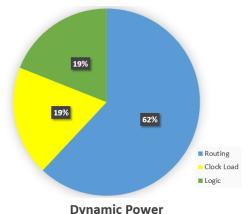

| 2.4.       RELATED WORK       13         2.5.       SUMMARY       16         CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3.1.        | Dynamic power                            | 12   |

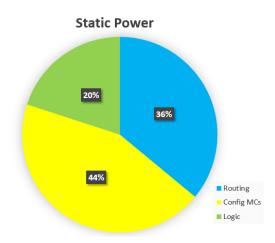

| 2.5.       SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.3.2.        | Leakage power                            | 13   |

| CHAPTER 3 : DEVICE LEVEL POWER REDUCTION TECHNIQUES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.4.          | RELATED WORK                             | 13   |

| 3.1.       INTRODUCTION       17         3.2.       DTMOS       17         3.2.1.       DTMOS FPGA structure       26         3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET flip-flops       42         3.3.3.       FinFET FPGA cluster       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.5.          | SUMMARY                                  | 16   |

| 3.2.       DTMOS       17         3.2.1.       DTMOS FPGA structure       26         3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET flip-flops       42         3.3.3.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CHAPTER 3 : I | DEVICE LEVEL POWER REDUCTION TECHNIQUES  | 17   |

| 3.2.1.       DTMOS FPGA structure       26         3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET flip-flops       42         3.3.3.3.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.1.          | INTRODUCTION                             | 17   |

| 3.3.       FINFET       27         3.3.1.       Predictive technology models       27         3.3.2.       FinFET FPGA components       32         3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET flip-flops       42         3.3.3.3.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.          | DTMOS                                    | 17   |

| 3.3.1.Predictive technology models273.3.2.FinFET FPGA components323.3.2.1.Critical path simulation323.3.2.2.FinFET flip-flops423.3.3.FinFET FPGA cluster613.4.SUMMARY66CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES4.1.INTRODUCTION674.2.FPGA ROUTING FABRIC HARDWARE674.3.CHARGE RECYCLING684.4.CR-CAPABLE INTERCONNECT BUFFER74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.2.1.        | DTMOS FPGA structure                     | 26   |

| 3.3.2.FinFET FPGA components.323.3.2.1.Critical path simulation323.3.2.2.FinFET flip-flops423.3.3.FinFET FPGA cluster613.4.SUMMARY66CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES4.1.INTRODUCTION674.2.FPGA ROUTING FABRIC HARDWARE674.3.CHARGE RECYCLING684.4.CR-CAPABLE INTERCONNECT BUFFER74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3.          | FinFET                                   | 27   |

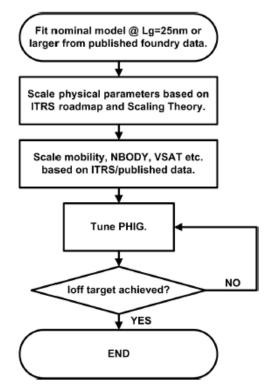

| 3.3.2.1.       Critical path simulation       32         3.3.2.2.       FinFET flip-flops       42         3.3.3.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.3.1.        | Predictive technology models             | 27   |

| 3.3.2.2.       FinFET flip-flops       42         3.3.3.       FinFET FPGA cluster       61         3.4.       SUMMARY       66         CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES         4.1.       INTRODUCTION       67         4.2.       FPGA ROUTING FABRIC HARDWARE       67         4.3.       CHARGE RECYCLING       68         4.4.       CR-CAPABLE INTERCONNECT BUFFER       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3.2.        | FinFET FPGA components                   | 32   |

| 3.3.3.FinFET FPGA cluster613.4.SUMMARY66CHAPTER 4 : CIRCUIT LEVEL POWER REDUCTION TECHNIQUES4.1.INTRODUCTION674.2.FPGA ROUTING FABRIC HARDWARE674.3.CHARGE RECYCLING684.4.CR-CAPABLE INTERCONNECT BUFFER74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | -                                        |      |

| 3.4.SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                                          |      |

| 4.1.INTRODUCTION674.2.FPGA ROUTING FABRIC HARDWARE674.3.CHARGE RECYCLING684.4.CR-CAPABLE INTERCONNECT BUFFER74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                          |      |

| 4.1.INTRODUCTION674.2.FPGA ROUTING FABRIC HARDWARE674.3.CHARGE RECYCLING684.4.CR-CAPABLE INTERCONNECT BUFFER74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CHAPTER 4 : ( | CIRCUIT LEVEL POWER REDUCTION TECHNIQUES | 67   |

| <ul> <li>4.2. FPGA ROUTING FABRIC HARDWARE</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                          |      |

| 4.3.Charge Recycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                          |      |

| 4.4. CR-CAPABLE INTERCONNECT BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                          |      |

| 4.6.      | EXPERIMENTAL STUDY     |    |

|-----------|------------------------|----|

| 4.7.      | SUMMARY                |    |

| DISCUSSIO | ON AND CONCLUSIONS     | 84 |

| REFERENC  | CES                    | 86 |

| APPENDIX  | A: INTRODUCTION TO VTR | 92 |

# **List of Tables**

| Table 2.1: Previous FPGA power reduction techniques                             | 16 |

|---------------------------------------------------------------------------------|----|

| Table 3.1: Major interconnects in the switch box                                | 20 |

| Table 3.2: PTM-MG models parameters                                             | 29 |

| Table 3.3: The simulated device parameters                                      |    |

| Table 3.4: The simulated device parameters of SD-FF                             | 45 |

| Table 3.5: Soft errors rate (In coulombs)                                       | 46 |

| Table 4.1: Power reduction and area overhead of each benchmark circuit in fully |    |

| populated with Multiple CR switches archirecture                                | 83 |

# List of Figures

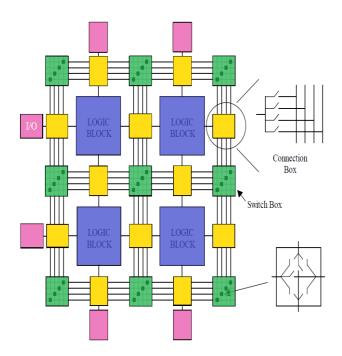

| Figure 2.1: FPGA architecture                                                                                                                                                                                                                                                                                                                            | 5                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

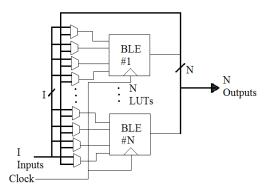

| Figure 2.2: FPGA cluster                                                                                                                                                                                                                                                                                                                                 | 5                               |

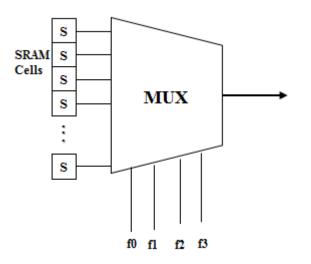

| Figure 2.3: Basic logic element                                                                                                                                                                                                                                                                                                                          | 5                               |

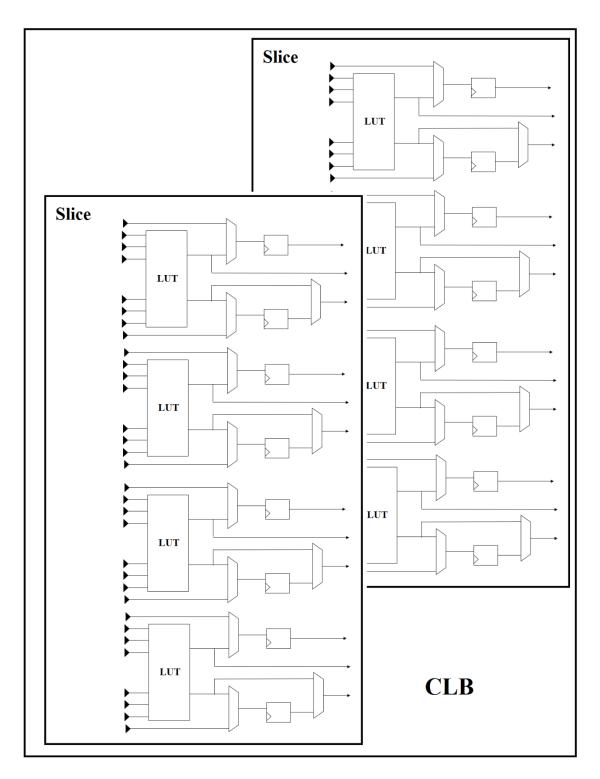

| Figure 2.4: Virtex-7 FPGA Cluster                                                                                                                                                                                                                                                                                                                        |                                 |

| Figure 2.5: Stratix-V FPGA logic array block                                                                                                                                                                                                                                                                                                             | 9                               |

| Figure 2.6: Stratix-V FPGA adaptive logic module                                                                                                                                                                                                                                                                                                         |                                 |

| Figure 2.7: FPGA switch buffer                                                                                                                                                                                                                                                                                                                           |                                 |

| Figure 2.8: Encoded multiplexer                                                                                                                                                                                                                                                                                                                          |                                 |

| Figure 2.9: Multiplexer inside look-up-table                                                                                                                                                                                                                                                                                                             | .11                             |

| Figure 2.10: Decoded multiplexer                                                                                                                                                                                                                                                                                                                         |                                 |

| Figure 2.11: Dynamic power breakdown in Spartan-3 FPGA                                                                                                                                                                                                                                                                                                   |                                 |

| Figure 2.12: Static power breakdown in Spartan-3 FPGA                                                                                                                                                                                                                                                                                                    |                                 |

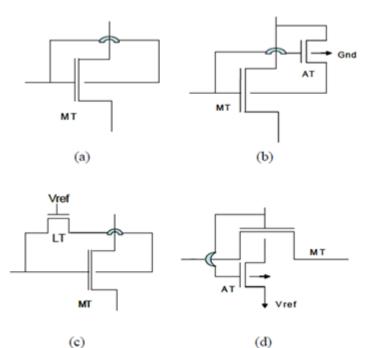

| Figure 3.1: DTMOS configurations                                                                                                                                                                                                                                                                                                                         |                                 |

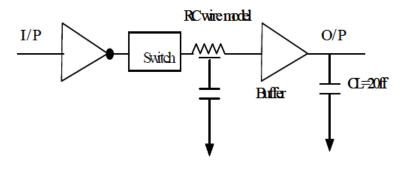

| Figure 3.2: Simulation setup                                                                                                                                                                                                                                                                                                                             |                                 |

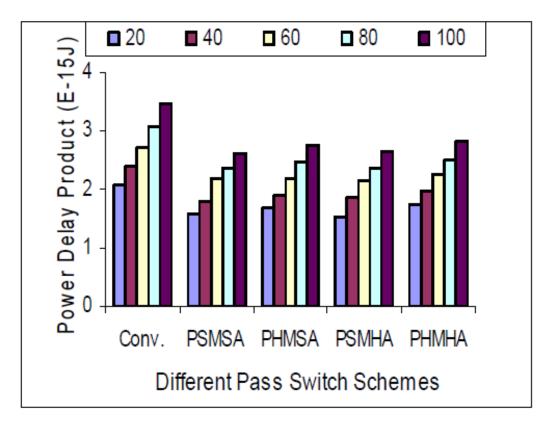

| Figure 3.3: PDP of pass switch vs. DTMOS schemes                                                                                                                                                                                                                                                                                                         |                                 |

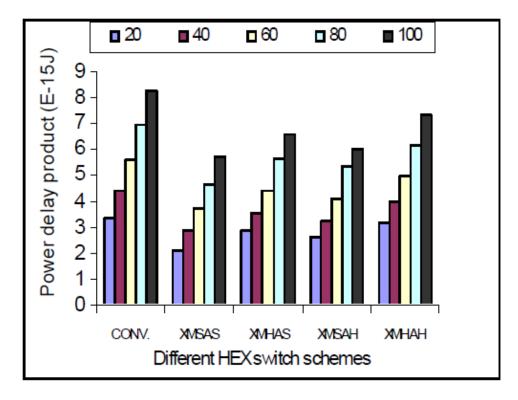

| Figure 3.4: PDP vs. HEX switch schemes                                                                                                                                                                                                                                                                                                                   |                                 |

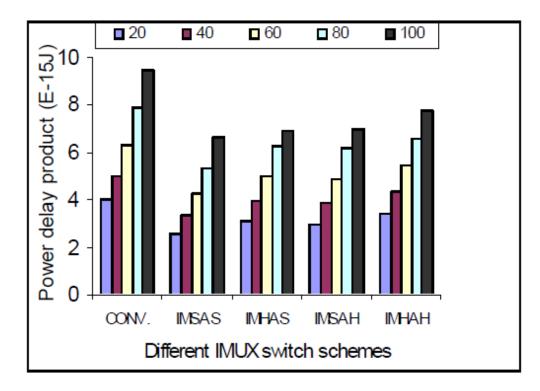

| Figure 3.5: PDP vs. IMUX switch schemes                                                                                                                                                                                                                                                                                                                  |                                 |

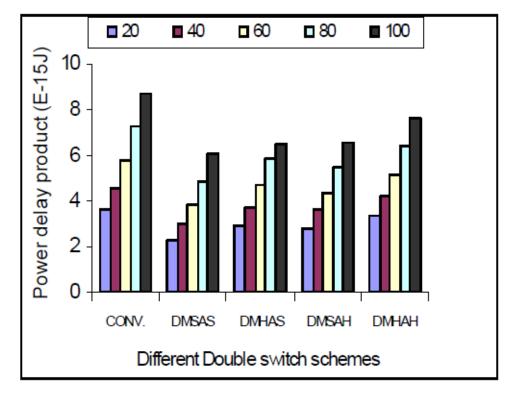

| Figure 3.6: PDP vs. double switch schemes                                                                                                                                                                                                                                                                                                                |                                 |

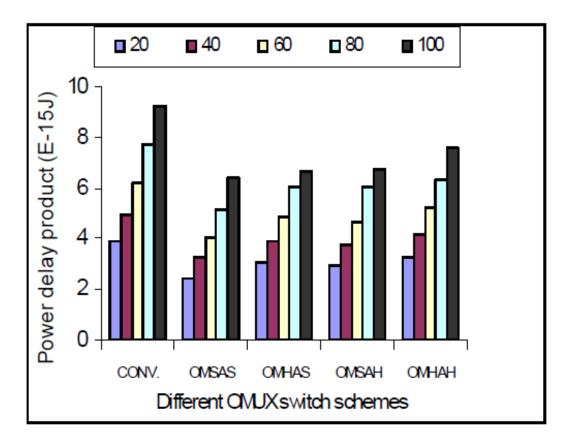

| Figure 3.7: PDP vs. OMUX switch schemes                                                                                                                                                                                                                                                                                                                  |                                 |

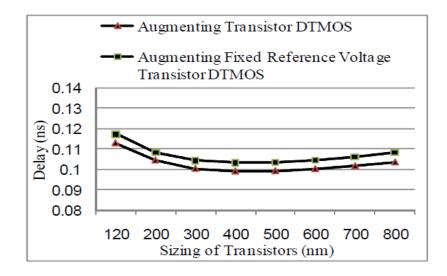

| Figure 3.8: Delay vs. size of Augmented and Augmented with fixed reference DTMC                                                                                                                                                                                                                                                                          |                                 |

|                                                                                                                                                                                                                                                                                                                                                          | .23                             |

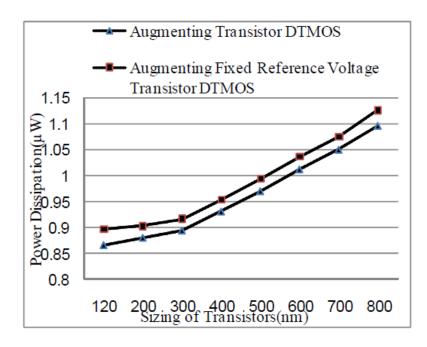

| Figure 3.9: Power vs. size of Augmented and Augmented with fixed reference DTM                                                                                                                                                                                                                                                                           |                                 |

|                                                                                                                                                                                                                                                                                                                                                          |                                 |

| Figure 3.10: PDP vs. size of Augmented and Augmented with fixed reference DTMC                                                                                                                                                                                                                                                                           | DS                              |

|                                                                                                                                                                                                                                                                                                                                                          |                                 |

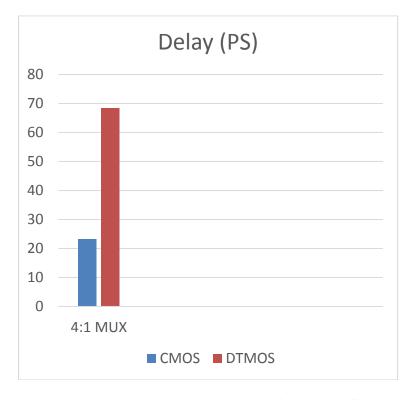

| Figure 3.11: 4-1 MUX delay DTMOS vs. CMOS                                                                                                                                                                                                                                                                                                                |                                 |

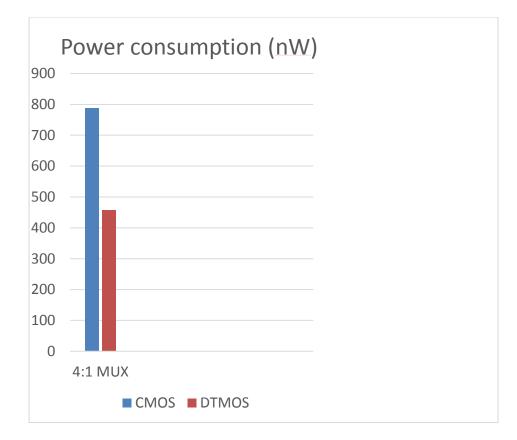

| Figure 3.12: 4-1 MUX power DTMOS vs. CMOS                                                                                                                                                                                                                                                                                                                |                                 |

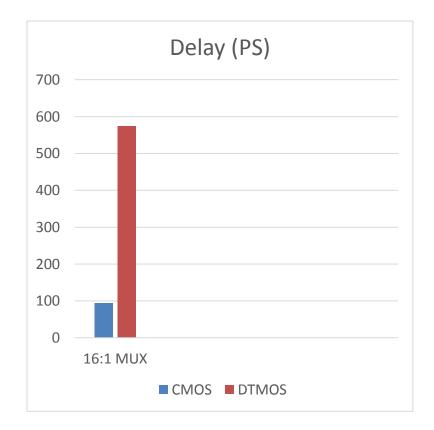

| Figure 3.13: 16-1 MUX delay DTMOS vs. CMOS                                                                                                                                                                                                                                                                                                               |                                 |

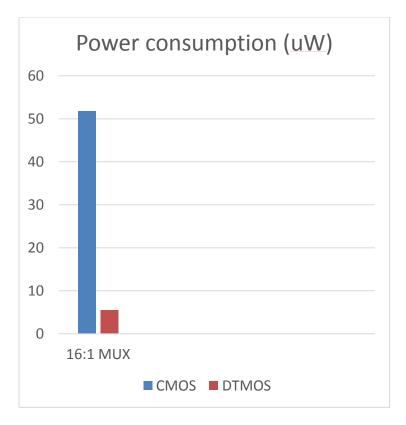

| Figure 3.14: 16-1 MUX power DTMOS vs. CMOS                                                                                                                                                                                                                                                                                                               |                                 |

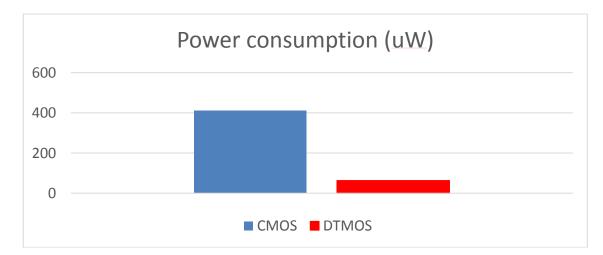

| Figure 3.15: CLB power DTMOS vs. CMOS                                                                                                                                                                                                                                                                                                                    |                                 |

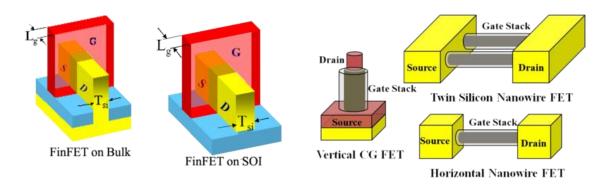

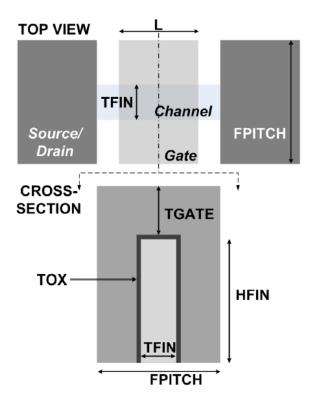

| Figure 3.16: Multi-gate transistors                                                                                                                                                                                                                                                                                                                      |                                 |

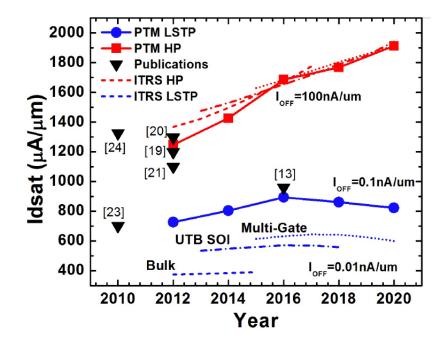

| Figure 3.17: Saturation current of PTM vs ITRS                                                                                                                                                                                                                                                                                                           |                                 |

|                                                                                                                                                                                                                                                                                                                                                          | .28                             |

| Figure 3.19: PTM models generation flow                                                                                                                                                                                                                                                                                                                  |                                 |

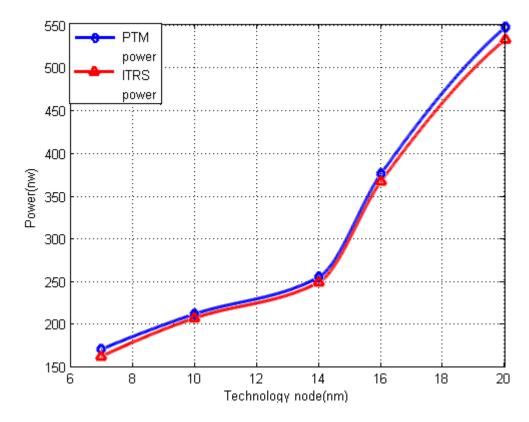

| Figure 3.20: The difference between ITRS off-current and PTM off-current impact o                                                                                                                                                                                                                                                                        |                                 |

| TG-FF power                                                                                                                                                                                                                                                                                                                                              |                                 |

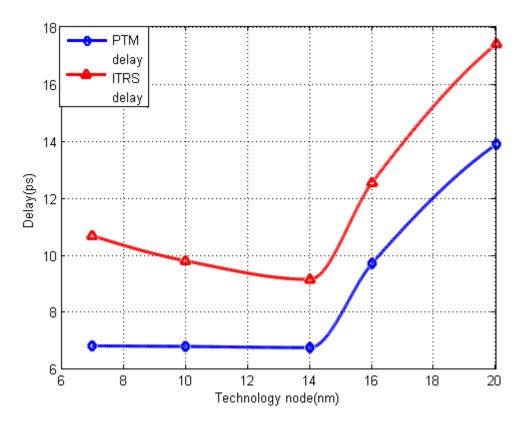

| Figure 3.21: The difference between ITRS off-current and PTM off-current impact o                                                                                                                                                                                                                                                                        |                                 |

| TG-FF delay                                                                                                                                                                                                                                                                                                                                              |                                 |

|                                                                                                                                                                                                                                                                                                                                                          |                                 |

|                                                                                                                                                                                                                                                                                                                                                          | n                               |

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o                                                                                                                                                                                                                                                                        |                                 |

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o TG-FF PDP.                                                                                                                                                                                                                                                             | .31                             |

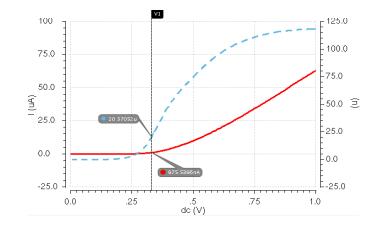

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o<br>TG-FF PDP<br>Figure 3.23: Extraction of Threshold voltage, the dashed line is the first derivative of                                                                                                                                                               | .31                             |

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o<br>TG-FF PDP<br>Figure 3.23: Extraction of Threshold voltage, the dashed line is the first derivative of<br>the drain current, the solid line is the drain current                                                                                                     | .31<br>.33                      |

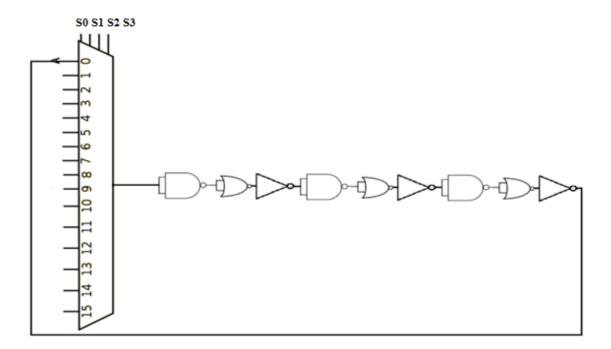

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o<br>TG-FF PDP<br>Figure 3.23: Extraction of Threshold voltage, the dashed line is the first derivative of<br>the drain current, the solid line is the drain current<br>Figure 3.24: Critical path simulation setup                                                      | .31<br>.33<br>.33               |

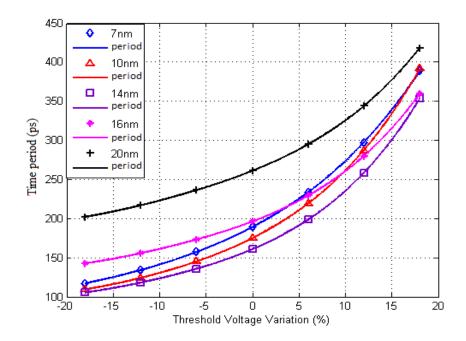

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o<br>TG-FF PDP<br>Figure 3.23: Extraction of Threshold voltage, the dashed line is the first derivative of<br>the drain current, the solid line is the drain current<br>Figure 3.24: Critical path simulation setup<br>Figure 3.25: RO time period vs. Threshold voltage | .31<br>.33<br>.33<br>.35        |

| Figure 3.22: The difference between ITRS off-current and PTM off-current impact o<br>TG-FF PDP<br>Figure 3.23: Extraction of Threshold voltage, the dashed line is the first derivative of<br>the drain current, the solid line is the drain current<br>Figure 3.24: Critical path simulation setup                                                      | .31<br>.33<br>.33<br>.35<br>.35 |

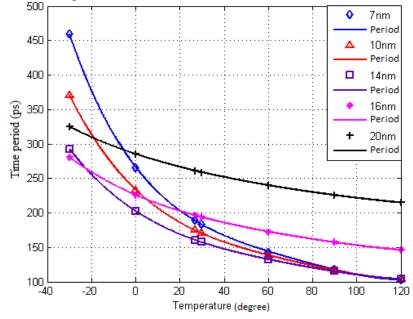

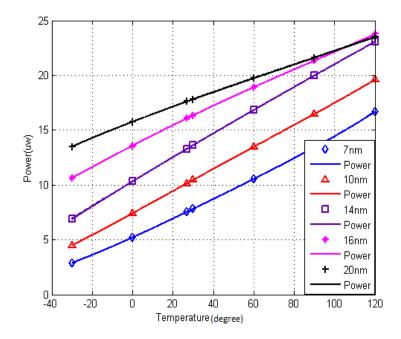

| Figure 3.28: RO power vs. Temperature                                               | .36 |

|-------------------------------------------------------------------------------------|-----|

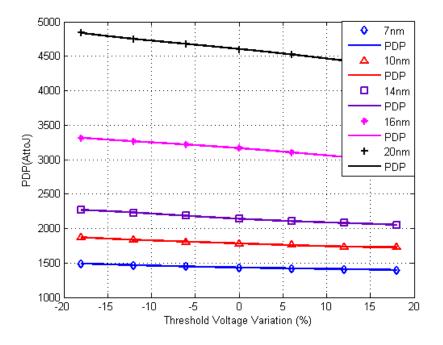

| Figure 3.29: RO PDP vs. Threshold voltage                                           |     |

| Figure 3.30: RO PDP vs. Temperature                                                 |     |

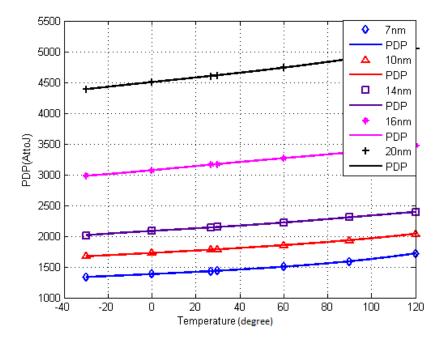

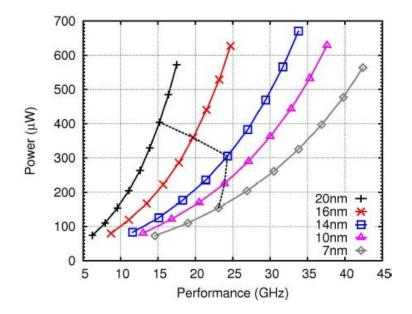

| Figure 3.31: PTM models power vs. performance                                       |     |

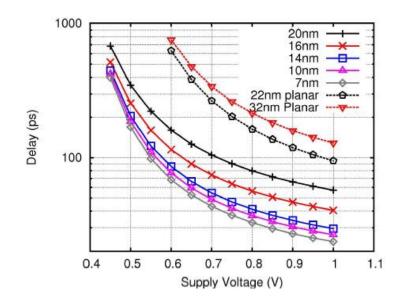

| Figure 3.32: PTM models delay vs. supply voltage                                    |     |

|                                                                                     |     |

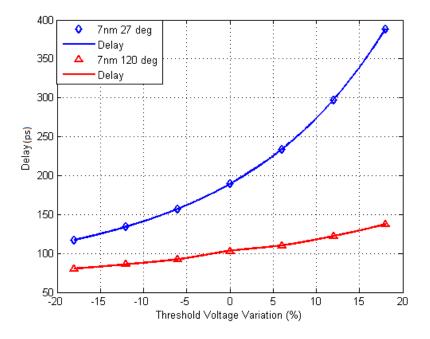

| Figure 3.33: 7nm delay vs. threshold voltage at 27° and at 120°                     |     |

|                                                                                     |     |

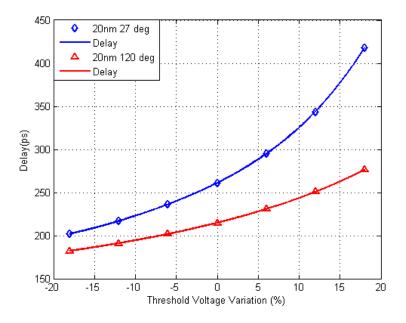

| Figure 3.34: 20nm delay vs. threshold voltage at 27° and at 120°                    |     |

|                                                                                     |     |

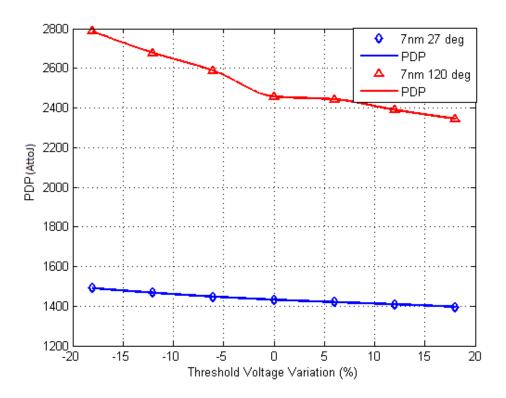

| Figure 3.35: 7nm PDP vs. threshold voltage at 27° and at 120°                       |     |

| Tigure 5.55. Timi TDT 15. une short totuge ut 27 une ut 120                         |     |

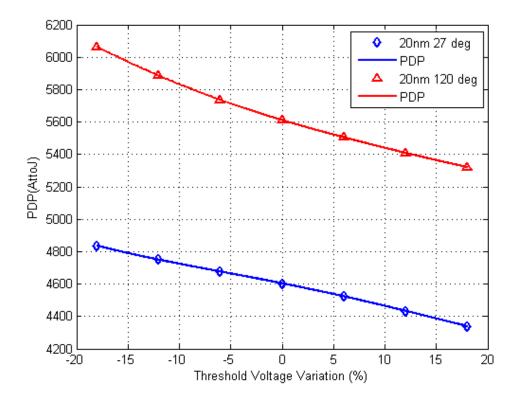

| Figure 3.36: 20nm PDP vs. threshold voltage at 27° and at 120°                      |     |

| right 9.50. 20mm PDF vs. uneshold voltage at 27 and at 120                          |     |

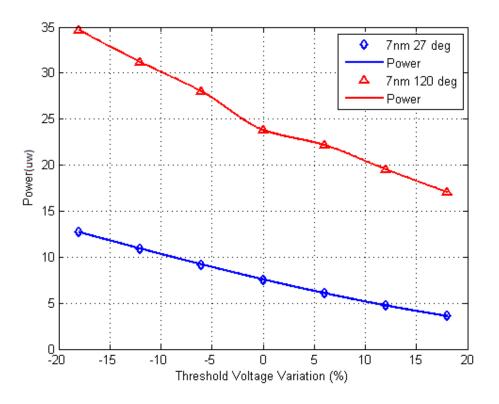

| Figure 3.37: 7nm power vs. threshold voltage at 27° and at 120°                     |     |

| rigure 5.57. This power vs. uneshold voltage at 27 and at 120                       |     |

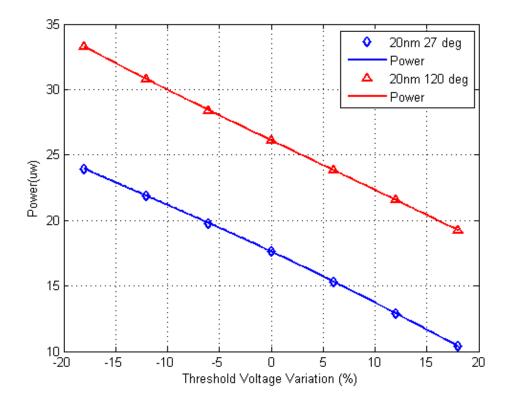

| Figure 3.38: 20nm power vs. threshold voltage at 27° and at 120°                    |     |

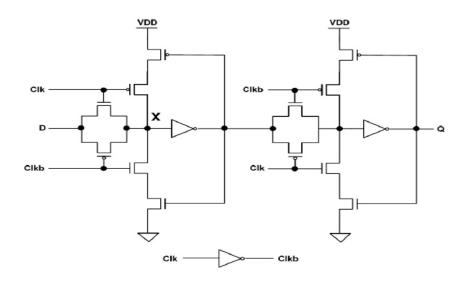

| Figure 3.39: Transmission gate Flip-Flop                                            | .41 |

|                                                                                     |     |

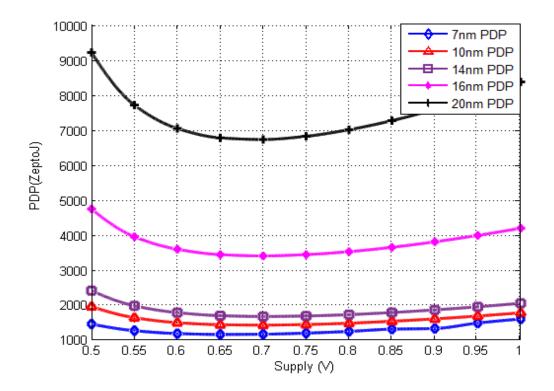

| Figure 3.40: TG-FF power delay product vs. supply voltage for 20nm to 7nm nodes.    |     |

| Figure 3.41: Sense Amplifier Flip-Flop                                              | .44 |

| Figure 3.42: SA-FF and SD-FF power delay product vs. supply voltage for 20nm to     | 11  |

| 7nm nodes (the solid lines are for SA-FF, and the dotted lines are for SD)          |     |

| Figure 3.43: Semi Dynamic Flip-Flop.                                                |     |

| Figure 3.44: TG-FF Delay vs. Threshold voltage                                      |     |

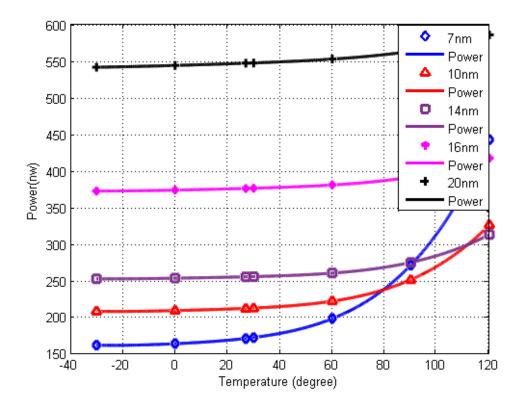

| Figure 3.45: TG-FF Delay vs. Temperature                                            |     |

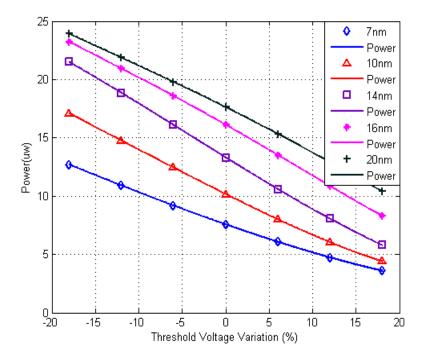

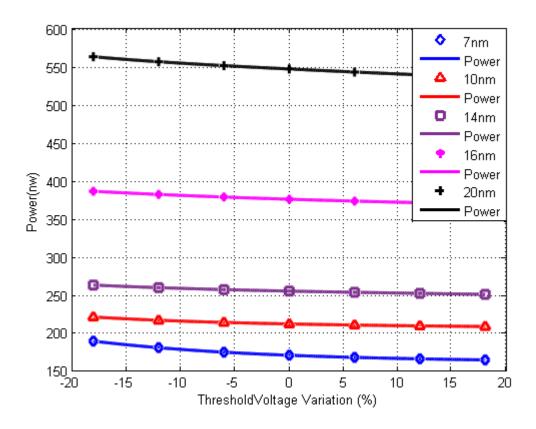

| Figure 3.46: TG-FF Power vs. Threshold voltage                                      |     |

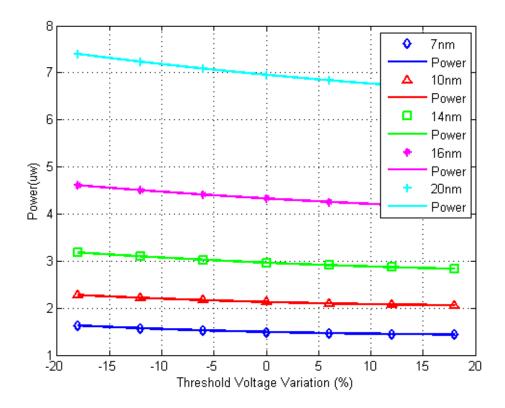

| Figure 3.47: TG-FF Power vs. Threshold voltage                                      |     |

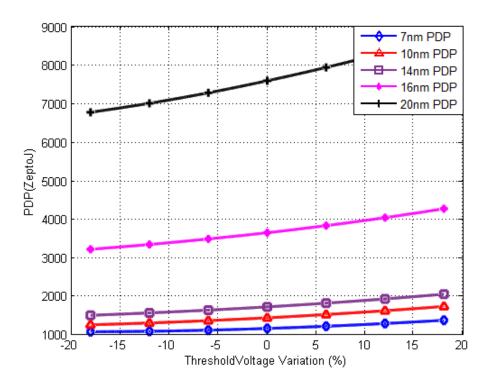

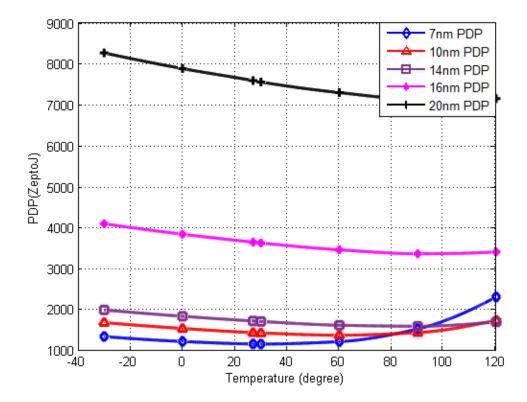

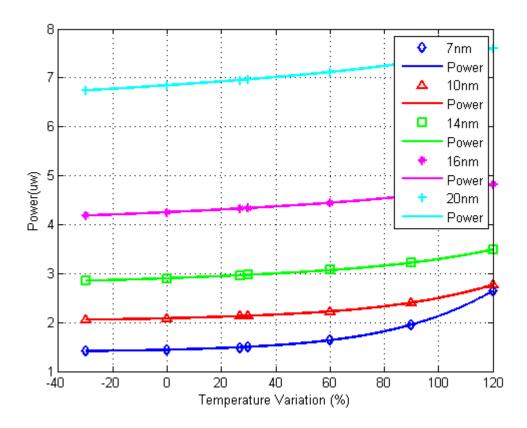

| Figure 3.48: TG-FF PDP vs. Threshold voltage                                        |     |

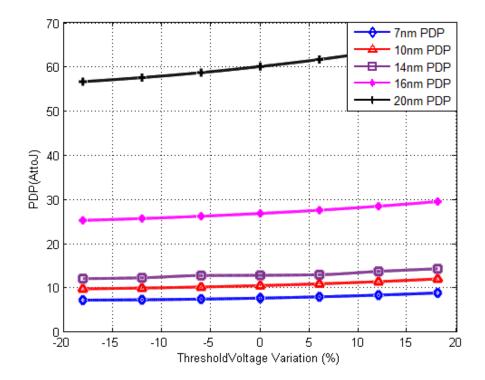

| Figure 3.49: TG-FF PDP vs. Temperature                                              |     |

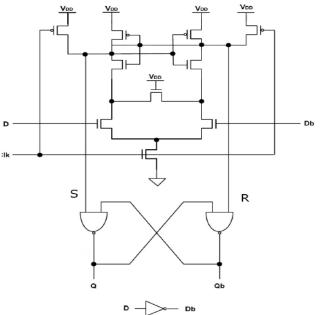

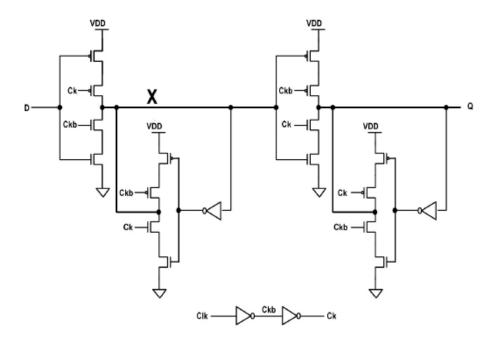

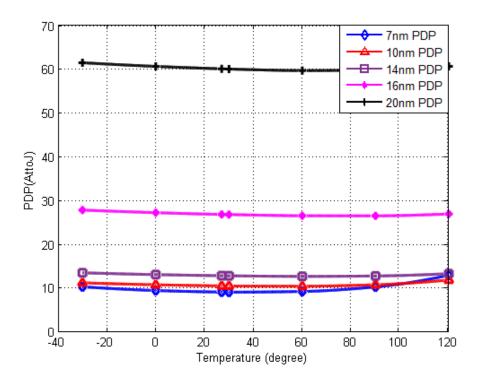

| Figure 3.50: Clocked CMOS flip-flop.                                                |     |

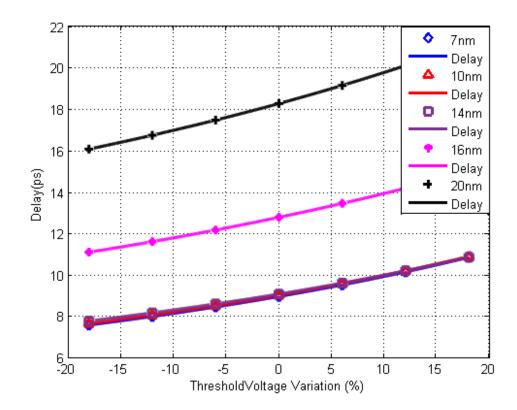

| Figure 3.51: C2MOS-FF Delay vs. Threshold voltage                                   |     |

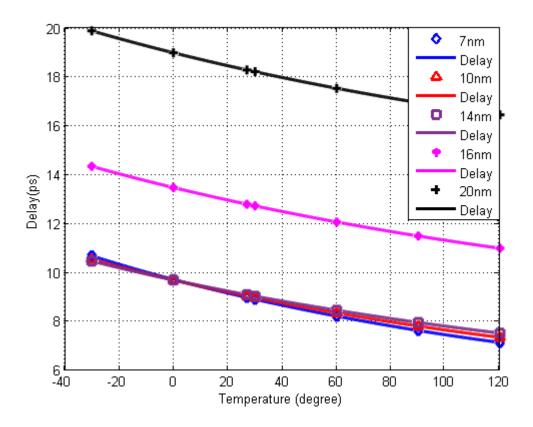

| Figure 3.52: C2MOS-FF Delay vs. Temperature                                         |     |

| Figure 3.53: C2MOS-FF Power vs. Threshold voltage                                   |     |

| Figure 3.54: C2MOS-FF Power vs. Temperature                                         |     |

| Figure 3.55: C2MOS-FF PDP vs. Threshold voltage                                     |     |

| Figure 3.56: C2MOS-FF PDP vs. Temperature                                           |     |

| Figure 3.57: SA-FF Delay vs. Threshold voltage                                      |     |

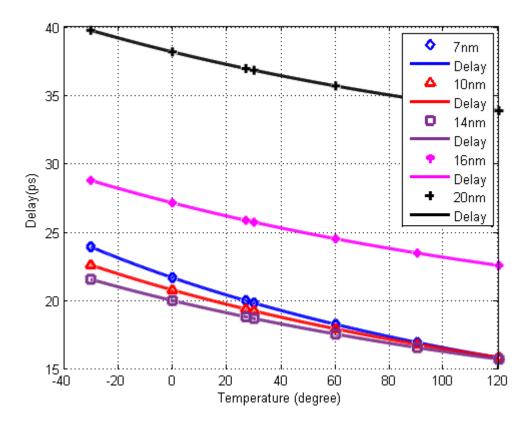

| Figure 3.58: SA-FF Delay vs. Temperature                                            |     |

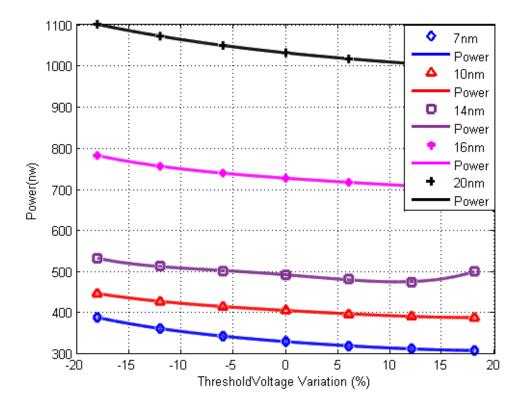

| Figure 3.59: SA-FF Power vs. Threshold voltage                                      |     |

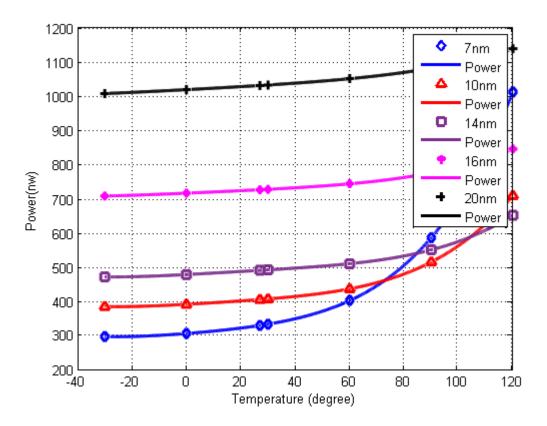

| Figure 3.60: SA-FF Power vs. Temperature                                            |     |

| Figure 3.61: SA-FF PDP vs. Threshold voltage                                        |     |

| Figure 3.62: SA-FF PDP vs. Temperature                                              |     |

| Figure 3.63: SD-FF Delay vs. Threshold voltage                                      |     |

| Figure 3.64: SD-FF Delay vs. Temperature                                            |     |

| Figure 3.65: SD-FF Power vs. Threshold voltage                                      | .58 |

| Figure 3.66: SD-FF Power vs. Temperature                                            | .59 |

| Figure 3.67: SD-FF PDP vs. Threshold voltage                                        | .59 |

| Figure 3.68: SD-FF PDP vs. Temperature                                              | .60 |

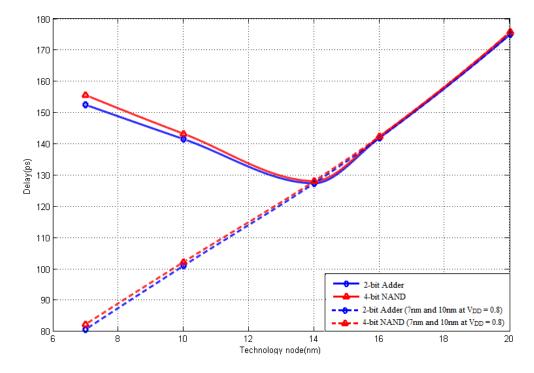

| Figure 3.69: Delay of 2-bit adder, and 4-bit NAND circuits for 20nm to 7nm nodes, t | he  |

| dashed line are for 7nm and 10nm at $V_{DD} = 0.8$                                  | .61 |

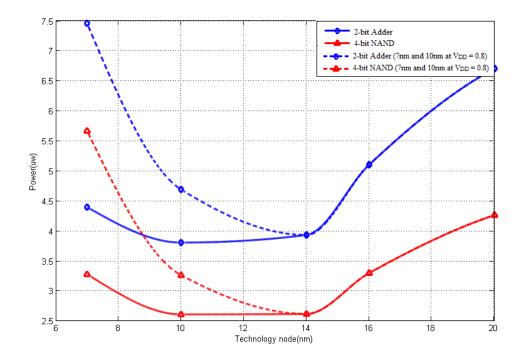

| Figure 3.70: Power consumption of 2-bit adder, and 4-bit NAND circuits for 20nm to     |

|----------------------------------------------------------------------------------------|

| 7nm nodes, the dashed line are for 7nm and 10nm at $V_{DD} = 0.8$                      |

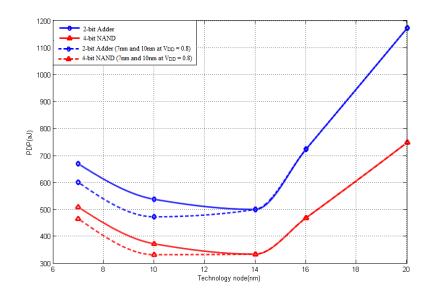

| Figure 3.71: PDP of 2-bit adder, and 4-bit NAND circuits for 20nm to 7nm nodes, the    |

| dashed line are for 7nm and 10nm at $V_{DD} = 0.8$                                     |

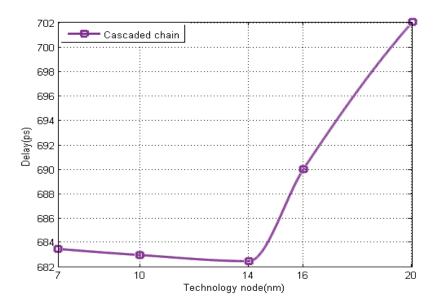

| Figure 3.72: Delay of cascaded chain circuit for 20nm to 7nm nodes                     |

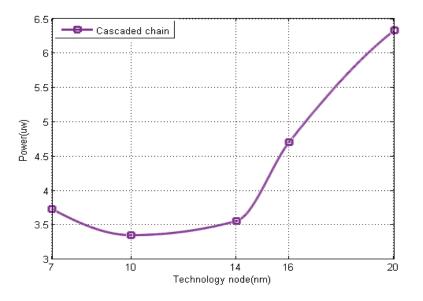

| Figure 3.73: Power consumption of cascaded chain circuit for 20nm to 7nm nodes64       |

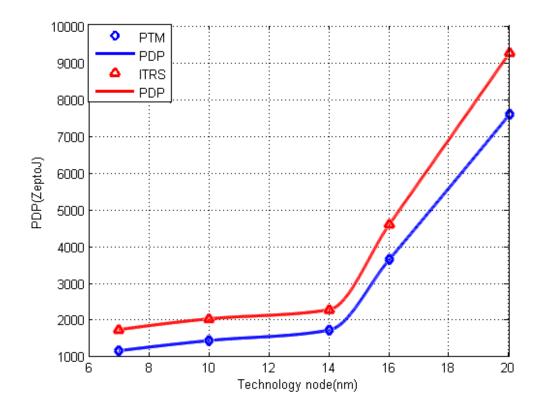

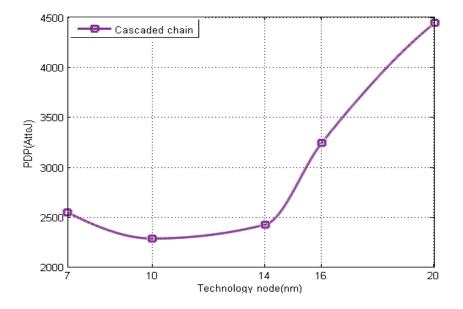

| Figure 3.74: PDP of cascaded chain circuit for 20nm to 7nm nodes                       |

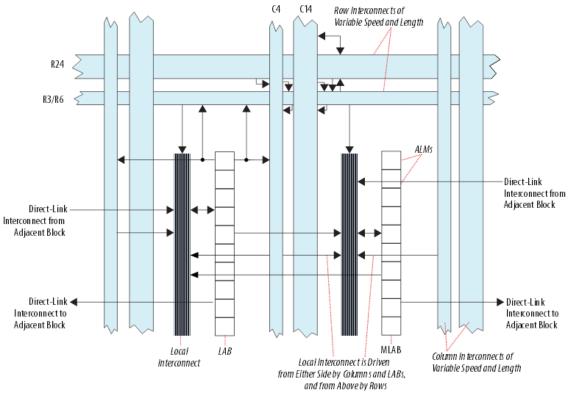

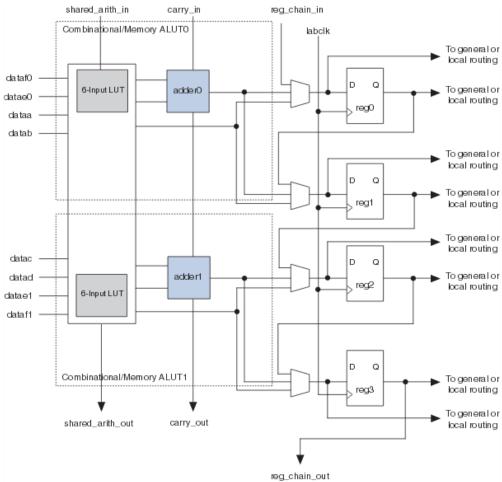

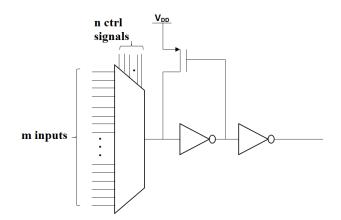

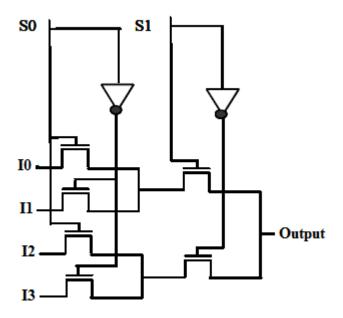

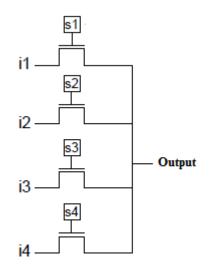

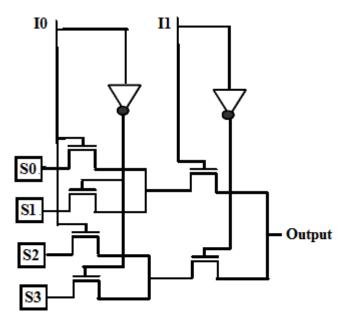

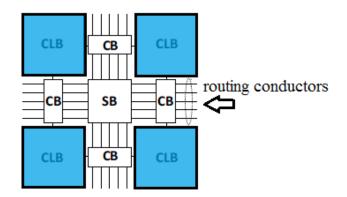

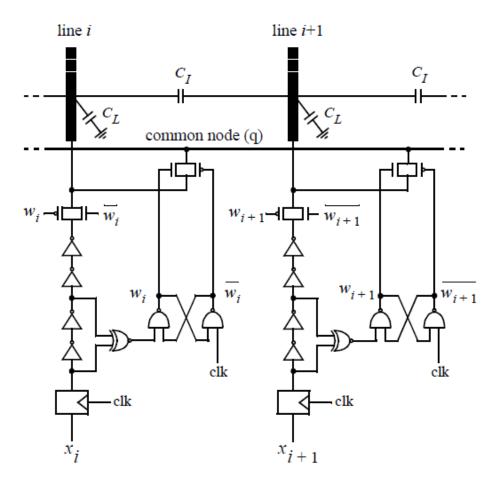

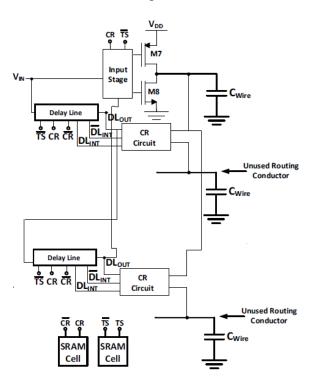

| Figure 4.1: FPGA circuits structures                                                   |

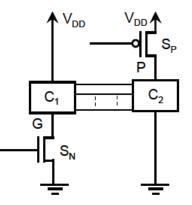

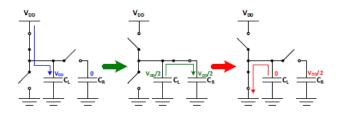

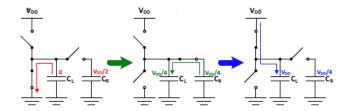

| Figure 4.2: Charge recycling in CMOS                                                   |

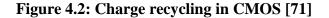

| Figure 4.3: Charge recycling CMOS circuit                                              |

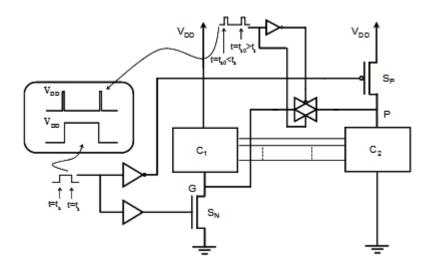

| Figure 4.4: Bus charge recycling                                                       |

| Figure 4.5: Bus charge recycling circuit                                               |

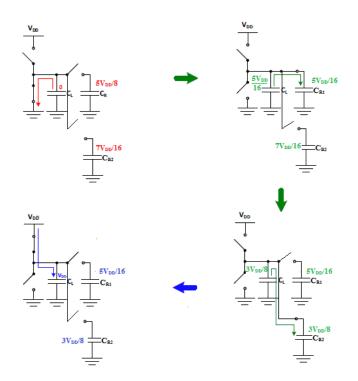

| Figure 4.6: FPGA charge recycling71                                                    |

| Figure 4.7: FPGA charge recycling second cycle                                         |

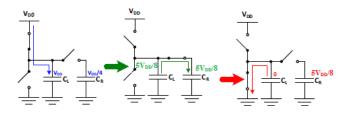

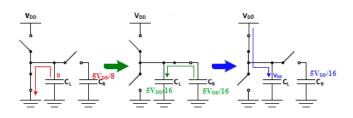

| Figure 4.8: Multiple charge recycling phases74                                         |

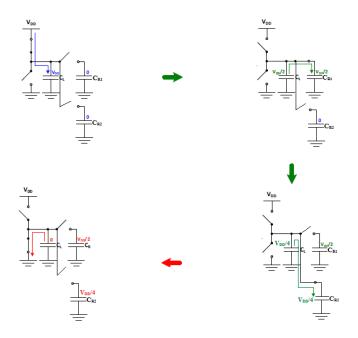

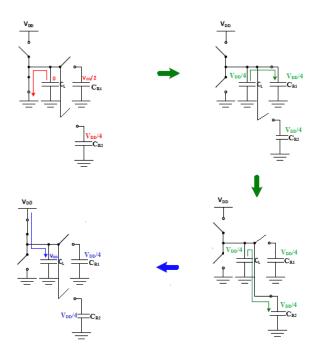

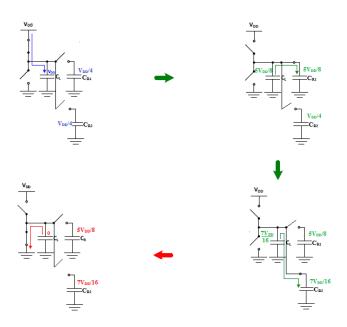

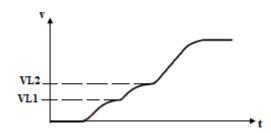

| Figure 4.9: Rising and falling signals in multiple CR75                                |

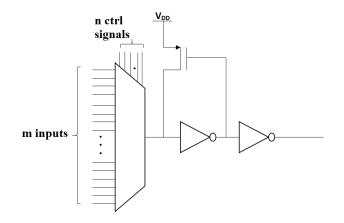

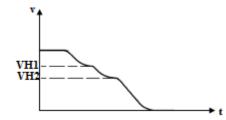

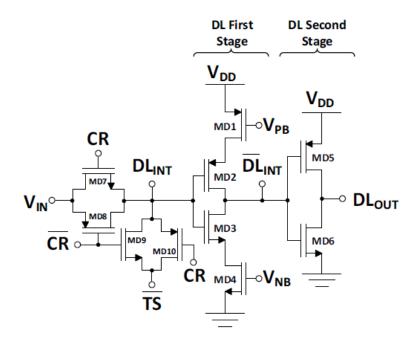

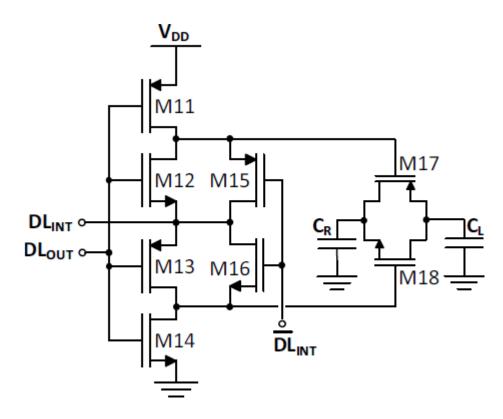

| Figure 4.10: CR buffer circuit                                                         |

| Figure 4.11: The proposed multiple CR buffer                                           |

| Figure 4.12: CR delay line77                                                           |

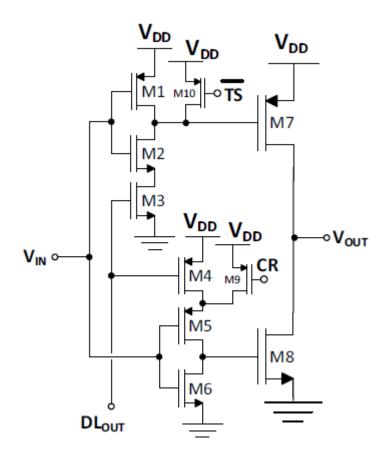

| Figure 4.13: CR input stage78                                                          |

| Figure 4.14: CR charge recycling sub-circuit                                           |

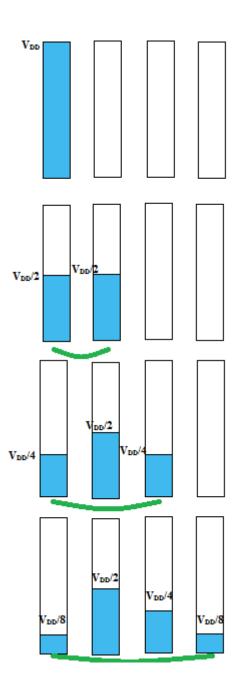

| Figure 4.15: Multiple charge recycling idea                                            |

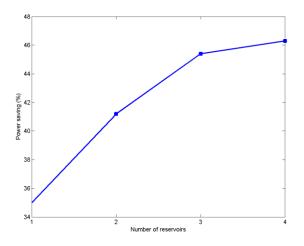

| Figure 4.16: Ideal multiple charge recycling power saving                              |

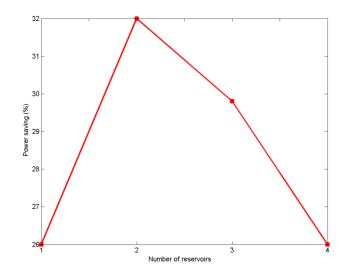

| Figure 4.17: Actual multiple charge recycling power saving                             |

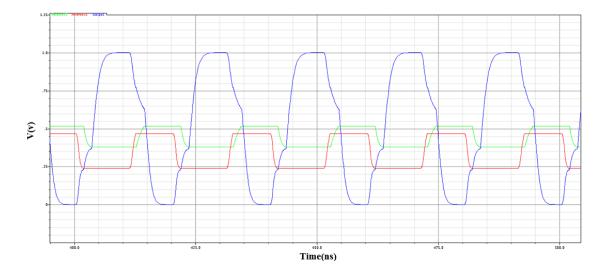

| Figure 4.18: SPICE simulation waveforms of output and reservoirs. Blue for output, red |

| for the first reservoir, and green for the second reservoir                            |

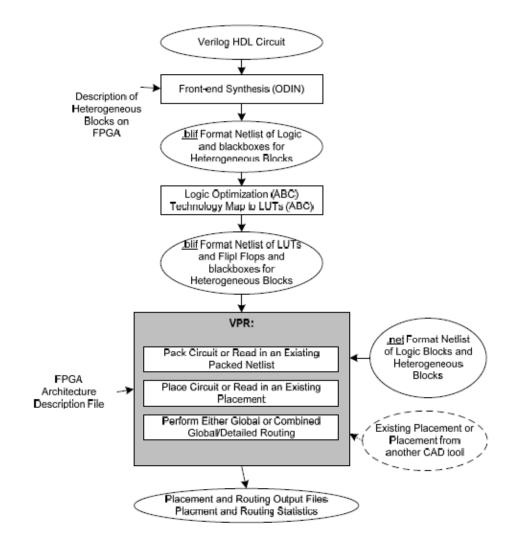

| Figure A.1: VTR workflow                                                               |

|                                                                                        |

## Abstract

Field-Programmable Gate Arrays (FPGAs) have become one of the key digital circuit implementation media over last decades. The importance of FPGAs comes from their architecture, which consists of programmable logic functionality blocks and programmable interconnects. This nature of FPGA has a terrific impact on the quality of the final product's performance, area, and power consumption. There are many techniques to make FPGAs more energy efficient. The different techniques can be categorized to: device, circuit, system, architecture, and computer-aided design (CAD). Device techniques refer to the usage of new emerging low-power process technologies offered by the semiconductor manufacturers, and new devices materials and structures. Circuit techniques refer to transistor level implementations of logic and routing resources. System techniques refer to high level techniques such as dynamic voltage and frequency control, power gating for unused resources, and dynamic reconfiguration. Architecture techniques refer to functionality of logic blocks, memory, and I/Os resources and the connectivity between these resources. Finally, CAD techniques refer to improvements added to the tools used to configure FPGAs to consider power consumption. In this work, we target introducing new design techniques to lower FPGAs power at device and circuit levels.

First, we studied using dynamic threshold MOSFET (DTMOS) in FPGA logic blocks and showed that DTMOS can be used as a good candidate for designing ultralow power FPGAs. The study also covered DTMOS MUXs as MUXs are the main part in FPGA routing fabric.

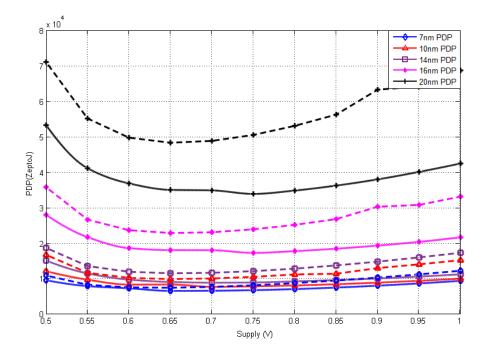

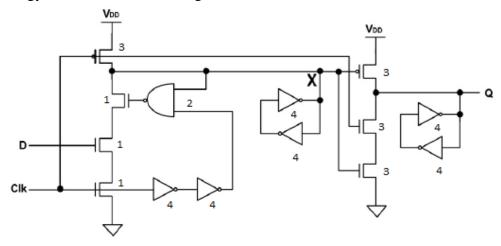

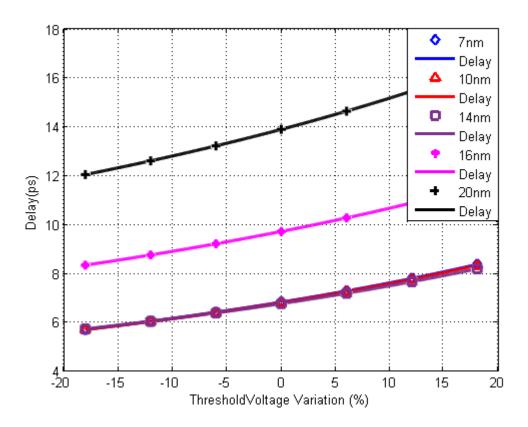

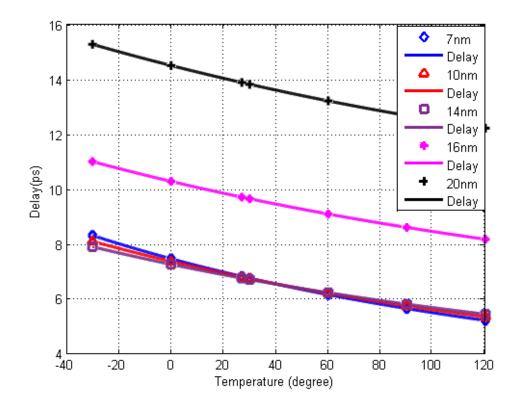

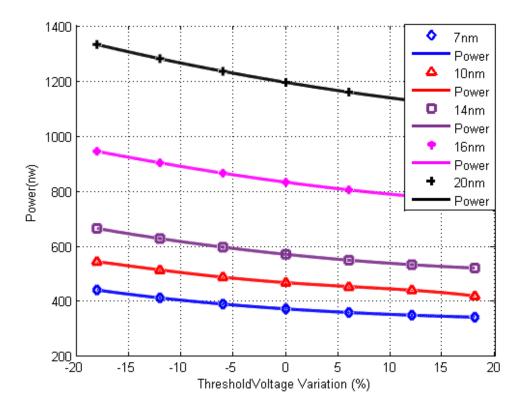

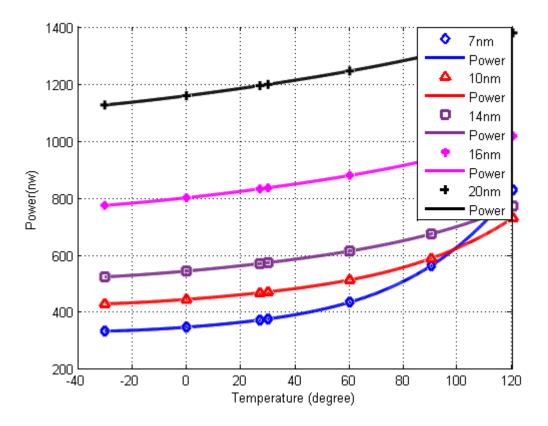

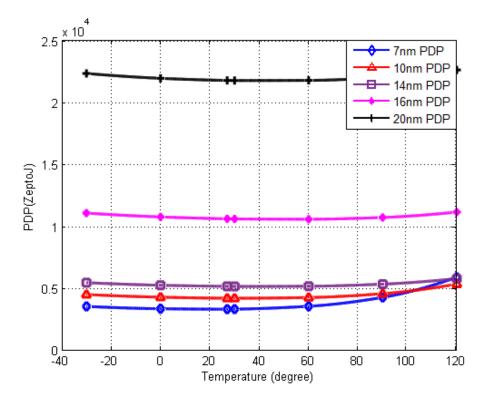

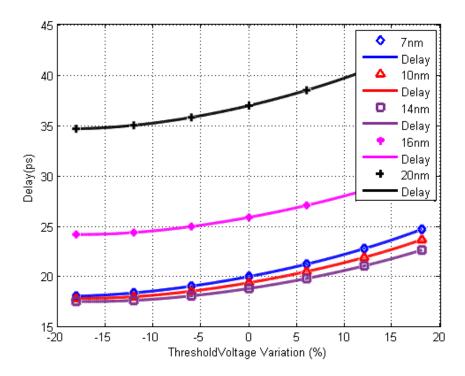

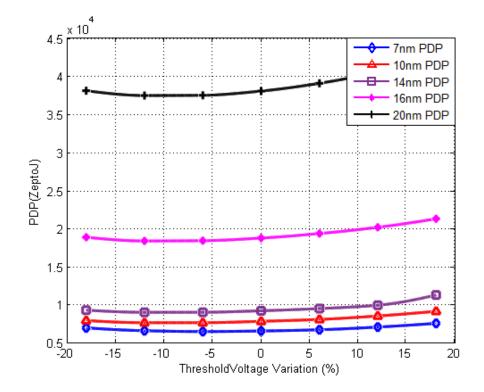

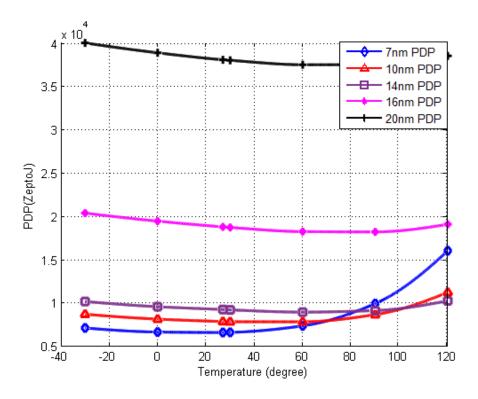

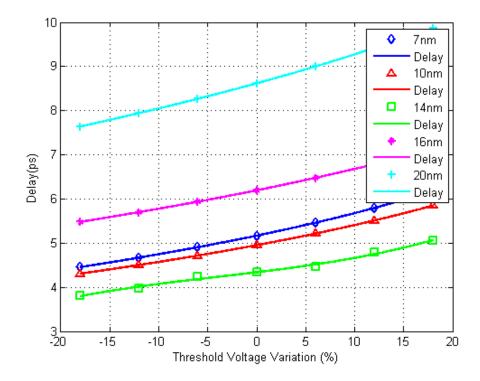

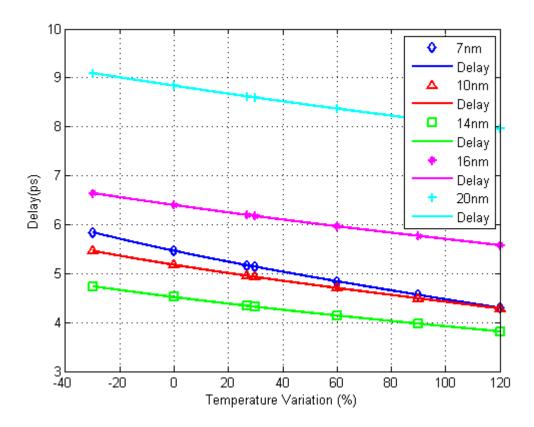

Following that, we studied the implementation of FPGA using FinFET instead of CMOS to explore future technologies impact on FPGAs energy, also environmental variations are covered in the study since the variations in nanoscale technologies cannot be neglected. We used predictive technology models (PTM model cards) for 20nm down to 7nm technologies to explore performance, power, and energy of FPGA components at each technology node and the impact of variations on the trends of these metrics, We also obtained the optimum supply voltage from the energy point of view for a variety of flip-flops topologies which can be used in today's FPGAs at each technology node. We evaluated FPGA cluster metrics using SPICE simulations based on three benchmark circuits: 2-bit adder, 4-bit NAND, and cascaded chain.