Design of High Speed Optical Communication Access Networks with Optical On-Chip Network FPGA (OOCN-FPGA) Integration

Funded by National Telecom Regulatory Authority (NTRA)

-

Project Duration: August 2014 – July 2016 (24 months)

-

Project Budget: EGP1.5 Million

-

Project Industrial Partners: Fujitsu Research Labs, USA

-

Project Executive Summary:

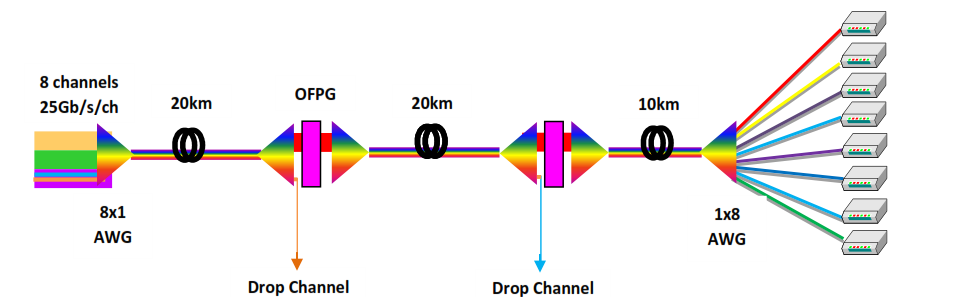

The main objective of this research project is to improve the performance of the optical communication access networks by increasing the transmission rate and the transmission distance. In addition, Wavelength Division Multiplexing (WDM) will be applied to the optical communication networks to increase the transmission rate more than 200GB/s over 8 WDM multiplexed channels. This objective is achieved by inserting an Optical Clock and Data Recovery (OCDR) unit, in the optical link.

The implementation of the OCDR will be performed, for the first time, by using the Field Programmable Gate Array (FPGA). In this research project, we will design a new optical compatible FPGA chip that exhibits Optical On-Chip Network (OOCN) in addition to the optical I/O pins. The OOCN will reduce the interconnect power and speed overheads and will get all the benefits of the optical link speed inside the FPGA chip. The new OOCN-FPGA chip will have new sneak path design that allows the optical I/O pins to access the OOCN directly without converting the optical signal into the electrical domain. This sneak path design will improve the speed of the OOCN-FPGA significantly.

-

Project Team:

-

Project Published Journal Papers:

- “Dual Split-Merge: A High Throughput Router Architecture for FPGAs”, Elsevier Microelectronics Journal, vol. 81, pp. 51-57, 2018.

- “Optimizing FPGA-based Hard Networks-on-Chip by Minimizing and Sharing Resources”, Elsevier Integration VLSI Journal, vol. 63, pp. 138-147, 2018.

- “NoC-DPR: A New Simulation Tool Exploiting the Dynamic Partial Reconfiguration (DPR) on Network-on-Chip (NoC) Based FPGA”, Elsevier Integration VLSI Journal, vol. 63, pp. 204-212, 2018.

- “Technology Scaling Roadmap for FinFET-Based FPGA Clusters Under Process Variations”, Journal of Circuits, Systems, and Computers, vol. 27, issue 4, pp. (1850056)1-32, 2018.

- “Electrical and Optical Clock and Data Recovery in Optical Access Networks: A Comparative Study”, International Journal of Communication Systems, pp. 1-10, 2016.

-

Project Published Conference Papers:

- M. Shehata, and H. Mostafa, “A Single Wavelength Photonic Network on Chip Design Based on Optical Orthogonal Codes”, IEEE International Symposium on Circuits and Systems (ISCAS 2018), Florence, Italy, pp. 1-4, 2018.[PDF]

- R. Ali, H. Mostafa, and A. Hussein, “Impact of Dynamic Partial Reconfiguration on CONNECT Network-on-Chip for FPGAs”, IEEE International Conference on Design and Technology of Integrated Systems in Nanoscale Era (DTIS 2018), Taormina, Italy, pp. 1-5, 2018. [PDF]

- M. Shaheen, H. A. H. Fahmy, and H. Mostafa, “Modified Connect: New Bufferless Router for NoC-Based FPGAs”, IEEE International Midwest Symposium on Circuits and Systems (MWSCAS 2018), Windsor, Ontario, Canada, pp. 424-427, 2018. [PDF]

- M. Beheiry, H. Mostafa, Y. Ismail, and A. M. Soliman, “3D-NOCET: A Tool for Implementing 3D-NoCs Based on the Direct-Elevator Algorithm”, International Symposium on Quality Electronic Design (ISQED 2017)), Santa Clara, California, USA, pp. 144-148, 2017. [PDF]

- A. Salaheldin, H. Mostafa, and A. M. Soliman, “A CODEC, Tiles to NoC Router Interface, for Next Generation FPGAs with Embedded NoCs”, IEEE International Midwest Symposium on Circuits and Systems (MWSCAS 2017), Boston, MA, USA, pp. 1228-1231, 2017. [PDF]

- A. K. ELdin, I. Ahmed, A. Obeid, A. Shalash, Y. Ismail, and H. Mostafa, “A Cost-Effective Dynamic Partial Reconfiguration Implementation Flow for Xilinx FPGA”, IEEE International NEW Generation of Circuits and Systems (NGCAS 2017), Genova, Italy, pp. 281-284, 2017. [PDF]

- A. Hassan, H. A. H. Fahmy, Y. Ismail, and H. Mostafa, “Exploiting the Dynamic Partial Reconfigurtion on NoC-Based FPGA”, IEEE International NEW Generation of Circuits and Systems (NGCAS 2017), Genova, Italy, pp. 277-280, 2017.[PDF]

- A. Hassan, H. A. H. Fahmy, Y. Ismail, and H. Mostafa, “Exploiting the Dynamic Partial Reconfigurtion on NoC-Based FPGA”, IEEE International NEW Generation of Circuits and Systems (NGCAS 2017), Genova, Italy, pp. 277-280, 2017.[PDF]

- K. Ismail, T. Ismail, Y. Ismail, and H. Mostafa, “Design and Implementation of CDR and SerDes for High-speed Optical Communication Networks using FPGA”, IEEE International Conference on Transparent Optical Networks (ICTON 2016), Trento, Italy, pp. 1-3, 2016. [PDF]

- N. Gamal, H. Fahmy, Y. Ismail, and H. Mostafa, “Design Guidelines for Embedded NoCs on FPGAs”, IEEE International Conference on Quality Electronic Design (ISQED 2016), Santa Clara, California, USA, pp. 69-74, 2016. [PDF]

- N. Gamal, H. A. H. Fahmy, Y. Ismail, T. Ismail, M. Mohie-Eldin, and H. Mostafa, “Design Guidelines for Soft Implementations to Embedded NoCs of FPGAs”, International Design and Test Symposium (IDT 2016), Hammamet, Tunisia, pp. 37-42, 2016. [PDF]

- M. Beheiry, A. Aly, H. Mostafa, and A. M. Soliman, “Direct-Elevator: A Modified Routing Algorithm for 3D-NoCs”, IEEE International Conference on Microelectronics (ICM 2015), Casablanca, Morocco, pp. 1-4, 2015. [PDF]

- K. Helal, S. Attia, T. Ismail, and H. Mostafa, “Comparative Review of NOCs in the Context of ASICs and FPGAs”, IEEE International Symposium on Circuits and Systems (ISCAS 2015), Lisbon, Portugal, pp. 1866-1869, 2015. [PDF]

- K. Helal, S. Attia, T. Ismail, and H. Mostafa, “Priority-Select Arbiter: An Efficient Round-Robin Arbiter”, IEEE International Conference on NEW Circuits and Systems (NEWCAS 2015), Grenoble, France, pp. 1-4, 2015.[PDF]

- A. Salaheldin, K. Abdallah, N. Gamal, and H. Mostafa, “Review of NoC-Based FPGAs Architectures”, IEEE International Conference on Energy Aware Computing Systems and Applications (ICEAC 2015), Cairo Egypt, pp. 1-4, 2015. [PDF]

- Y. Elsayed, A. Wageeh, T. Ismail, and H. Mostafa, “All-Optical Clock and Data Recovery using Self-Pulsating Lasers for High-Speed Optical Networks”, IEEE International Conference on Energy-Aware Computing Systems and Applications (ICEAC 2015), Cairo Egypt (Best Paper Award), pp. 1-3, 2015. [PDF]

- Y. Elsayed, A. Wageeh, T. Ismail, and H. Mostafa, “All-Optical Clock and Data Recovery using Self-Pulsating Lasers for High-Speed Optical Networks”, IEEE International Conference on Energy-Aware Computing Systems and Applications (ICEAC 2015), Cairo Egypt (Best Paper Award), pp. 1-3, 2015. [PDF]

- Y. El-Sayed, T. Ismail, and H. Mostafa, “A Wide FBG-Based Optical Clock and Data Recovery for Optical Access Networks”, International Conference on Transparent Optical Networks (ICTON 2015), Budapest, Hungary, pp. 1-4, 2015. [PDF]

- T. Ismail, H. Mostafa, and Y. Ismail, “Performance Evaluation of Wavelength Exchanging in WDM Optical Crossbar”, IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2015), Cairo Egypt, pp. 681-684, 2015. [PDF]