# LOW POWER, SMALL AREA ALL DIGITAL PHASE LOCKED LOOP (ADPLL)

By

Ammar Mohammad Ibrahim

Ammar Mohammad Hussein

Mohammad Abdel-Lateef Abdel-Tawab

# A thesis submitted in partial fulfillment of the requirements for the degree of

Bachelor of Science in Electronics and Electrical Communications Department, Faculty of Engineering

Cairo University

Supervised by Dr. Hassan Mostafa

July, 2014

#### ABSTRACT

### ADPLL

The objective of the thesis is to design an All Digital Phase Locked Loop (ADPLL) with low power. The design consists of three main blocks: Digitally Controlled Oscillator (DCO), Phase Detector (PD) and Loop Filter (LF). The DCO is considered as the heart of the ADPLL as it consumes the most power for the whole system. The design went through two different approaches, standard cells and custom cells .This design can be used in Clock and Data Recovery (CDR) system as an application.

This thesis presents a low power all digital phase locked loop (ADPLL) in 65 nm CMOS process with 1.2 V power supply. It operates in the frequency range of 100 - 300 MHz. The ADPLL uses a digitally controlled oscillator with two stages, fine tuning stage and coarse tuning stage. The source of oscillation for this DCO is the ring oscillator.

The proposed ADPLL uses also a phase-frequency detector (PFD) and shift registers for the loop filter. It achieved power consumption at 200 MHz of 0.6 mW and a lock time of 1 uS.

The last design step of the ADPLL is the layout, some modification applied to the layout to satisfy the required specifications, at the end of this thesis a comparison between the required and the achieved specifications in schematic and layout level.

Design considerations of the ADPLL circuit components and implementation using Cadence, Synopsys and Mentor tools are presented; the AMS tool is used frequently in the standard cells flow.

# TABLE OF CONTENTS

| List of Figures                                                |    |

|----------------------------------------------------------------|----|

| Acknowledgments                                                |    |

| Acronyms                                                       |    |

| Chapter 1: Introduction                                        | 1  |

| Chapter 2: Custom Cells Approach                               | 5  |

| 2.1 DCO                                                        |    |

| 2.1.1 Ring Oscillator                                          | 6  |

| 2.1.2 Fine stage                                               | 11 |

| 2.1.3 Coarse stage                                             |    |

| 2.1.4 Conclusion and final results                             |    |

| 2.2 PFD                                                        | 24 |

| 2.3 Loop Filter                                                |    |

| 2.4 Overall Design                                             |    |

| 2.4.1 Extreme Reference Frequency                              |    |

| 2.4.2 Intermediate Reference Frequency                         |    |

| 2.4.3 Frequency step response                                  |    |

| 2.4.4 Jitter calculation                                       |    |

| Chapter 3: Standard Cells Approach                             |    |

| 3.1 PFD                                                        |    |

| 3.2 Loop Filter                                                |    |

| 3.3 PFD and Loop Filter                                        |    |

| 3.3 Overall Design                                             |    |

| Chapter 4: Layout                                              |    |

| 4.1 DCO                                                        |    |

| 4.1.1 DCV                                                      |    |

| 4.1.2 DCV2                                                     |    |

| 4.1.3 Ring Oscillator                                          | 45 |

| 4.1.4 Complete DCO                                             |    |

| 4.2 PFD                                                        |    |

| 4.3 Loop Filter                                                |    |

| 4.4 Overall Design                                             |    |

| 4.5 Conclusion                                                 | 51 |

| References                                                     |    |

| Appendix A: AMS Tutorial                                       | 53 |

| Appendix B: Logic Synthesis                                    |    |

| Appendix C: Importing Synthesized Design into Cadence Composer |    |

| Appendix D: Standard Cell Placement and Routing                |    |

| Appendix E: Power Calculation                                  |    |

|                                                                |    |

# LIST OF FIGURES

| Figure 1.1: Block diagram of the PLL                                       | 1  |

|----------------------------------------------------------------------------|----|

| Figure 1.2: The Overall block diagram of the ADPLL                         | 2  |

| Figure 1.3: Jitter Illustration                                            |    |

| Figure 2.1: DCO symbol view                                                | 5  |

| Figure 2.2: DCO internal structure                                         | 6  |

| Figure 2.3: Ring oscillator block diagram                                  | 6  |

| Figure 2.4: A Schematic view for the inverter                              | 7  |

| Figure 2.5: Simulation results of the inverter                             |    |

| Figure 2.6: Simulation results for the ring oscillator without delay cells |    |

| Figure 2.7: A schematic view of the HDC                                    | 9  |

| Figure 2.8: The ring oscillator with HDC cells                             |    |

| Figure 2.9: Simulation results for the ring oscillator with HDC cells      | 10 |

| Figure 2.10: A schematic view for the DCV cell                             | 11 |

| Figure 2.11: The gate capacitance of NAND gate                             | 12 |

| Figure 2.12: Simulation results for the NAND based DCV Cell                | 13 |

| Figure 2.13: A block diagram for the DCV building block                    | 13 |

| Figure 2.14: DCV array internal structure                                  |    |

| Figure 2.15: A symbol view for the DCV array                               | 15 |

| Figure 2.16: Period step Vs. frequency steps                               | 16 |

| Figure 2.17: A schematic view for the DCV2 cell                            | 17 |

| Figure 2.18: DCV2 block                                                    |    |

| Figure 2.19: DCV2 array                                                    | 19 |

| Figure 2.20: A symbol view for the DCV2 array                              | 20 |

| Figure 2.21: Different output periods of the DCO                           | 21 |

| Figure 2.22: Different output waveforms of the DCO                         | 22 |

| Figure 2.23: Period steps versus code                                      | 22 |

| Figure 2.24: Frequency steps versus code                                   | 23 |

| Figure 2.25: PFD schematic                                                 | 24 |

| Figure 2.26: State diagram of the PFD                                      | 25 |

| Figure 2.27: PFD simulation results                                        | 25 |

| Figure 2.28: Digital control signals used to switch a set of varactors     | 26 |

| Figure 2.29: Schematic view of the shift register                          | 27 |

| Figure 2.30: Reference = 100MHz                                            |    |

| Figure 2.31: DCO delay                                                     |    |

| Figure 2.32: Reference= 250MHz                                             | 29 |

| Figure 2.33: Effect of using counter                                       |    |

| Figure 2.34: Frequency counter                                             | 31 |

| Figure 2.35: frequency step response                                       | 32 |

| Figure 2.36: Eliminating the oscillations                                  |    |

| Figure 2.37: Eye-diagram of the ADPLL                                      |    |

| Figure 3.1: PFD schematic                                                  |    |

| Figure 3.2: Loop Filter schematic                                          |    |

| Figure 3.3: PFD and Loop Filter                                            |    |

| Figure 3.4: Overall ADPLL (standard cells)                                 |    |

|                                                                            |    |

| Figure 3.5: AMS of the overall ADPLL without the counter                 |    |

|--------------------------------------------------------------------------|----|

| Figure 3.6: AMS simulation of the overall ADPLL with counter             |    |

| Figure 3.7: AMS of the ADPLL with counter                                |    |

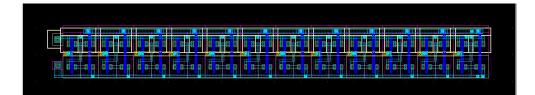

| Figure 3.8: The standard cells of both PFD and Loop Filter               | 41 |

| Figure 3.9: The transistor level of the standard D flip flop in cadence. |    |

| Figure 4.1: DCV layout                                                   |    |

| Figure 4. 2: DCV block layout                                            |    |

| Figure 4. 3: DCV array layout                                            |    |

| Figure 4. 4: DCV2 layout                                                 | 44 |

| Figure 4. 5: DCV2 block layout                                           | 45 |

| Figure 4. 6: DCV2 array layout                                           | 45 |

| Figure 4. 7: Ring Oscillator layout                                      | 45 |

| Figure 4. 8: Final DCO layout                                            |    |

| Figure 4. 9: DCO operating range in layout                               | 47 |

| Figure 4. 10: PFD layout                                                 | 47 |

| Figure 4.11: PFD pre-layout simulation                                   |    |

| Figure 4.12: PFD post-layout simulation                                  |    |

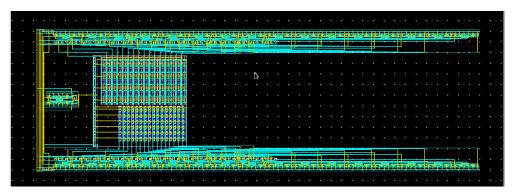

| Figure 3.13: Shift Register layout                                       | 49 |

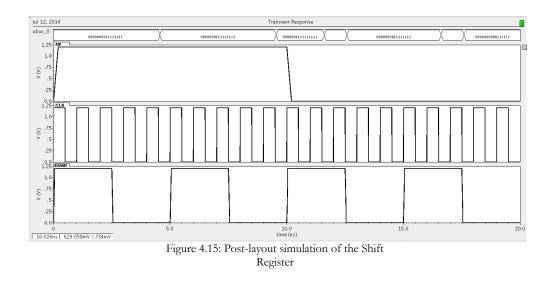

| Figure 4.14: Pre-layout simulation of the Shift Register                 | 49 |

| Figure 4.15: Post-layout simulation of the Shift Register                |    |

| Figure 4.16: The overall layout                                          |    |

| Figure 4.17: Overall post layout simulation                              |    |

## ACKNOWLEDGMENTS

First of all we would like to thank ALLAH for his mercy supporting us through this project. We wish to express sincere appreciation to **Dr. Hassan Mostafa** for his assistance in the preparation of this project. In addition, special thanks to our teaching assistance **Eng. Mahmoud Nagib Sawaby** for helping us with the needs and ideas of the standard cells approach and to **Eng. Mohammad Wagih Emam** for his time and effort for answering our questions and helping deal with Cadence toolkit. Thanks also to our friend **Eng. Islam Abdou** for installing the AMS tool in Cadence.

# ACRONYMS

| ADPLL | All Digital Phase Locked Loop   |

|-------|---------------------------------|

| AMS   | Analog Mixed Simulation         |

| DCO   | Digitally Controlled Oscillator |

| DCV   | Digitally Controlled Varactor   |

| DFF   | D Flip Flop                     |

| DPLL  | Digital Phase Locked Loop       |

| HDC   | Hysteresis Delay Cell           |

| LF    | Loop Filter                     |

| LPLL  | Linear Phase Locked Loop        |

| PD    | Phase Detector                  |

| PFD   | Phase Frequency Detector        |

| PLL   | Phase Locked Loop               |

| SR    | Shift Register                  |

| VCO   | Voltage Controlled Oscillator   |

# Chapter 1

#### INTRODUCTION

The PLL represents one of the most active topics in signal processing and communication theory. The initial ideas started as early as 1919 in the context of synchronization of oscillators. The theory of phase-locked loop was based on the theory of feedback amplifiers. The PLL contributed significantly to communications and motor servo systems. Due to the rapid development of integrated circuits (IC's) since the 1970's, PLLs are widely used in modern signal processing and communication systems, and it is expected that PLL will contribute to improvement in performance and reliability of future communication systems. The applications of PLLs include filtering, frequency synthesis, motor speed control, frequency modulation, demodulation, signal detection, frequency tracking and many other applications.

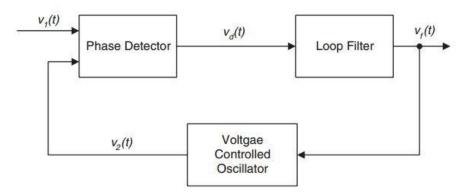

The PLL consists of three main blocks VCO, Loop Filter and Phase detector as shown in figure 1.1.

Figure 1.1: Block diagram of the PLL

There are many types of PLL according to the internal blocks and designing techniques as following:

- LPLL: Linear Phase Locked Loop which contains a VCO and RC circuit for the Loop Filter block and uses a multiplier to detect the phase difference between the reference frequency and the VCO output frequency.

- DPLL: Digital Phase Locked Loop was the very first digital PLL; it was in effect a hybrid device ONLY the phase detector was built as a digital block like EXOR.

- 3. ADPLL: All Digital Phase Locked Loop in which all the blocks are built as digital blocks.

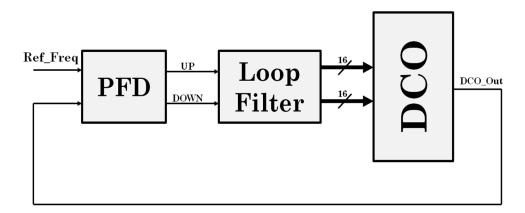

ADPLL consists of the same three main blocks mentioned previously except for the VCO; it will be replaced by the DCO as shown in figure 1.2

Figure 1.2: The Overall block diagram of the ADPLL

PLL in general has its own parameters such as:

- The operating frequency range: the range of frequencies that PLL can lock on them.

- **The lock time:** the time which PLL needs to lock on the reference frequency.

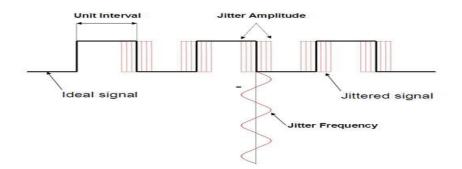

- **The Jitter:** undesired deviation from the true periodicity of an assumed periodic signal.

## What is Jitter?

Jitter is the undesired deviation from true periodicity of an assumed periodic signal, Deviation (expressed in  $\pm$  ps) can occur on either the leading edge or the trailing edge of a signal. Jitter may be induced and coupled onto a clock signal from several different sources and is not uniform over all frequencies.

Period of ring oscillator vibrates in a random manner T=T+T where T is a random value. In high-quality circuits range of T is relatively small compared to T. This variation in oscillator period is called jitter. Local temperature effects cause the period of a ring oscillator to wander above and below the long-term average period when the local silicon is cold, the propagation delay is slightly shorter, causing the ring oscillator to run at a slightly higher frequency, which eventually raises the local temperature. When the local silicon is hot, the propagation delay is slightly longer, causing the ring oscillator to run at a slightly lower frequency, which eventually lowers the local temperature.

Figure 1.3: Jitter Illustration

We considered the DCO as the first design stage, because it consumes about 50% of the system power and covers the most area of the whole system area. The design went through two approaches the custom cells and the standard cells. The DCO is done in the custom approach however; the rest of the design went through both approaches.

The proposed ADPLL has the following specifications:

- Power  $< 1 \ mW$ .

- Area < 0.01  $mm^2$ .

- Frequency Range from 100 MHz to 300 MHz.

- Lock time < 10 μs.</li>

- Peak to Peak Jitter < 20 *ps*.

- R.M.S. Jitter < 5 *ps*.

In the following chapters we are going to discuss the design steps in details for each block of the ADPLL to satisfy these requirements.

Frequently Asked Question about ADPLL:

- Why digital? What is the problem of the analog (linear) one?

- Basically, the ADPLL consumes less power than the linear PLL.

- ADPLL can be easily scaled down to another technology.

- Linear PLL needs an off chip components such as capacitors and resistors (for the loop filter) which do not have a fixed and stable value because they may suffer from aging.

- ADPLL covers less area than linear PLL.

# Chapter 2

## CUSTOM CELLS APPROACH

## 2.1 Digitally Controlled Oscillator

The digitally controlled oscillator (DCO) is considered the heart of the PLL as it controls the overall system performance and consumes the most power and area of the whole design. The proposed DCO follows a full custom design approach to make it easier to control its area and power. It consists of three main blocks:

- 1. A ring oscillator

- 2. A fine tuning stage (DCV Array)

- 3. A Coarse tuning stage (DCV2 Array)

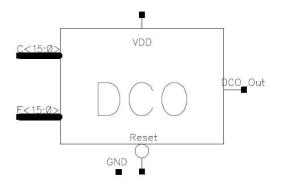

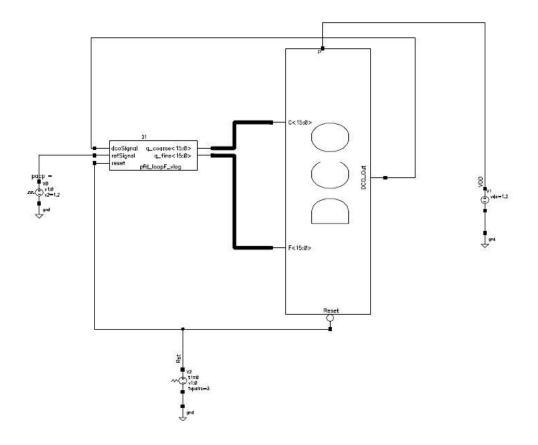

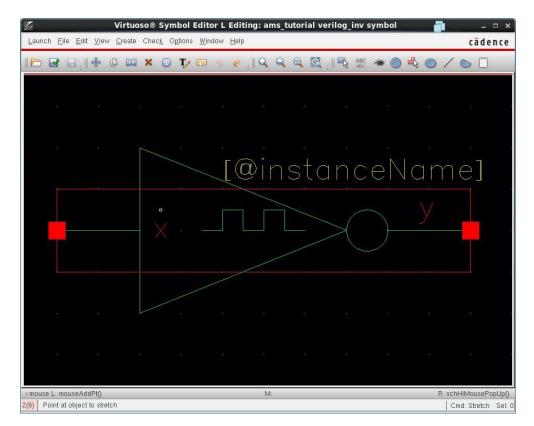

Figure 2.1 is the symbol view of the DCO.

Figure 2.1: DCO symbol view

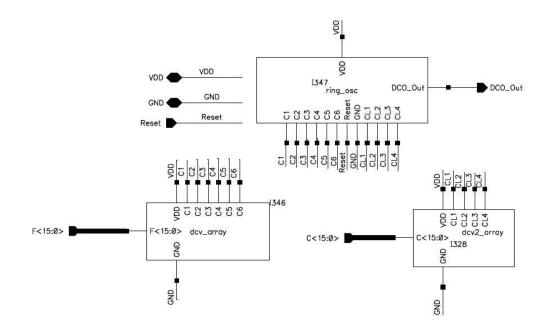

Another figure for the internal block diagram of the DCO is figure 2.2, figuring out its three main blocks.

Figure 2.2: DCO internal structure

We will start our discussion by investigating the internal structure of the ring oscillator followed by the fine tuning stage (DCV Array) and finally the coarse tuning stage (DCV2 Array).

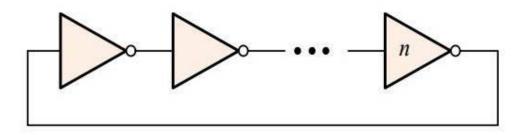

# 2.1.1 Ring Oscillator

The ring oscillator is the source of oscillation for the DCO. It consists of an odd number of inverters in a cascaded configuration with a feedback from the output to the input. Figure 2.3 is a block diagram for the proposed ring oscillator.

Figure 2.3: Ring oscillator block diagram

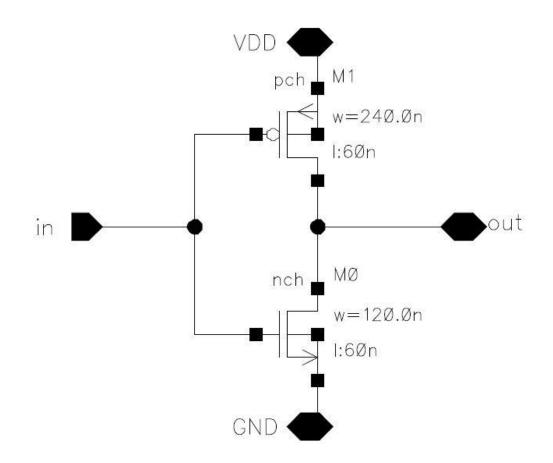

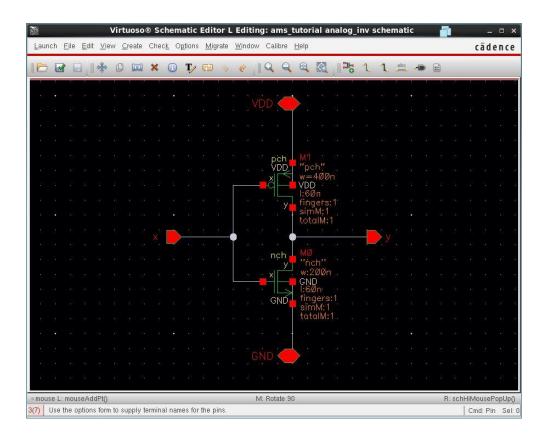

The design of the ring oscillator follows a full custom approach. The following is the schematic view (figure 2.4) of the basic cell for the ring oscillator, the inverter.

Figure 2.4: A Schematic view for the inverter

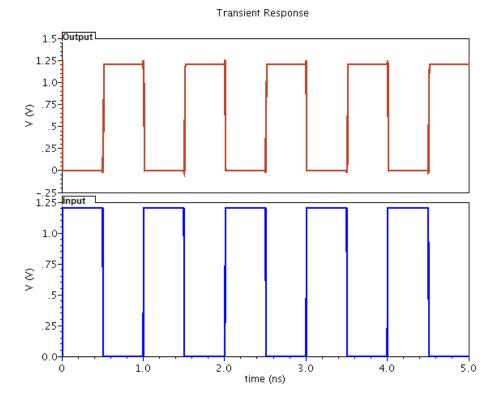

The simulation result for the inverter can be found in figure 2.5.

Figure 2.5: Simulation results of the inverter

Next step is to simulate the ring oscillator as cascaded inverters without any delay cells. Simulation result for this step is shown in figure 2.6.

Figure 2.6: Simulation results for the ring oscillator without delay cells

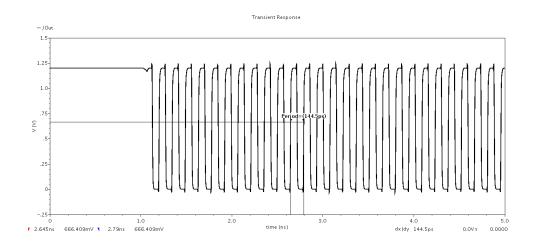

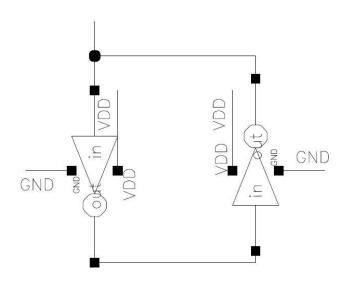

The problem with the simulation results of this ring oscillator is that, the output frequency is in range of GHZ (Period = 144.5 ps) not MHZ and our lock range is from 100 MHZ to 300 MHZ. To solve this problem, we added delay cells to the internal nodes of the ring oscillator. The delay cells to be added to the ring oscillator are Hysteresis Delay Cells (HDC). Each HDC cell consists of two cross coupled inverters. The schematic view of the HDC cell can be found in the figure 2.7.

Figure 2.7: A schematic view of the HDC

The schematic view of the ring oscillator with HDC cells attached to it, is in figure 2.8.

Figure 2.8: The ring oscillator with HDC cells

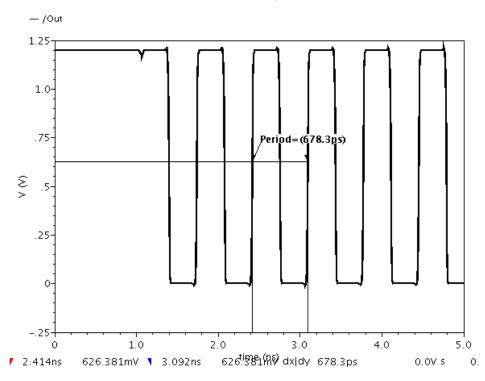

The simulation result for this modified ring oscillator is in figure 2.9 and it increased the period of oscillation from 144.5 ps to 678.3 ps.

Transient Response

Figure 2.9: Simulation results for the ring oscillator with HDC cells

### 2.1.2 A fine tuning stage (DCV Array)

For the proposed DCO, we use a fine tuning stage to give a step change in the period of oscillation of about 48 ps. The DCV cell is a NAND based delay cell. A schematic view of this DCV cell can be found in figure 2.10.

Figure 2.10: A schematic view for the DCV cell

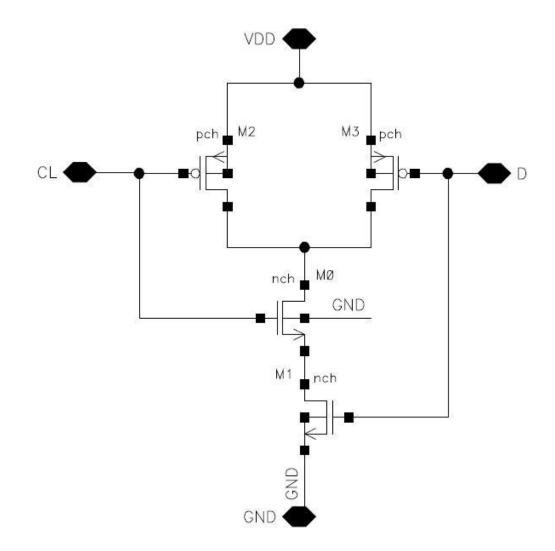

The idea of operation of this cell is that, the gate capacitance seen from node CL (It refers to the load capacitance and it is connected to the output node of each inverter in the ring oscillator) can be changed according to the gate voltage applied to the node D (it refers to digital input bit of the DCO). The formula of

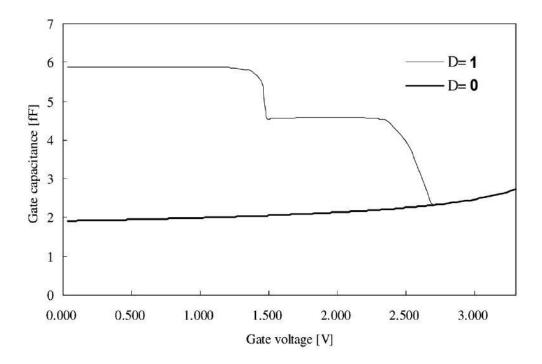

the resulting gate capacitance for this NAND based cell in both cases (when D is high and when it is low) is as follows in figure 2.11:

Figure 2.11: The gate capacitance of NAND gate

Where p0 is probability second input (B) to be equal the ZERO and p1 is probability second input to be equal the ONE (p0 + p1 = 1). The simulation result in figure 2.12 illustrates changing the gate capacitance with the gate voltage (CL) in two cases, when D is high and when it is low. From this result, it seems that we can achieve high capacitance for the case when the digital input bit is high (D=1) and we can get a low capacitance when it is low (D=0). Increasing the load capacitance for each node of the ring oscillator output means increasing the delay as the value of RC constant will be increased. For the ring oscillator and for a typical inverter, the propagation delay can be calculated from the following formula:

$$T_p = 0.69C_L \left(\frac{R_{\rm eqp} + R_{\rm eqn}}{2}\right)$$

Where CL is the output capacitance of the inverters of ring oscillator which is the gate capacitance of the delay cells. Reqp and Reqn are the equivalent resistances of the PMOS and NMOS transistors respectively.

Figure 2.12: Simulation results for the NAND based DCV Cell

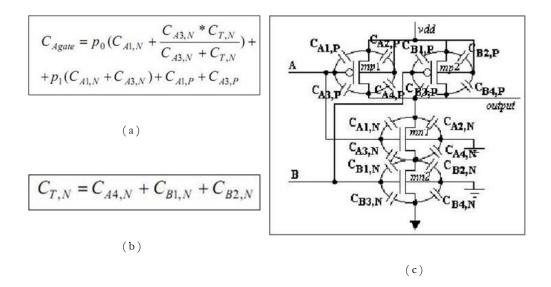

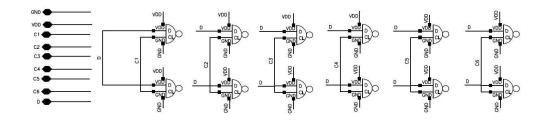

We use this NAND based DCV cell as a building element for a DCV block in the fine tuning stage. Every twelve DCV cells are connected to a single input which is the digital input bit (D). The output of this block consists of six nodes from C1 to C6. These nodes are connected to the corresponding outputs of six inverters in the ring oscillator. A block diagram for the DCV block is in figure 2.13.

Figure 2.13: A block diagram for the DCV building block

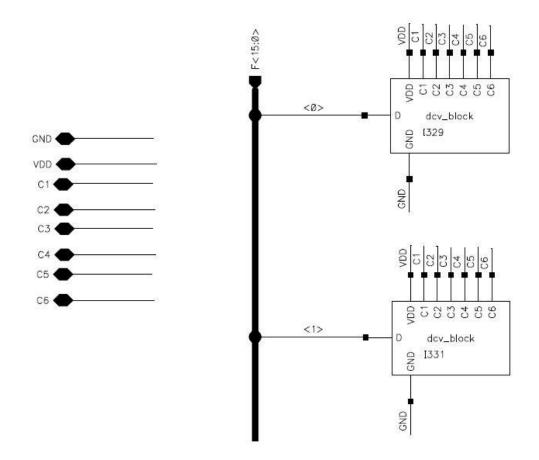

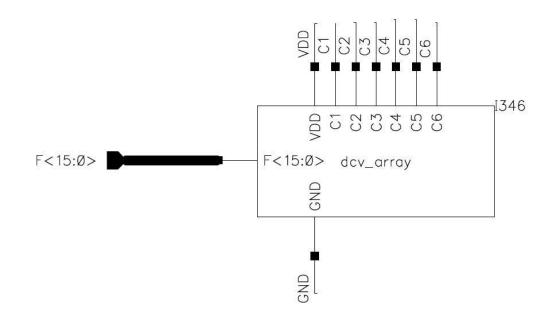

We then use this DCV block to construct the DCV array consisting of sixteen DCV blocks. All outputs of the sixteen blocks (C1 to C6) are connected to the same six nodes of the ring oscillator but each input from the DCV blocks is connected to a different external digital bit so, for the DCV array of the fine tuning stage we have a digital word of sixteen bits. Figure 2.14 is the internal structure of the DCV array:

Figure 2.14: DCV array internal structure

A symbol view of this DCV array is shown below in figure 2.15:

Figure 2.15: A symbol view for the DCV array

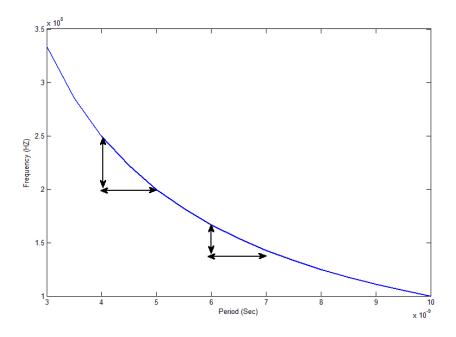

An important thing to notice here is that, although we achieved a fixed step in period of about 48ps for fine stage, the step in output frequency is not fixed because the relation between the frequency and period is not linear. For the same period step we get many frequency steps depending on the location of this period step in time access. For example, our DCO period range is from 3.3 ns to 10 ns consider adding a period step to the first period in range, from 3.3 ns to 3.348 ns (3.3ns+48ps), 3.3 ns corresponds to a frequency of 303 MHZ and 3.348 ns corresponds to a frequency of 298.686 MHZ so a period step of 48 ps from 3.3 ns to 3.348 ns causes a frequency step of 4.314 MHZ. Let's consider the same period step added to another period in another location in time access, for the last period of output oscillation from the DCO which is 10 ns, the period before this one is 9.952 ns (10 ns - 48 ps), 9.952 ns corresponds to a frequency of 100.482 MHZ and 10 ns corresponds to a frequency of 100 MHZ, so the same period step of 48 ps when added to the period 9.952 ns we get a frequency step of 0.482 MHZ. For these two cases we get two different frequency steps of 4.314 MHZ and 0.482 MHZ although the period step of fine stage is constant. Conclusion is that, although the period step for fine stage is constant we will get different frequency steps (not fixed) because the relation between frequency and

15

period is not linear. Figure 2.16 illustrates why we get different frequency steps for the same period step.

Figure 2.16: Period step Vs. frequency steps

#### 2.1.3 A coarse tuning stage (DCV2 Array)

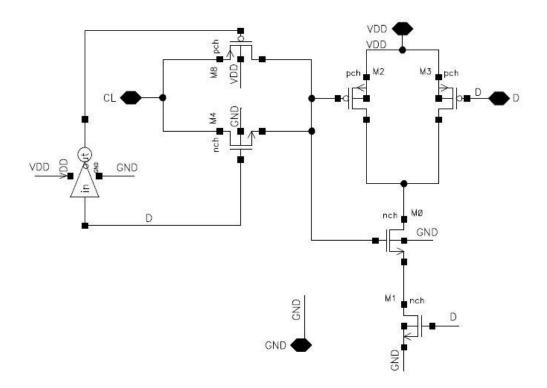

After using the fine tuning DCV array we achieved a relatively small step change in output period of the DCO and consequently a relatively small frequency steps. For the coarse stage we need to get larger frequency steps to reduce the lock time of the PLL, to achieve these larger frequency steps we have to use delay cells with larger period steps than the fine tuning stage (48 ps), so we used another delay cell to get this larger period step. The delay cell used for coarse tuning stage is also based on the NAND configuration but with a transmission gate in the beginning. The enable line for this transmission gate is the external digital input bit (D) and the input to it is the load capacitance node (CL) which is connected to the output of each inverter in the ring oscillator. Figure 2.17 is a schematic view for this delay cell.

Figure 2.17: A schematic view for the DCV2 cell

When the external input is low (D=0), the CL node will be disconnected from the NAND cell and introduces low capacitance and consequently low delay. When the external input is high (D=1), the CL node is now connected to the NAND cell and can see the gate capacitance of it. The two cases of D=0 and D=1 here are different from those in fine tuning stage, as in fine tuning stage the CL node was connected to NAND cell in both cases that's why the period step in fine stage was relatively small. In coarse stage, the CL node is connected only when D=1 so we can say that, in coarse stage the node CL can see the capacitance of the NAND cell or it cannot see it, so the period step here is larger than the period step in fine stage. For coarse stage we achieved a period step of 380 ps. Another advantage for using the DCV2 cell is that, it helped us increase the largest output period of the DCO (10 ns) without affecting the smallest period (3.3 ns) by changing the sizing of the NAND cell in this DCV2 cell

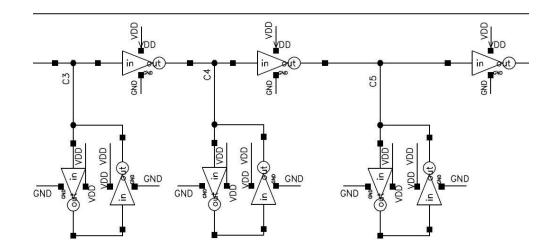

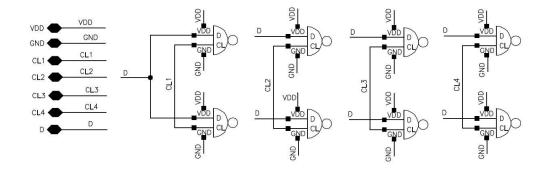

We use this NAND based DCV2 cell as a building element for a DCV2 block in the coarse tuning stage. Every eight DCV2 cells are connected to a single input which is the digital input bit (D). The output of this block consists of four nodes from CL1 to CL4. These nodes are connected to the corresponding outputs of four inverters in the ring oscillator. These four inverters are following the six inverters used in the fine stage. A block diagram for the DCV2 block is in figure 2.18.

Figure 2.18: DCV2 block

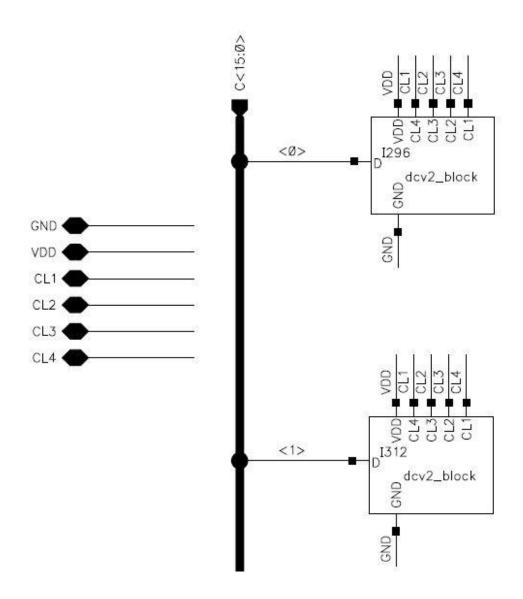

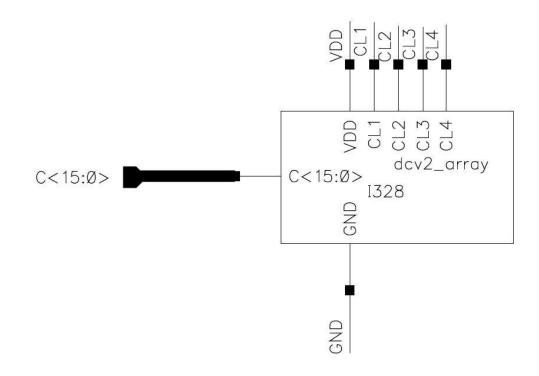

We then use this DCV2 block to construct the DCV2 array consisting of sixteen DCV2 blocks. All outputs of the sixteen blocks (CL1 to CL4) are connected to the same four nodes of the ring oscillator but each input DCV2 blocks is connected to a different external digital bit so, for the DCV2 array of the coarse tuning stage we have a digital word of sixteen bits. The following figure is the internal structure of the DCV2 array (Figure 2.20).

Figure 2.19: DCV2 array

A symbol view of this DCV2 array is shown in figure 2.20.

Figure 2.20: A symbol view for the DCV2 array

## 2.1.4 Conclusion and final results

In this section we introduced the proposed DCO which is consisting of three main blocks:

- 1. A ring oscillator

- 2. A fine tuning stage

- 3. A coarse tuning stage

The output period for this DCO ranges from 3.3 ns to 10 ns which is equivalent to a lock range from 100 MHZ to 300 MHZ. We used HDC cells to add a fixed delay to the ring oscillator and DCV cells for both fine and coarse tuning stages to add a programmable delay. The fine tuning stage gives a small step (48 ps) in period and consequently small steps in frequency. The coarse tuning stage gives large period step (380 ps) and consequently large steps in output frequency.

The following table in figure 2.21 shows different output periods of the DCO according to different values for the digital words of both fine and coarse tuning stages.

| Control bits                        | Period  | Frequency | Period step | Freq. step<br>MHz |

|-------------------------------------|---------|-----------|-------------|-------------------|

| Fine Word Coarse Word               | ns      | MHz       | ns          | MHZ               |

| 0000000 0000000 0000000 0000000     | 3.289   | 304.878   |             |                   |

| 00000000 0000000 0000000 00000001   | 3.669   | 272.553   | 0.38        | 32.325            |

| 10000000 0000000 0000000 00000001   | 3.718   | 268.961   | 0.049       | 3.592             |

| 10000000 0000000 0000000 00000011   | 4.1     | 243.902   | 0.382       | 25.059            |

| 11000000 0000000 0000000 00000011   | 4.147   | 241.138   | 0.047       | 2.764             |

| 11000000 00000000 0000000 00000111  | 4.53    | 220.75    | 0.383       | 20.388            |

| 11100000 0000000 0000000 00000111   | 4.578   | 218.435   | 0.048       | 2.315             |

| 11100000 00000000 00000000 00001111 | 4.961   | 201.572   | 0.383       | 16.863            |

| 11110000 0000000 0000000 00001111   | 5.009   | 199.641   | 0.048       | 1.931             |

| 11110000 0000000 0000000 00011111   | 5.38973 | 185.538   | 0.38073     | 14.103            |

| 11111000 0000000 0000000 00011111   | 5.43695 | 183.927   | 0.04722     | 1.611             |

| 11111000 00000000 00000000 00111111 | 5.82148 | 171.778   | 0.38453     | 12.149            |

| 11111100 00000000 00000000 00111111 | 5.869   | 170.387   | 0.04752     | 1.391             |

| 11111100 00000000 00000000 01111111 | 6.25404 | 159.897   | 0.38504     | 10.49             |

| 11111110 00000000 00000000 01111111 | 6.29857 | 158.766   | 0.04453     | 1.131             |

| 11111110 0000000 0000000 11111111   | 6.68375 | 149.617   | 0.38518     | 9.149             |

| 11111111 0000000 0000000 11111111   | 6.73115 | 148.563   | 0.0474      | 1.054             |

| 11111111 00000000 00000001 11111111 | 7.1095  | 140.657   | 0.464       | 7.906             |

| 11111111 10000000 00000001 1111111  | 7.1607  | 139.651   | 0.0512      | 1.006             |

| 11111111 1000000 00000011 11111111  | 7.5419  | 132.593   | 0.3812      | 7.058             |

| 11111111 11000000 00000011 11111111 | 7.59375 | 131.687   | 0.05185     | 0.906             |

| 11111111 11000000 00000111 11111111 | 7.9758  | 125.379   | 0.38205     | 6.308             |

| 11111111 11100000 00000111 1111111  | 8.0248  | 124.614   | 0.049       | 0.765             |

| 11111111 11100000 00001111 11111111 | 8.41188 | 118.879   | 0.38708     | 5.735             |

| 11111111 11110000 00001111 11111111 | 8.4583  | 118.227   | 0.04642     | 0.652             |

| 11111111 11110000 00011111 11111111 | 8.84562 | 113.05    | 0.38732     | 5.177             |

| 11111111 11111000 00011111 11111111 | 8.8918  | 112.463   | 0.04618     | 0.587             |

| 11111111 11111000 00111111 11111111 | 9.2775  | 107.788   | 0.3857      | 4.675             |

| 11111111 1111100 00111111 1111111   | 9.3259  | 107.228   | 0.0484      | 0.56              |

| 11111111 1111100 01111111 1111111   | 9.7117  | 102.969   | 0.3858      | 4.259             |

| 11111111 1111110 01111111 1111111   | 9.7605  | 102.454   | 0.0488      | 0.515             |

| 11111111 1111110 11111111 1111111   | 10.146  | 98.561    | 0.3855      | 3.893             |

| 11111111 1111111 111111111111111111 | 10.194  | 98.097    | 0.048       | 0.464             |

Figure 2.21: Different output periods of the DCO

The simulation result in figure 2.22 is different output waveforms for the DCO.

Figure 2.22: Different output waveforms of the DCO

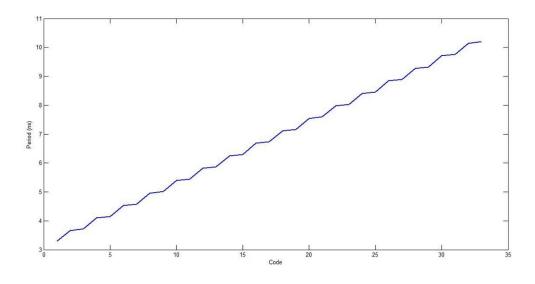

Figure 2.23 is the period steps versus the digital code according to the above table, one coarse step change followed by one fine step change. From this figure, one can easily notice the coarse step is larger than the fine step. The start point of our range is 3.3 ns and the end point is 10 ns corresponds to the lock range for the proposed DCO (100 MHZ to 300 MHZ).

Figure 2.23: Period steps versus code

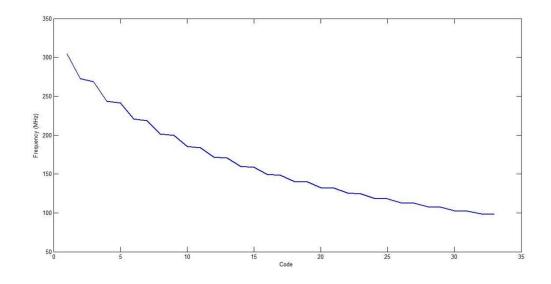

Figure 2.24 is the output frequency versus the 32-bit digital input word (16-bit word for fine stage and 16-bit word for coarse stage).

Figure 2.24: Frequency steps versus code

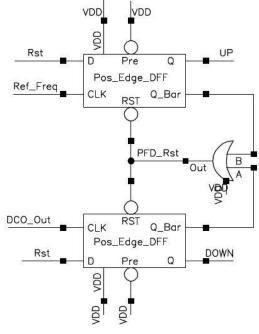

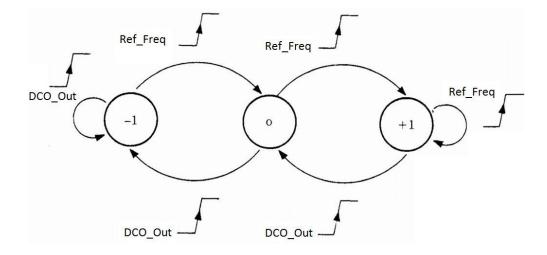

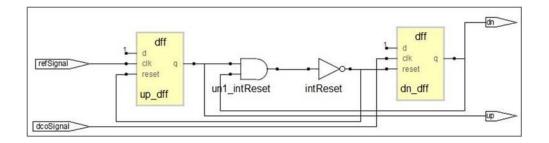

#### 2.2 PFD

A phase detector is a circuit capable of delivering an output signal that is proportional to the phase difference between its two input signals Ref\_Freq and DCO\_Out as mentioned in figure 1.2. When the PLL moved into digital territory, digital phase detectors become popular, such as EXOR gate, the edge-triggered JK-flip flop, and the so-called phasefrequency detector (PFD). The PFD differs greatly from the other phase detector types as its name implies, its output signal depends not only on phase error but also on frequency error when the PLL has not yet acquired lock. The PFD is built from two D-flip flops, whose outputs are denoted UP and DOWN(DN) as shown in figure 2.25, these two signals are the digital representation of the phase/frequency error. The PFD can be in one of four states:

- UP=0, DN=0

- UP=1, DN=0

- UP=0, DN=1

- UP=1, DN=1

The fourth state is inhibited, however, by an additional gate. Whenever both flip flops are in the 1 state, a logic low level appears at their reset inputs, which reset both flip flops. We assign the symbols -1, 0, and 1 to these three states :

- UP=0, DN=0  $\rightarrow$  state -1

- UP=1, DN=0  $\rightarrow$  state 0

- UP=0, DN=1  $\rightarrow$  state 1

The actual state of the PFD is determined by the positive-going transients of the signals Ref\_Freq and DCO\_Out, as explained by the state diagram in figure 2.26, a positive transition of Ref\_Frq forced the PFD to go into its next higher state, unless it is already in the 1 state. In analogy, a positive edge of DCO\_Out forces the PFD into its next lower state, unless it is already in the -1 state.

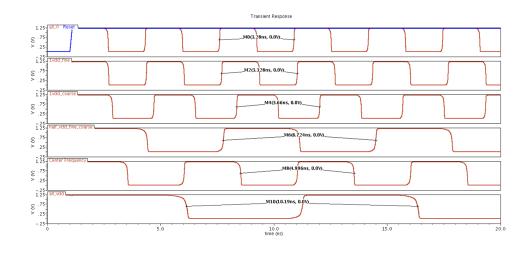

Figure 2.25: PFD schematic

Figure 2.26: State diagram of the PFD

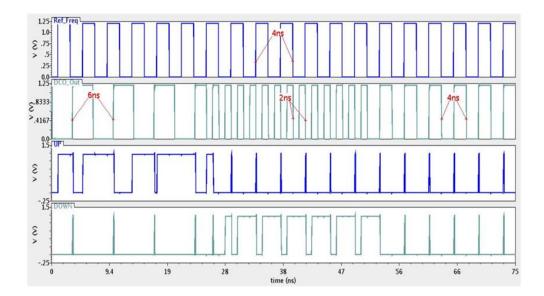

To see how the PFD works in a real PLL system, we consider the waveforms in figure 2.27, this figure shows the three cases:

- a) First 25ns shows the case where Ref\_Freq leads, therefore the PFD toggles between states 0 and 1.

- b) If Ref\_Freq lags as in the next 25ns, the PFD now toggles between states-1 and 0.

- c) The signals Ref\_Freq and DCO\_Out are 'exactly' in phase; both positive edges occur at the same time; hence the PFD will stay in state 0 forever.

Figure 2.27: PFD simulation results

#### 2.3 Loop Filter:

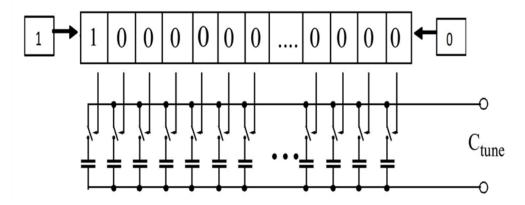

The Loop filter stage controls the output capacitance by changing the number of DCV cells that are turned on, as shown in figure 2.28 the digital control signals is used to increase/decrease the DCO frequency for a certain period of time by reducing /increasing the capacitance. If the input to the DCV is '1', it provides more capacitive load at the output. If more number of cells are on (input is '1'), then it acts as more capacitive load on the ring oscillator which reduces the DCO frequency.

Figure 2.28: digital control signals used to switch a set of varactors

In order to control each of the fine DCV array and the coarse DCV array individually, we have used two 16-bits bi-directional loadable shift registers and here part of the schematic view for each shift register in figure 2.29

Figure 2.29: Schematic view of the shift register

Initially, 8 DCV cells of each array are on, this achieved by using asynchronous Reset and Preset signals. Depending on the up/down signals from PFD, the frequency is either increased or decreased. When phase and frequency acquisition starts, if the output of PFD is up, then the contents of the shift register are left shifted and bit '0' is pushed into Q<15> and hence the capacitive load decreases and the frequency increases. Likewise, if it is down, the contents of the shift register are right shifted and bit '1' is pushed into Q<0>. This reduces the frequency of the DCO as the capacitive loading at the output increases.

# 2.4 Overall Design

In this section the simulation results of the whole system will be introduced.

### 2.4.1 Extreme Reference frequency

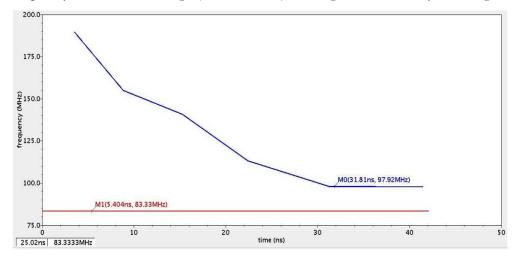

First let the input (reference frequency) signal be an extreme, let's say the minimum frequency in the desired range (100-300MHz) as in figure 2.30.And by knowing

Figure 2.30: Reference = 100 MHz

that the DCO frequency initially equals to the center frequency (200MHz), then the shift register should get only DOWN pulses from the PFD, which activates all the DCV cells and introduces the lowest frequency .now what about the lock time ? Actually this depends on two factors, the:

- CLK used for the loop filter: this means the rate of changing in DCO frequency at a certain time. It's clear that we need to increase the frequency of this CLK to get smaller lock time.

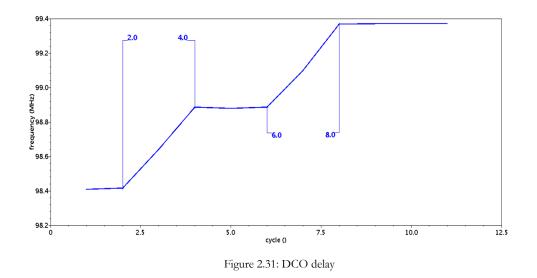

- ii. DCO Delay : this means time needed by the DCO to change its frequency after one step delay as shown in figure 2.31, where one DCV cell is deactivated after two cycles, the effect of this step appears after exactly two cycles, this time is considered as the DCO delay, thus the CLK above in part (i) should take in consideration this delay to get the true UP/DN pulse after the new change in the DCO frequency.

# 2.4.2 Intermediate Reference frequency

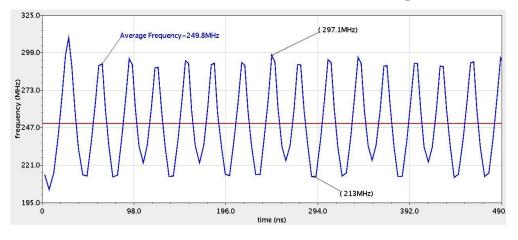

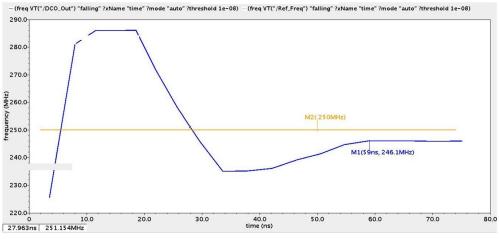

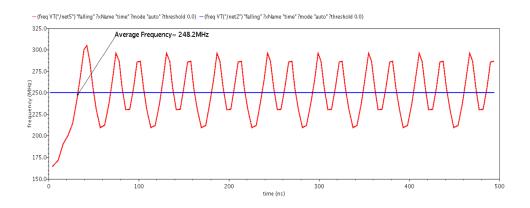

Now let's consider this case, reference = 250MHz as below in figure 2.32.

Figure 2.32: Reference= 250MHz

It's clear that average frequency is almost equals to the reference, but the problem that appears here due to the wide steps of the course stage (up to 31MHz), which results to these oscillations with a very high peak-to-peak value. Simply to solve this problem, the coarse stage must be stopped after being operating separately from the fine stage. This is applied using a 4bit Counter to count the maximum number of steps needed by the coarse stage, which is 16 at the worst case, after that a carry signal is used to turn off the coarse shift register and activates the fine one. The simulation results of this idea are

shown in figures 2.33a, 2.33b and 2.33c.

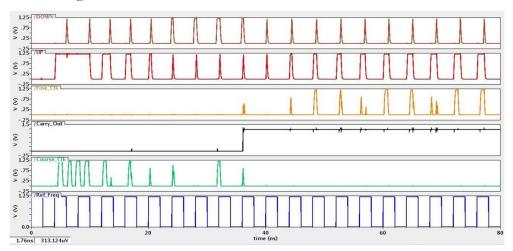

a) Control signals

b) Frequency response

| Course stage     |                   |                |  |  |  |  |  |  |  |  |

|------------------|-------------------|----------------|--|--|--|--|--|--|--|--|

| Course SH_Reg    | Fine SH_Reg       | Frequncy (MHz) |  |  |  |  |  |  |  |  |

| 0000000 00000001 | 0000000 00001111  | 260.28         |  |  |  |  |  |  |  |  |

| 0000000 00000011 | 00000000 00001111 | 236.85         |  |  |  |  |  |  |  |  |

|                  | Fine stage       |                |

|------------------|------------------|----------------|

| Course SH_Reg    | Fine SH_Reg      | Frequncy (MHz) |

| 0000000 00000011 | 0000000 00000001 | 245.21         |

| 0000000 00000011 | 0000000 00000000 | 246.13         |

c) Digital words of Both SRs

Figure 2.33: Effect of using counter

In this example the reset signal of the whole system was designed to start the DCO oscillations at the center frequency, this is achieved by activating four DCV cells from each array, to calculate this frequency as explained in section 2.1:

Period (ps) =  $3270 + \text{Coarse}_1$ 's × (380) + Fine\_1's × (48) = 5ns (200MHz).

Through the first stage the fine SR is stopped as shown in figure 2.33a and 2.33c, and at the end of this stage the DCO frequency was undecided between two frequencies around the reference corresponding to the digital words which clarified in figure 2.33c, after that the course stage stopped using the carry signal at 38n as shown in figure 2.33a.At the same time the fine stage started, this can be observed through the frequency response in figure 2.33b ,where the very small slopes appears after the 38ns.

## 2.4.3 Frequency step response

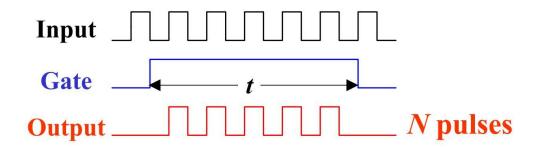

It was necessary to consider in our design that the Reference signal frequency may be changed during the loop, because this PLL targets a low power clock and data recovery system. But in order to detect this change, the loop filter won't be a simple shift registers as it now because a certain controlling circuit must be added. Actually we have replaced the coarse SH by a frequency counter circuit which is one of Digital Instruments that can be used to measure signal frequency and period, the basic idea is illustrated in the following figure:

Figure 2.34: Frequency counter

We have implemented this idea by generating the Gate signal (figure 2.34) from the reference frequency, and the input clock source (time base) signal which used to trigger the counter from a ring oscillator which already discussed in section 2.1.1.

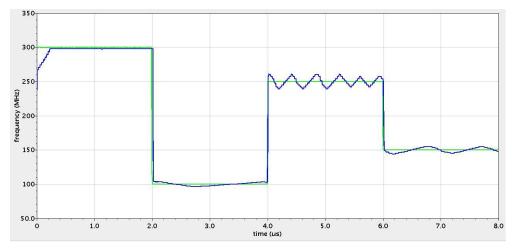

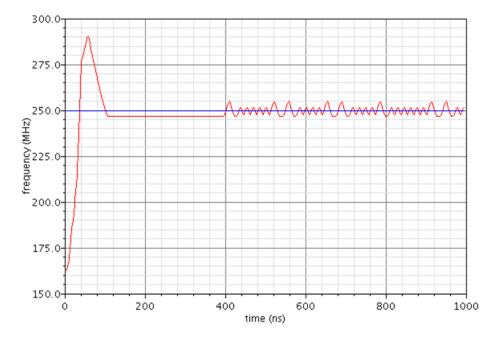

After counting the N pulses mentioned in figure 2.34, this number is therefore mapped to the 16 bit to control the coarse DCV array. Note that at the end of each counting period, the counted value should mapped synchronously and the counter should cleared. In the following the whole system simulation result after using the frequency counter :

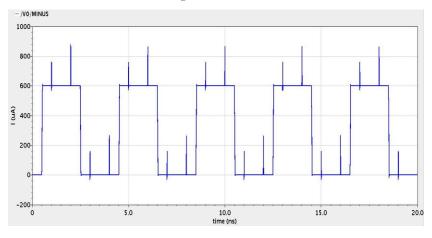

Figure 2.35: frequency step response

After this modification on the system to become capable of reacting with the step system response, the consumed power is increased from 0.25 to **0.6** mWatt due to the high frequency clock added. Also the lock time at the worst case does not exceed 300ns. Now there is one more enhancement needed

The last improvement needed, is to reduce the oscillation of the fine stage around the reference, this is achieved by slowing its clock frequency. Figure 2.36 shows the result after this modification.

Figure 2.36: Eliminating the oscillations

As expected, slowing the fine SR led to the expansion of the time lock until the time of 1us as figure 2.36 shows.

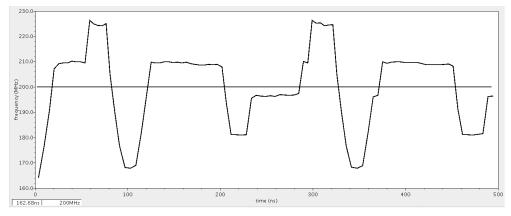

# 2.4.4 Jitter calculation :

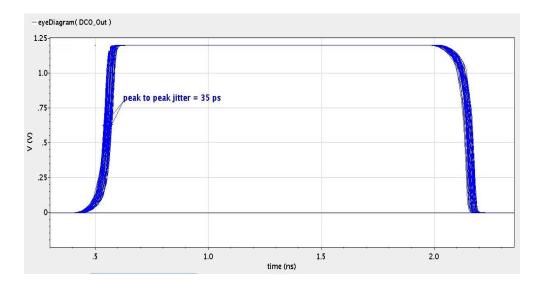

Figure 2.37 shows the eye-diagram of DCO output clock when locked at 300 MHz plotted using Cadence tools. In this eye-diagram, each and every cycle of the DCO output clock are overlapped on one clock period (after the DCO clock is locked to the reference) and the maximum deviation that can be obtained from the graph is measured as peak-to-peak jitter. Number of cycles that are taken into account are 100. The delay is measured at 50% voltage levels and the period jitter determines how noisy and stable the oscillator output signal is.

Figure 2.37: Eye-diagram of the ADPLL

The peak-to-peak jitter for this implementation when the feedback signal is locked at 300 MHz is 35 ps.

### Chapter 3

#### STANDARD CELLS APPROACH

**Standard Cells Approach** means that the targeted block will be written with one of the Hardware Description Language HDL codes such as Verilog or VHDL, and then can be translated into an hardware circuit using Standard Cells library. Thanks to AMS we are able to simulate and test the targeted block with analog blocks in cadence environment.

One big advantage of using such approach is that the designer is not have to deal with the block gates at the transistor level and check the sizing of the logic gates . This approach also made the layout step very easy and effective in area.

### 3.1 PFD

As mentioned before, the Phase and Frequency Detector (PFD) will be used as a phase detector to detect the phase and the frequency difference between the reference signal and the output signal of the DCO.

First of all, we will write the code of our PFD using Verilog programming language, we will design a block which has:

- Two input ports (reference signal and DCO output).

- Two output ports (Up and Down).

The Up signal indicates that the system should increase the DCO frequency (i.e. the reference frequency is higher than the DCO frequency) and the Down signal indicates that the system should decrease the DCO frequency.

module dff (input d,clk,reset,output reg q); always@(posedge clk,negedge reset) if(~reset) q<=1'b0; else q<=d; endmodule module pfd (input refSignal,dcoSignal,output up,dn); wire intReset; assign intReset=~(up&dn); dff up\_dff(1'b1,refSignal,intReset,up); dff dn\_dff(1'b1,dcoSignal,intReset,dn); endmodule

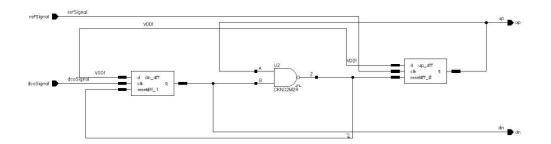

And using Synplify PRO we translated our PFD into the corresponding standard cells schematic as shown in figure 3.1

Figure 3.1: PFD schematic

This PFD can be imported as Verilog code in cadence also , see appendix A for more details.

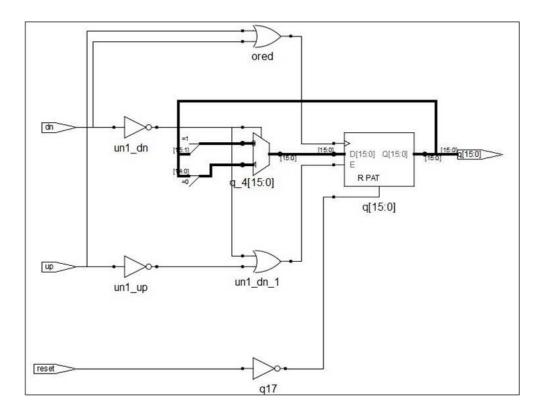

### 3.2 Loop Filter

The Loop Filter used here is simply a 16 bits shift register ,following the same procedure of PFD ,we got the schematic view of the Loop Filter as shown in figure 3.2.

```

module loopFilter ( input up,dn,reset, output reg [15:0] q);

wire ored;

assign ored = up | dn;

always @(posedge ored, negedge reset)

if(~reset) //active low reset(level sensitive)

q <= 16'b11110000_00000000;

else if(up & ~dn)

q <= \{q[14:0],1'b0\};

else if(dn & ~up)

q <= \{1'b1,q[15:1]\};

endmodule

```

Figure 3.2: Loop Filter schematic

We used two Loop Filters, one as a Coarse and the other as a fine, the Coarse one is responsible for the large step change in the DCO output frequency while the fine one is responsible for the small step change.

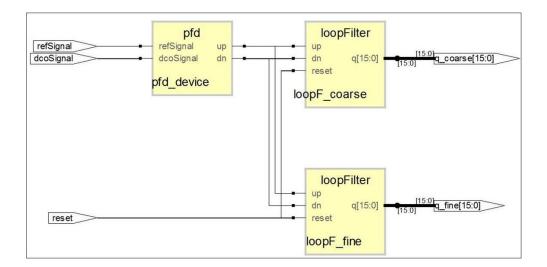

#### 3.3 PFD and Loop Filter

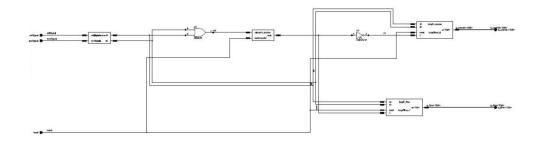

Now, we have PFD and Loop Filter as functional blocks, so we can connect them together as shown in figure 3.3.

Figure 3.3: PFD and Loop Filter

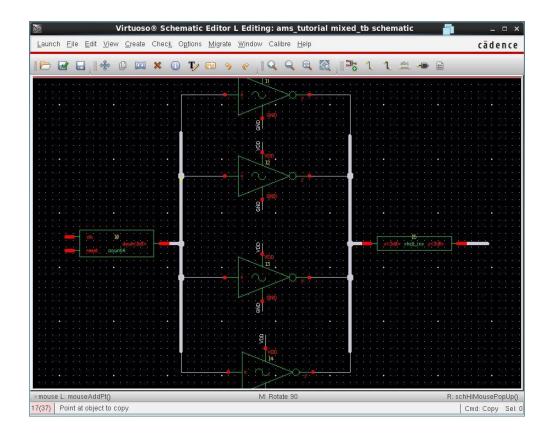

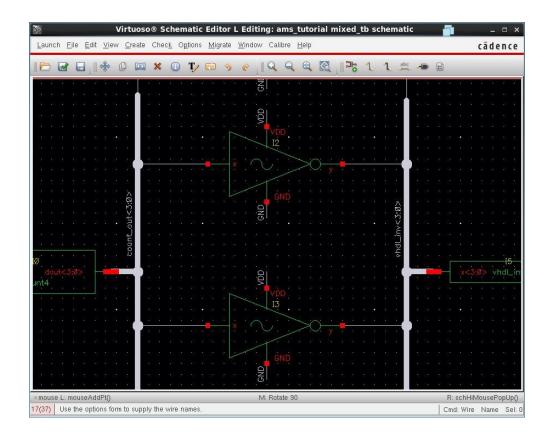

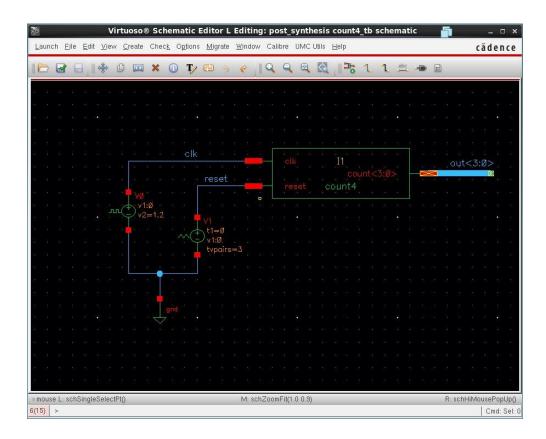

Now, we have our functional block (PFD + Loop Filter) so we can import it to cadence environment and connect it with the custom designed DCO.

# 3.4 Overall Design

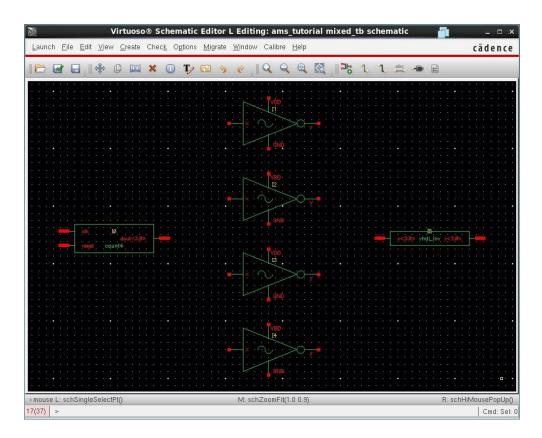

Figure 3.4: Overall ADPLL (standard cells)

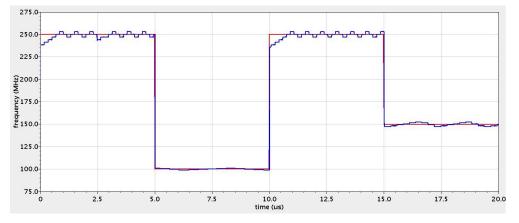

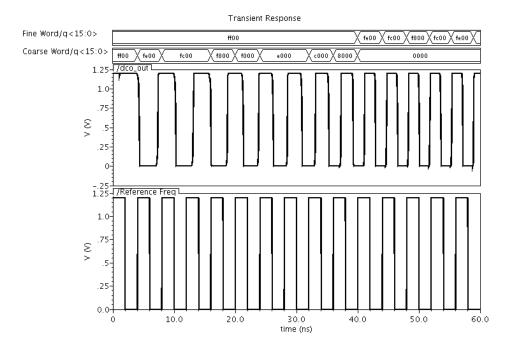

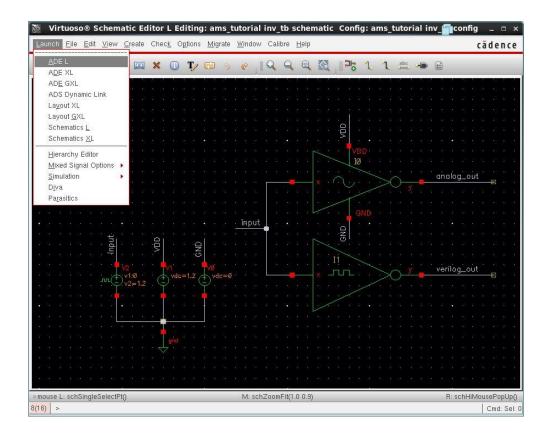

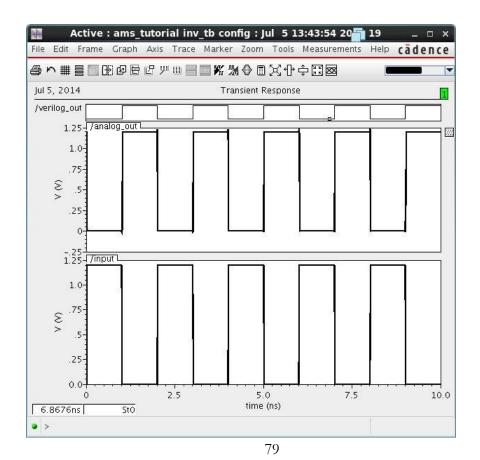

Using AMS we can simulate analog and digital(functional) blocks together and check the functionality of our ADPLL and the result was as shown in figure 3.5

Figure 3.5: AMS of the overall ADPLL without the counter

As we can see that the DCO output frequency is oscillating around the reference frequency and that is due to the coarse large steps, so we need to stop the coarse shift register to eliminate the large oscillations.

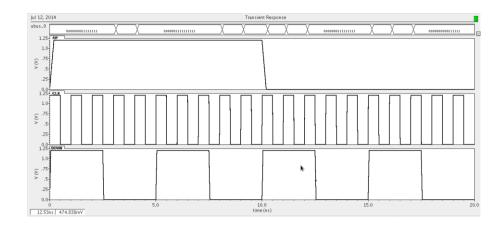

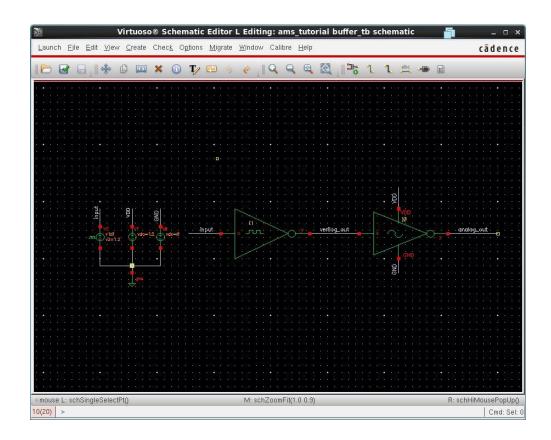

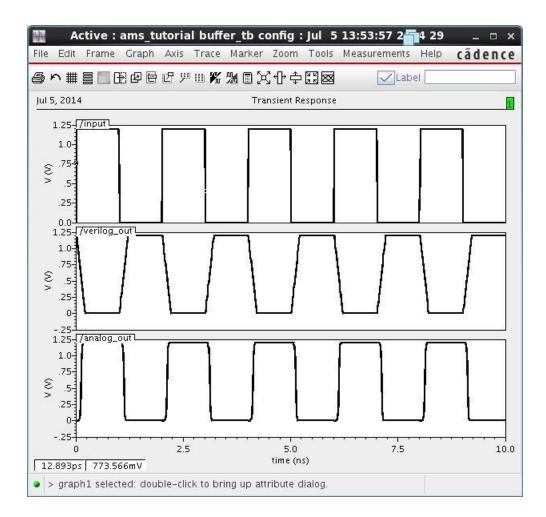

4 bits counter is used for that purpose and when the counter carry bit activated the coarse shift register is turned off and the fine one is turned on as shown in figure 3.6

Figure 3.6: AMS simulation of the overall ADPLL with counter

And the result of the Overall ADPLL as a functional (behavioral) block was as shown in figure 3.7.

Figure 3.7: AMS of the ADPLL with counter.

From the above figure we found that the lock time is less than 150 ns which means that our lock time restriction (lock time < 10 us) is satisfied.

But, the problem is, the above design assuming the reference frequency is fixed and will not exposed to a step change.

All the above simulation results is done considering the functional behavioral of the PFD and the Loop Filter (as code only).

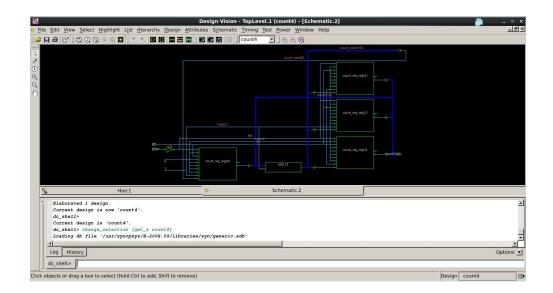

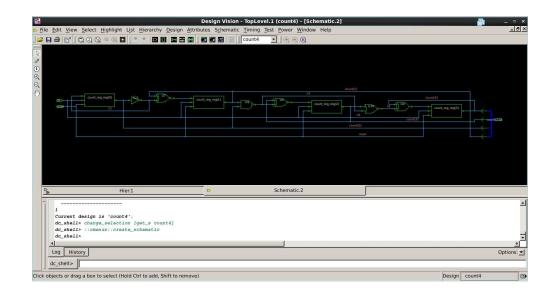

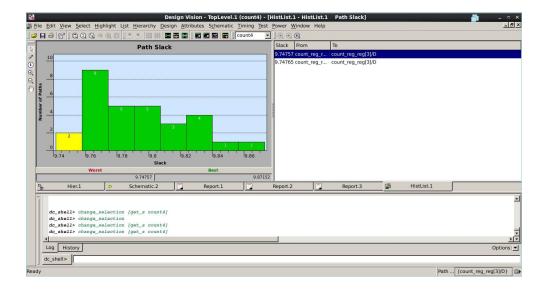

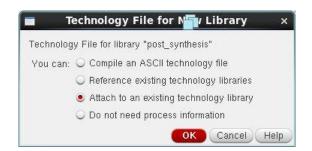

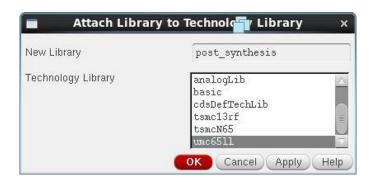

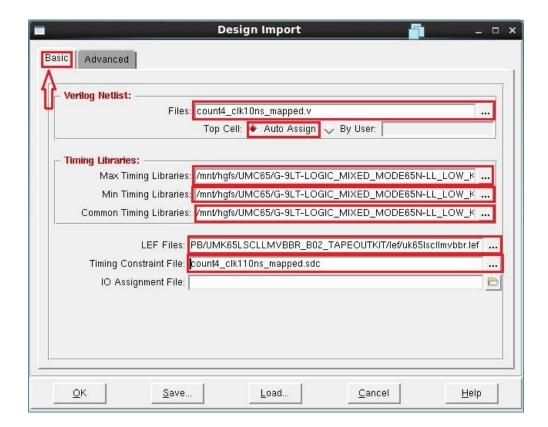

We did the technology mapping using Design Compiler by converting the functional Verilog code of the PFD and the Loop Filter into a netlist to generate a mapped code which contains the needed standard cells to achieve the block functionality.

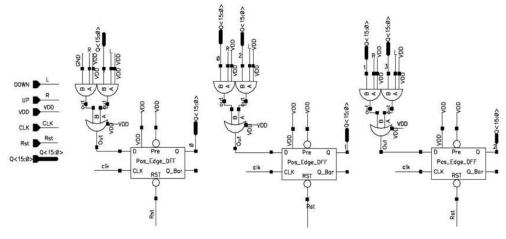

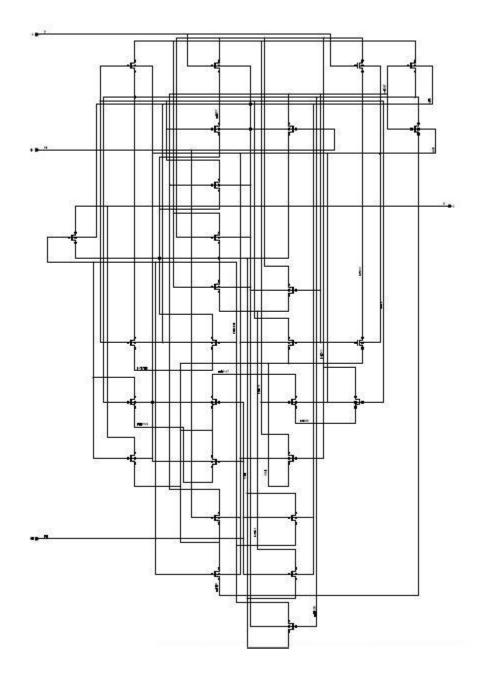

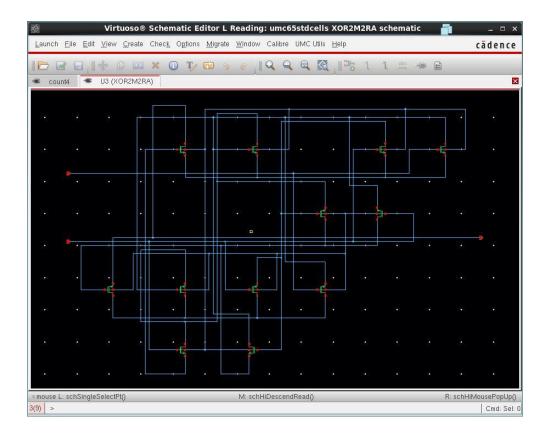

We extracted the transistor level schematic of the PFD and the Loop Filter successfully using the standard cells of UMC65nm digital kit as shown in figure 3.8.

a) Imported schematic of PFD in cadence

| P-   | -0 | -d |  | ┍⋑┈ |    | <b>-</b> | -0 |     | ┍╴ |          | ┍═᠉─        | <b>₽</b> ° | -6-    |

|------|----|----|--|-----|----|----------|----|-----|----|----------|-------------|------------|--------|

|      |    |    |  |     | 5  |          |    |     |    |          |             |            | -0     |

|      |    |    |  |     |    |          |    |     |    |          |             |            | -6-    |

|      |    |    |  |     | 10 |          |    | -D- |    |          |             | <u> </u>   | -<br>- |

|      |    |    |  |     |    |          |    |     |    |          |             |            |        |

|      |    |    |  |     |    |          |    |     |    | <u> </u> | <b>1</b> 0- |            |        |

|      |    |    |  |     |    |          |    |     |    |          |             |            |        |

| <br> |    |    |  |     |    |          | -  |     |    | -        |             |            | н<br>  |

b) Imported schematic of Loop Filter in cadence

c) Imported schematic of PFD and Loop Filter together in cadence

Figure 3.8: The standard cells of both PFD and Loop Filter

As an example we took a snap shot of one standard block inside the PFD schematic in figure 3.8.a. above

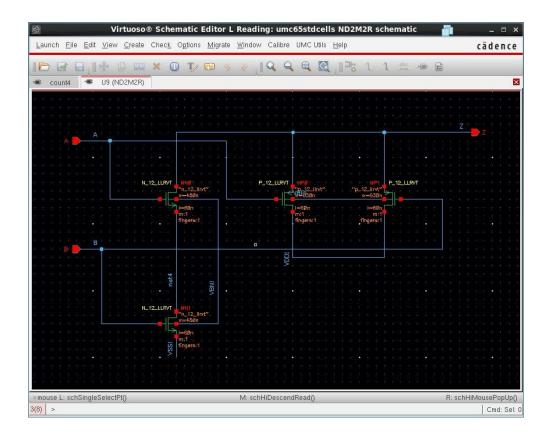

Figure 3.9: The transistor level of the standard D flip flop in cadence.

# Chapter 4

#### LAYOUT

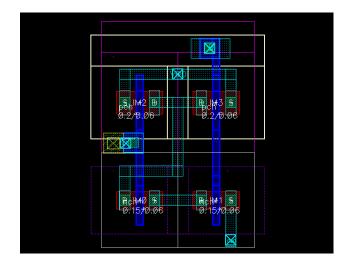

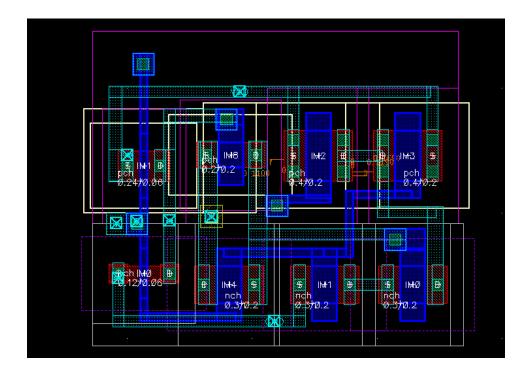

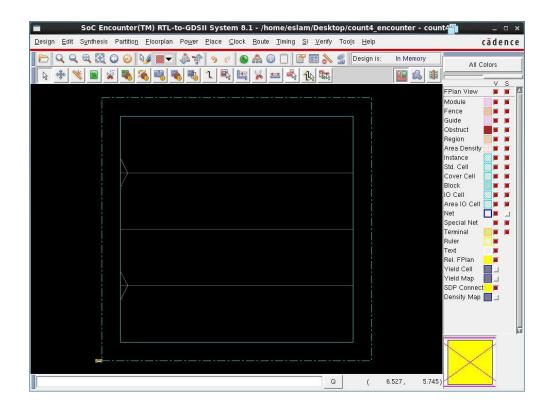

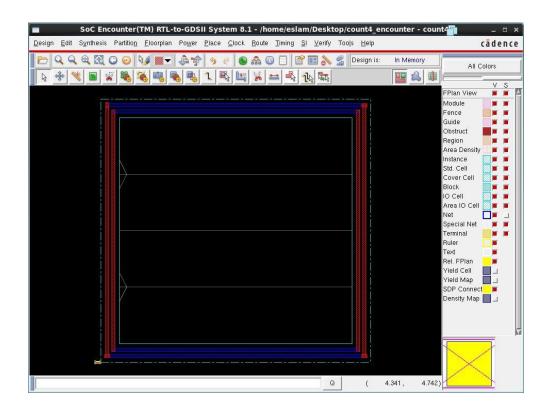

The last step of the design flow is the layout, first of all DCO is considered as the core of the ADPLL so as we started the design in the schematic scope with the DCO, we will start with the DCO in the layout scope and we believe that the range will be changed due to the capacitance and the resistance added by the layout (i.e. more delay).

### 4.1 DCO

The proposed DCO depends mainly on the delay cells (HDCs and DCVs) and because of the layout, the delay is not the same as schematic any more.

#### 4.1.1 DCV

Figure 4.1: DCV layout

Figure 4. 2: DCV block layout

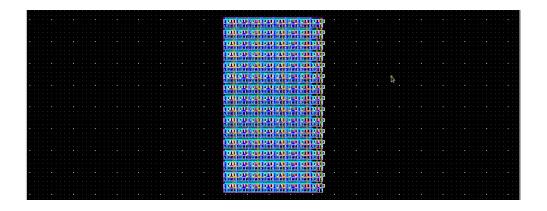

Figure 4. 3: DCV array layout

# 4.1.2 DCV2

Figure 4. 4: DCV2 layout

Figure 4. 5: DCV2 block layout.

Figure 4. 6: DCV2 array layout

# 4.1.3 Ring Oscillator

Figure 4. 7: Ring Oscillator layout

#### 4.1.4 Complete DCO

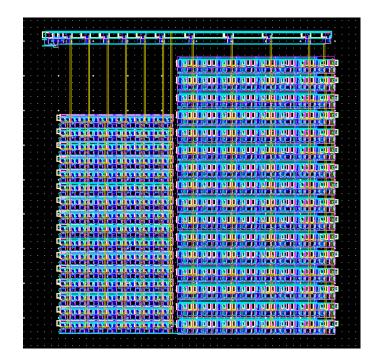

Figure 4. 8: Final DCO layout

The DCO range was from 3.33 ns to 10 ns of period (i.e. from 100 MHz to 300 MHz), but after constructing the layout directly without any modification to the sizing of DCVs or removing any fixed delay cells , the DCO range was from 11 ns to 16 ns (i.e. from 62.5 MHz to 90 MHz) which is out of our required range, so we had to remove the fixed delay cells (i.e. HDCs) but the range was still not satisfied, so we started to modify the length of the transistors in the DCV2 cells because the problem was with the lower bound of the required range (i.e. 100 MHz) and also increase the supply voltage source from 1.2v to 1.5v to satisfy the required range, and finally we have got 3.236 ns to 9.952 ns (i.e. 100.48 MHz to 309.02 MHz) as shown in figure 4.9.

Figure 4. 9: DCO operating range in layout.

## 4.2 PFD

Figure 4. 10: PFD layout

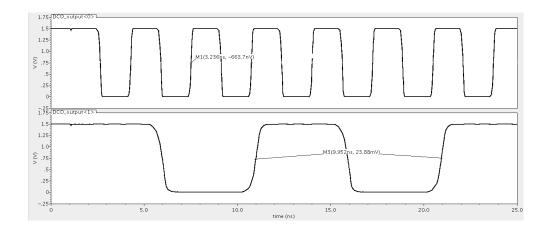

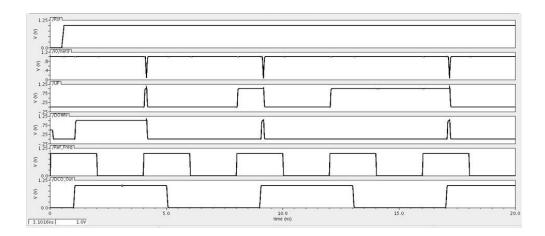

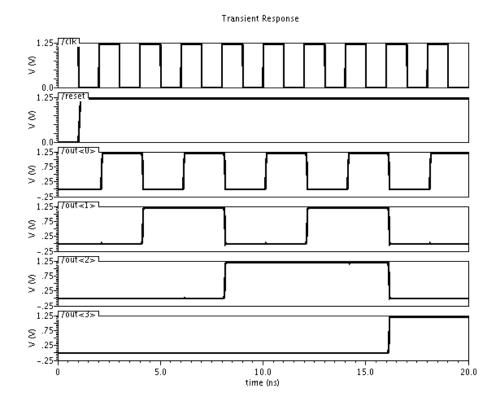

The proposed PFD consists of two D flip flop and OR gate. At the first time, when simulating the layout directly with power supply voltage 1.2v, we found that the functionality of the PFD is not working correctly, so we decreased the supply voltage to 1v and the PFD worked properly as shown in figure 4.10 and figure 4.11.

Figure 4.11: PFD pre-layout simulation.

Figure 4.12: PFD post-layout simulation.

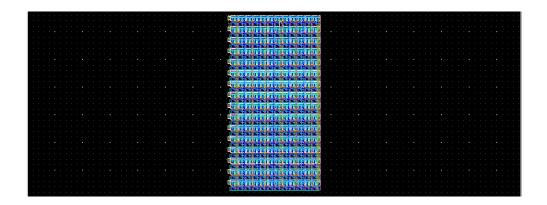

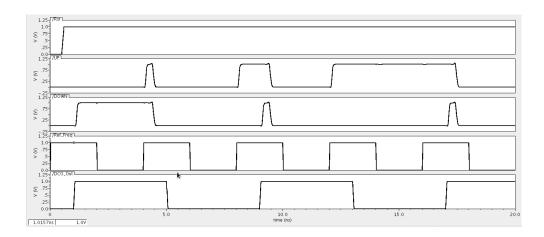

#### 4.3 Loop Filter

As mentioned earlier, the proposed Loop Filter in ADPLL is a shift register, which contains D FF's and some combinational blocks.

| • • | •   | •     | ·     | •    | •                  | • | • • | •    | ٠   | ٠    | ٠   | ٠  | ٠       | ٠  | ٠    | ٠  | ٠  | ٠  | •   | • • | • | •  | ٠   | •  | •  | •   | • | •   | •  | •          | ٠  | ٠ | • | ٠ | • | ٠     | ٠ | • • |   | • |

|-----|-----|-------|-------|------|--------------------|---|-----|------|-----|------|-----|----|---------|----|------|----|----|----|-----|-----|---|----|-----|----|----|-----|---|-----|----|------------|----|---|---|---|---|-------|---|-----|---|---|

| • • |     |       |       |      |                    |   |     |      |     |      |     |    |         |    |      |    |    |    |     |     |   |    |     |    |    |     |   |     |    |            |    |   |   |   |   |       |   |     |   |   |

|     | Ŧ   | - 1-1 | H     | ų,   | ij.                | Ð | M   | μŦ   | ١W  | Į,   | 4   | U, | þ       | W. | W.   | 44 | ηĄ | Ц  |     | 1   |   | ΗĐ | ij. | 61 | 19 | ЦJ. |   | i i | ٩Đ | <b>W</b> 1 | 府自 | - | М |   | H | i i i |   | d d | 1 |   |

|     | bi. |       | pi an | içka | e <mark>pto</mark> | 4 | 1   | 1972 | P m | al a | ft. | -  | a di ji | 14 | pine | ft | 7  | -1 | a e | P   |   | 3  |     |    |    |     | - |     | _  | D.         |    | ľ |   |   |   |       |   |     |   |   |

|     |     |       |       |      |                    |   |     |      |     |      |     |    |         |    |      |    |    | •  |     |     | 1 |    |     |    |    |     |   | 1   | -  |            |    |   |   |   |   |       |   |     |   |   |

| • • |     |       |       |      |                    |   |     |      |     |      |     |    |         |    |      |    |    |    |     |     |   |    |     |    |    |     |   |     |    |            |    |   |   |   |   |       |   |     |   |   |

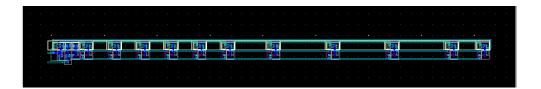

Figure 3.13: Shift Register layout

The post-layout simulation result was different from the pre-layout simulation due to the delay produced by the layout capacitance and resistance as shown in figure 4.12 and figure 4.13, but that is not a big deal. As we can see in figure 4.12 in the time period 2.5ns to 5ns the shift occurs at the positive edge of the CLK signal because the up and down signal are different, but in the same time slot in figure 4.13 the shift occurred once due to the delay produced by the layout.

Figure 4.14: Pre-layout simulation of the Shift Register

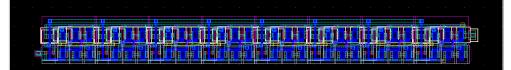

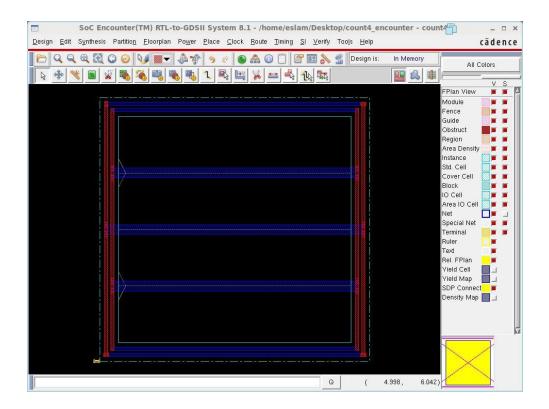

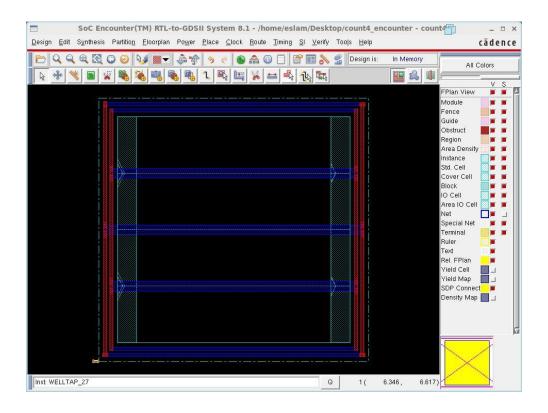

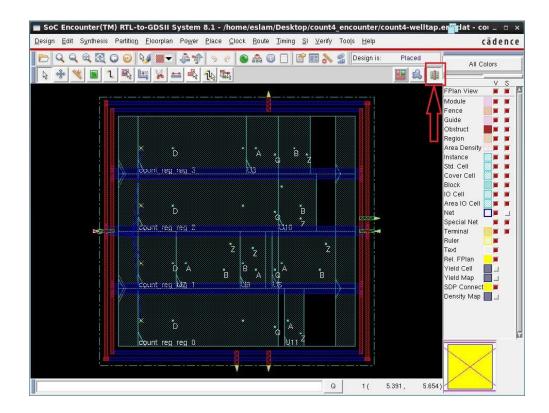

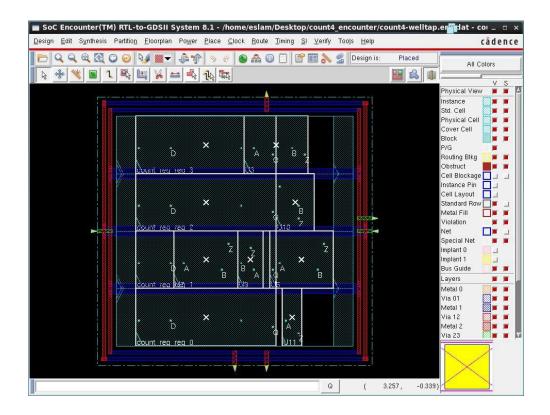

# 4.4 Overall Design

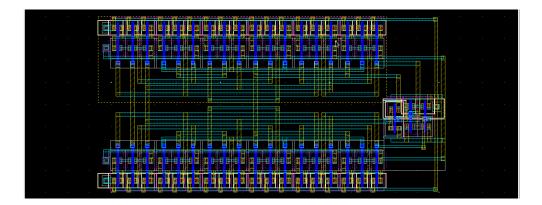

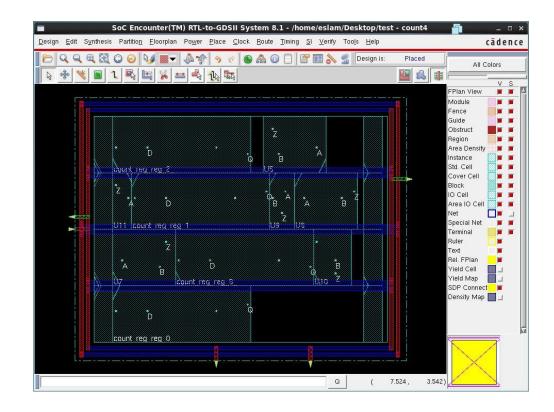

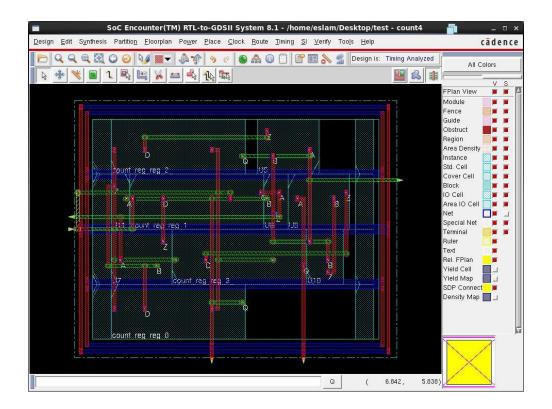

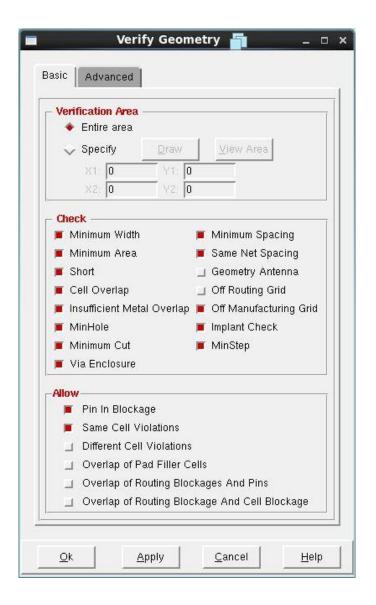

After constructing the layout of each block in the system, the layout of the overall design can be constructed as shown in figure 4.16

Figure 4.16: The overall layout

Figure 4.17: Overall post layout simulation

# 4.5 Conclusion

A comparison between the Required Specifications and Achieved Specifications is held as shown below

| <b>Required Specifications</b> | Achieved Specifications   |

|--------------------------------|---------------------------|

| Power < 1  mW                  | 0.6 mW                    |

| $Area < 0.01  mm^2$            | From Layout= $0.0086mm^2$ |

| Lock time $< 10  \mu s$        | 1 <i>µs</i>               |

| P-to-P jitter < 20 ps          | 35 ps                     |

#### References

- [1] Roland E. Best, "Phase Locked Loops, Design, simulation and applications 5<sup>th</sup> Edition" New York McGraw-Hill, 2003.

- [2] Duo Sheng, Ching-Che Chung and Chen-Yi Lee, "An Ultra-Low-Power and Portable Digitally Controlled Oscillator for SoC Applications" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 54, NO. 11, NOVEMBER 2007.

- [3] SALEH R. AL-ARAJI, ZAHIR M. HUSSAIN and MAHMOUD A. AL-QUTAYRI, "DIGITAL PHASE LOCK LOOPS, Architectures and Applications" Springer,2006.

- [4] Pao-Lung Chen, Ching-Che Chung, and Chen-Yi Lee "A Portable Digitally Controlled Oscillator Using Novel Varactors " IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 52, NO. 5, MAY 2005.

- [5] João Baptista Martins, Ricardo Reis and José Monteiro, "Capacitance and Power Modeling at Logic-Level".

- [6] CADENCE, "Virtuoso AMS Designer Environment Tutorials", 2008.

- [7] CADENCE, "Virtuoso AMS Designer Simulator User Guide", 2006.

- [8] CADENCE, "Virtuoso AMS Environment User Guide", 2006.

- [9] Alain Vachoux, "Top-Down Digital Design Flow" Version 6.0, October 2011.

- [10] Ahmed Ahmed, Hussein Mohamed, Khaled Ebrahim, Khaled Mohamed and Mohamed Sherif "All Digital Phase Locked Loop (ADPLL)", July 2013

### Appendix A

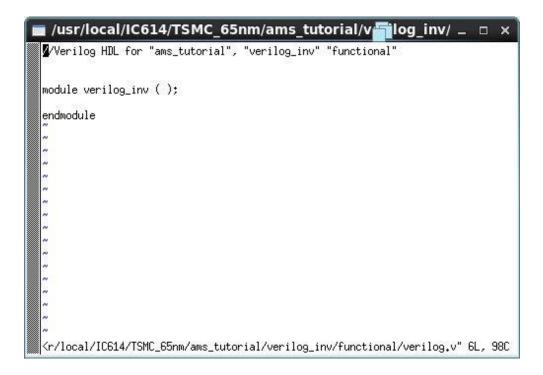

#### AMS TUTORIAL

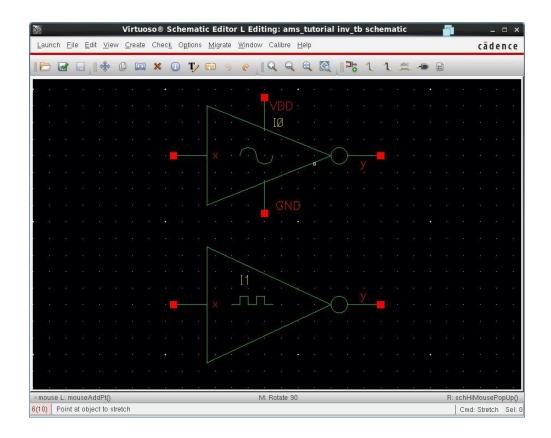

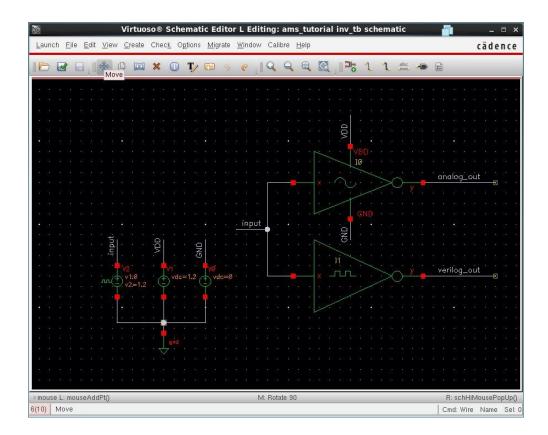

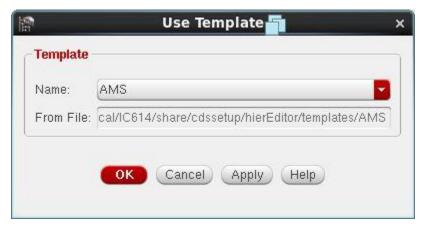

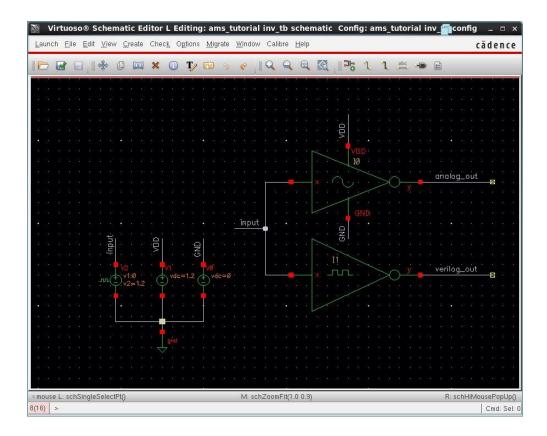

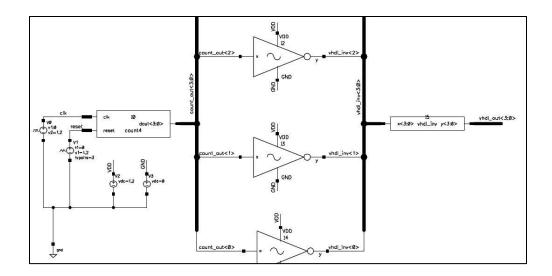

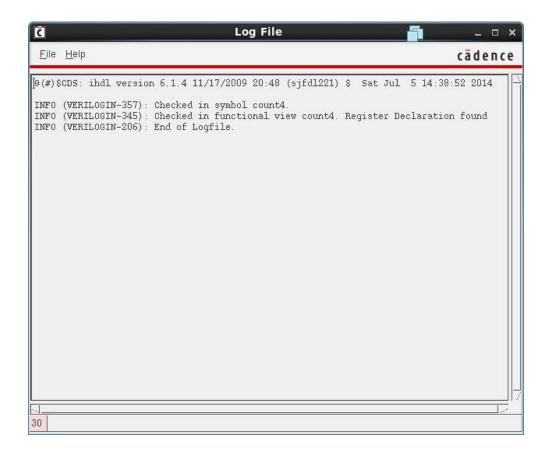

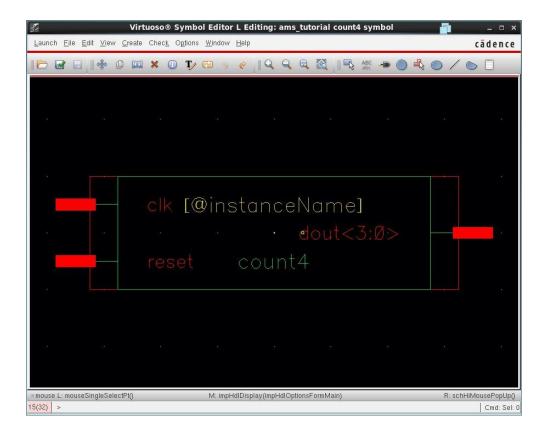

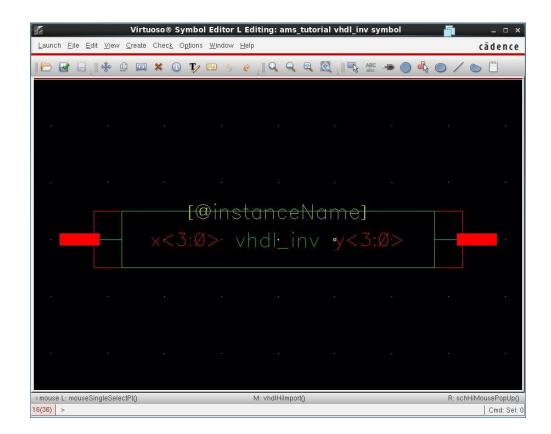

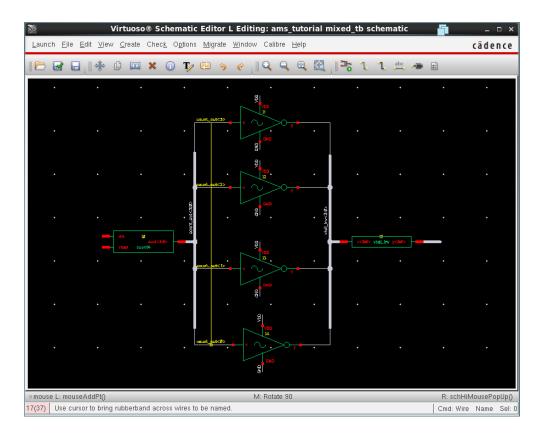

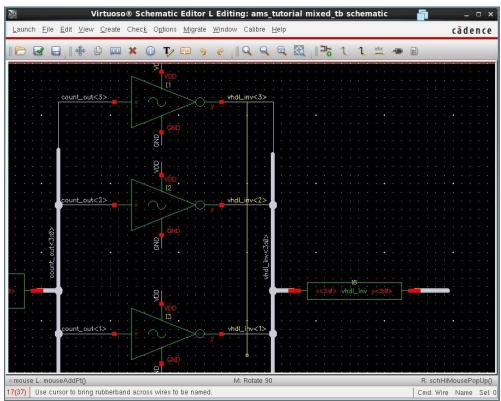

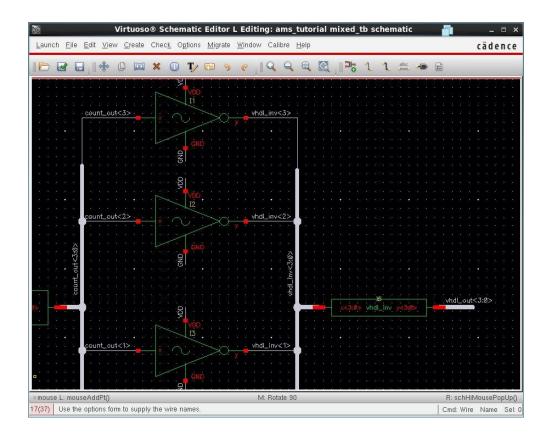

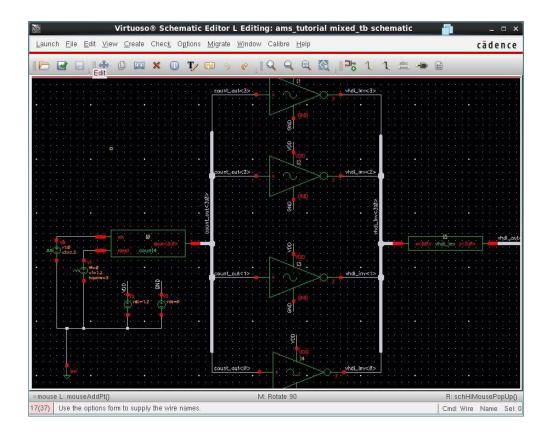

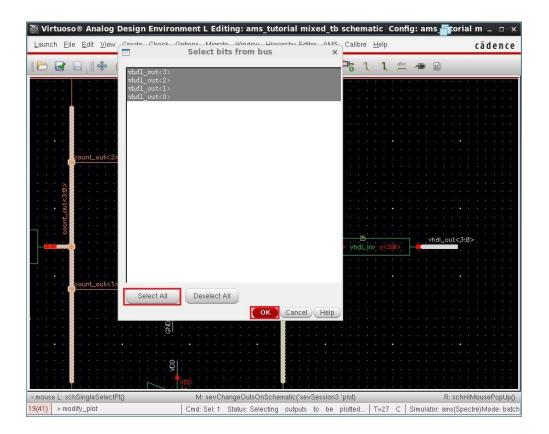

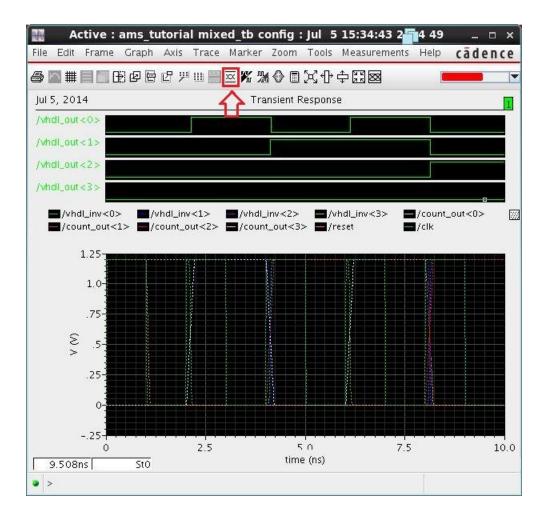

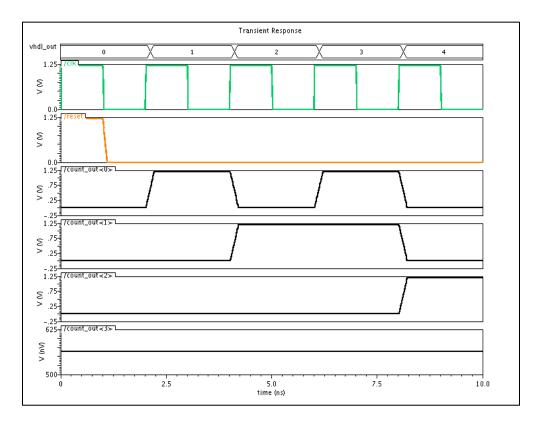

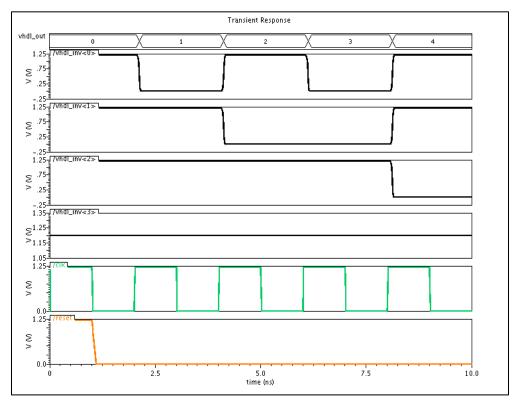

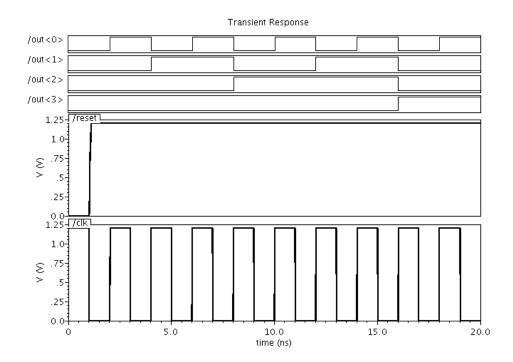

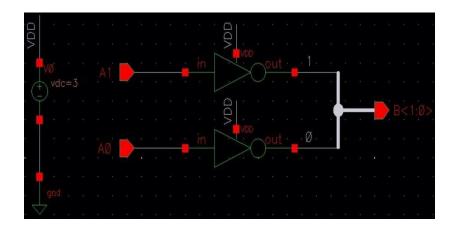

Through this tutorial you will learn how to simulate a system containing digital Verilog blocks, digital VHDL blocks and analog blocks. This tutorial is mainly divided into two parts, part 1 and part 2. For part 1, we are going to simulate a digital Verilog inverter with an analog inverter and compare the outputs of them, and then we put them in a cascaded configuration (analog inverter after digital Verilog inverter) to work together as a buffer. The idea of this cascaded configuration is to make sure that, the connect rules between the digital block and analog block are established correctly. For part 2, we are going to simulate another design contains three main blocks, a digital Verilog 4-bit counter, an analog 4-bit inverter and a digital VHDL 4-bit inverter. This design is organized as follows; an external clock signal and reset signal are applied to the Verilog 4-bit counter. The output of the Verilog 4-bit counter is labeled as  $count_out < 3:0 >$ and is applied as an input to the next block which is the analog 4-bit inverter. The output of the analog 4-bit inverter is labeled as vhdl\_inv<3:0> and is applied as an input to the last block which is VHDL 4-bit inverter. The output of the VHDL 4-bit inverter is labeled as vhdl\_out<3:0>. We are interested in these signals, count\_out<3:0>, vhdl\_inv<3:0> and vhdl\_out<3:0>. If everything is correct, the final output, vhdl\_out<3:0> will be the same as the counter output count\_out<3:0>. A block diagram for this design can be found in part 2 section.

#### Part1:

The following steps are to simulate both the digital Verilog inverter and the analog inverter and compare both outputs. Another configuration for these two inverters is to put them in cascade to work as a buffer. We use a library called ams\_tutorial to include all circuits in this tutorial.

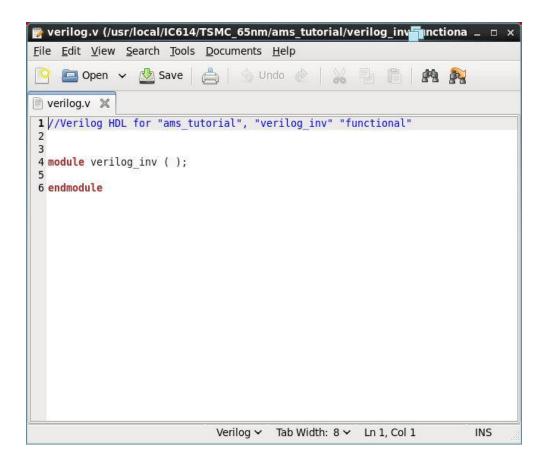

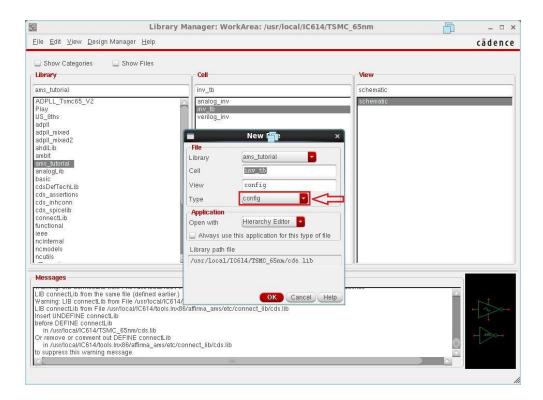

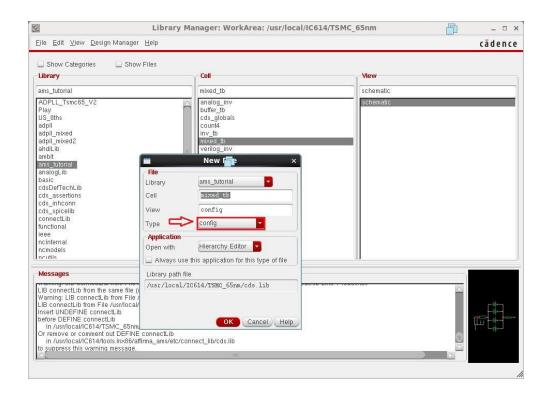

Firstly, we will make a cell view for the digital Verilog inverter.

| Library Manager: WorkArea: /usr/local/IC614/TSMC_65nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ×       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Elle Edit View Design Manager Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | cādence |

| New         Library           Open         Ctrl+O           Open (Bead-Only)         Ctrl+R           Category         Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| Load Defaults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| Ogen Shell Window Ctrl+P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| Egit Ctri+X<br>ambit<br>ams_utortal<br>analogLib<br>basic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

| CdSD#TechLib<br>Cds_assertions<br>Cds_inhcon<br>Cds_spicelib<br>connectLib<br>functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| ieee<br>ncinternal<br>ncmodels<br>ncutis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| Messages         LiB connectLib from the same file (defined earlier.)         Warning: LiB connectLib from File /usr/local/C614/TSMC_65nm/cds.lib Line 18 redefines         LiB connectLib from File /usr/local/C614/TSMC_65nm/cds.lib Line 18 redefines         LiB connectLib from File /usr/local/C614/TSMC_65nm/cds.lib         Insert UNDEFINE connectLib         in /usr/local/C614/TSMC_65nm/cds.lib         in /usr/local/C614/TSMC_65nm/cds.lib         in /usr/local/C614/TSMC_65nm/cds.lib         in /usr/local/C614/TSMC_65nm/cds.lib         to suppress this warning message. |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       |

|                   | New 🚰                                 | ×   |

|-------------------|---------------------------------------|-----|

| File              |                                       |     |

| Library           | ams_tutorial                          |     |

| Cell 🗢            | verilog_inv                           |     |

| View ->           | functional                            |     |

| Туре 🖚            | Verilog                               |     |

| Application       |                                       |     |

| Open with         | Read HDL                              |     |

| 🔲 Always use t    | his application for this type of file |     |

| Library path file |                                       |     |

| /usr/local/IC     | 614/TSMC_65nm/cds.lib                 |     |

|                   |                                       |     |

|                   |                                       |     |

|                   | OK Cancel H                           | elp |

After pressing the OK button, you'll get this menu

It is a little difficult to edit your code in this text editor so, we will use another text editor called "gedit" by typing the command **editor="gedit"** in the CIW window.

| Ĉ                                                                                      | Virtuoso® 6.1.4 - Log: /root/CDS.log | ×       |

|----------------------------------------------------------------------------------------|--------------------------------------|---------|

| <u>F</u> ile <u>T</u> ools <u>O</u> ptions So                                          | nnet TSMC PDK Tools <u>H</u> elp     | cādence |

| Loading schHDL.cxt<br>Warning: ams.env<br>Loading schematic.cxt<br>Loading ahdlSck.cxt |                                      |         |

| editor="gedit"<br>"mouse L:<br>1 >                                                     | M:                                   | R:      |

You can now see your cell view and double click on it to edit the code using gedit text editor

| 📓 🛛 Library Manage                                                                                                                                                                                                                                                                                                                                                                                            | er: WorkArea: /usr/local/IC614/TSMC_65nm     | 👘 💷 ×   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|

| Eile Edit ⊻iew Design Manager Help                                                                                                                                                                                                                                                                                                                                                                            |                                              | cādence |

|                                                                                                                                                                                                                                                                                                                                                                                                               | og_inv<br>og_inv<br>functional<br>functional |         |

| Messages<br>LIB connectLib from the same file (defined earlier.)<br>Warning: LIB connectLib from File /usr/local/C614/ToSMC_65<br>LIB connectLib from File /usr/local/C614/TosMC_65<br>linsert UNDEFINE connectLib<br>before DEFINE connectLib<br>in /usr/cal/C614/TSMC_65nm/cds.lib<br>Or remove or comment out DEFINE connectLib<br>in /usr/cal/C614/TSMC_65nm/cds.lib<br>Or suppress this warning message. | ams/etc/connect_llb/cds.llb                  |         |

A new window will open up after double clicking your cell view as follows:

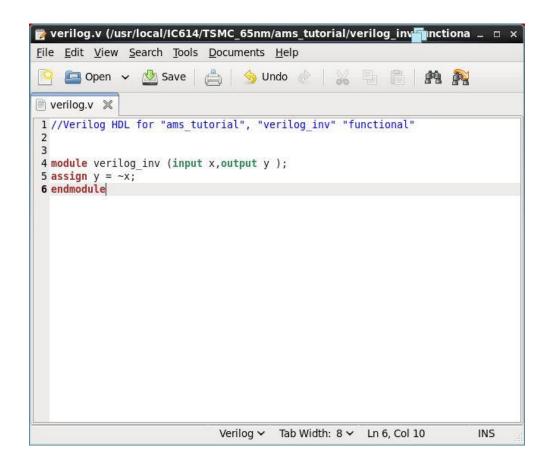

Edit the code and save it.

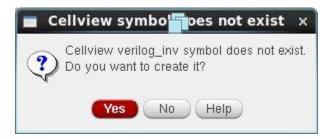

After closing it, you'll get a menu asking to create a symbol view for your circuit, press "yes".

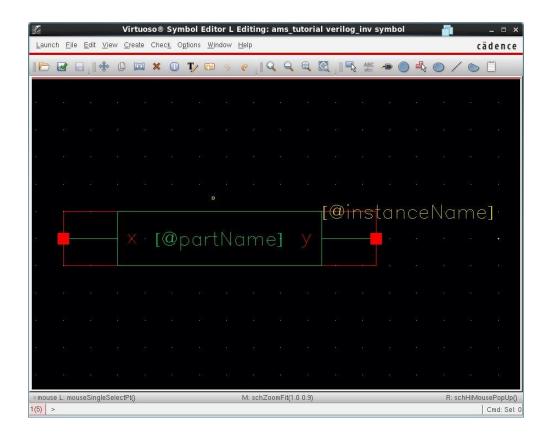

You can use the created symbol as is or edit it.

We will edit it to take the form of an inverter (optional step).

We put a something like square wave inside the symbol view to differentiate between it and the analog inverter. Now it is time to create the analog inverter.

|                  | New I                                | ×    |

|------------------|--------------------------------------|------|

| File             |                                      | -    |

| Library          | ams_tutorial                         |      |

| Cell             | analogLinv                           |      |

| View             | schematic                            |      |

| Туре             | schematic 🧧                          |      |

| Application      |                                      | -    |

| Open with        | Schematics L                         |      |

| 🔲 Always use     | this application for this type of fi | le   |

| Library path fil | e                                    |      |

| /usr/local/      | IC614/TSMC_65nm/cds.lib              |      |

|                  |                                      |      |

|                  |                                      |      |

|                  | OK Cancel H                          | Help |

| 5<br>Laund | ch <u>F</u> | ile  | Edit        | Vie   |            |        |                                      |              | hem   |              |          |   |            |                              |               | Calibre       |        |                           | ai u                  | nand | ·g_      |         | cine | anne     | ue        | -  |   |          |          | āde    |            |

|------------|-------------|------|-------------|-------|------------|--------|--------------------------------------|--------------|-------|--------------|----------|---|------------|------------------------------|---------------|---------------|--------|---------------------------|-----------------------|------|----------|---------|------|----------|-----------|----|---|----------|----------|--------|------------|

|            |             |      |             |       | -          |        | Insta                                |              |       | <u>p</u> uon | <u> </u> |   | • <u></u>  | indo<br>Ø                    |               |               |        | e<br>D                    | 8                     |      | JF.      | 1.      | 1    | ab       | ç ,       |    |   |          |          | aue    | : 11 0     |

|            | •           |      | 9<br>9<br>9 |       |            | 1      | <u>W</u> ire<br>Wire<br>Wire         | (wi <u>d</u> | e)    | W<br>Sł      | nift+V   | v |            |                              | /DI           |               |        | •                         |                       |      |          | 4       |      | 30<br>20 |           | 19 |   | 8        | 2<br>10  | -25    | -          |

|            |             |      |             |       |            |        |                                      | Expre        | ssion | P            |          |   |            |                              |               | 1             |        |                           |                       |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        | <u>B</u> loc<br><u>C</u> ell<br>Sold | view         |       | В            |          | • | F          | rom (                        | <u>C</u> ellv | iew           |        | /i<br>'pcl                |                       |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        | <u>N</u> ote<br>Pa <u>t</u> cl       | hcor         |       |              |          | • |            | rom <u>F</u><br>rom <u>I</u> |               |               |        | v=4<br>/DD<br>:60         | ØØ                    |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       | 8)<br>8)   | 1      | Pr <u>o</u> b<br>M <u>u</u> lti      | Shee         |       |              |          | • |            |                              |               | y             | f<br>S | ing<br>simi               | ers:<br>M;1           |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       | 10<br>20   |        | CP <u>F</u>                          | NetS         | iets  | -<br>-       | ×        |   | •          |                              |               |               | •      |                           |                       |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        |                                      |              |       |              |          |   |            |                              |               | nch<br>y<br>x |        | ncl<br>v:2                | ØØ⊓                   |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        |                                      |              |       |              |          |   |            |                              |               | GNĎ           |        | GND<br>:60<br>ing<br>simi | n <sup>.</sup><br>ers |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        |                                      |              |       |              |          |   |            |                              |               |               |        | ata                       |                       |      |          |         |      |          |           |    |   |          |          |        |            |

|            |             |      |             |       |            |        |                                      |              |       |              |          |   |            |                              |               |               |        |                           |                       |      |          |         |      |          |           |    |   |          |          |        |            |

|            | d.          | 12   | 8           |       | 84.<br>181 | 4<br>3 | 8                                    | s:<br>p      | ŝ     | 10<br>10     | 8        |   | 24.<br>28. | 33                           | 91            | Ð             | a.     | 64).<br>181               |                       | 91.  | 20<br>30 | с.<br>С | 10   | 2        | 74<br>(†1 | 10 | 8 | 93<br>93 | 20<br>20 | a<br>a | 40.<br>12. |

| mous       | e L: m      | ious | eAd         | :Pt() |            |        |                                      |              |       |              |          |   |            |                              | M: F          | Rotate        | 90     |                           |                       |      |          |         |      |          |           |    | F | l: sch   | HiMo     | ouseP  | opU        |

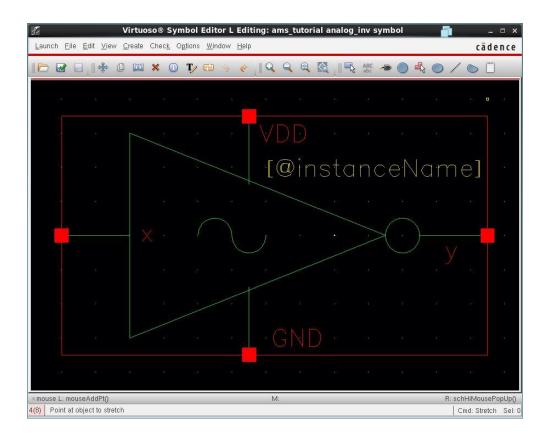

To create a symbol choose, **Create > cellview > from cellview** as follows

## Press ok for the next window

|                  | Cellview From Cellview 📑 | ×          |

|------------------|--------------------------|------------|

| Library Name     | ams_tutorial             | Browse     |

| Cell Name        | analog_inv               |            |

| From View Name   | schematic                |            |

| To View Name     | symbol                   |            |

| Tool / Data Type | schematicSymbol          |            |

| Display Cellview | ✓                        |            |

| Edit Options     | ⊻                        |            |

|                  |                          |            |

|                  | OK Cancel Defaults       | Apply Help |

|                 | Sy                 | mbol Gene | eration Option | າຣ        | ×           |  |  |

|-----------------|--------------------|-----------|----------------|-----------|-------------|--|--|

| Library Name    |                    | Cell Name |                | View Name |             |  |  |

| ams_tutorial    | -                  | analog_in | 7              | symbol    |             |  |  |

| Pin Specificati | ons                |           |                |           | Attributes  |  |  |

| Left Pins       | x                  | List      |                |           |             |  |  |

| Right Pins      | У                  |           |                |           | List        |  |  |

| Top Pins        | ממע                |           |                |           | List        |  |  |

| Bottom Pins     | GND                |           |                |           | List        |  |  |

| Exclude Inheri  | ted Connection Pir | ns:       |                |           |             |  |  |

| 🖲 None 🔾        | All 🔾 Only thes    | е:        |                |           |             |  |  |

| Load/Save 📃     | Edit Attril        | outes 🗔   | Edit Labels    | Edit P    | roperties 🗔 |  |  |

|                 |                    |           | ОК             | Cancel A  | Apply Help  |  |  |

We will edit the symbol view to looks like the following (optional). We put a something like a sine wave inside the symbol to differentiate it from the digital inverter.