# LTE-UE-L1-Processing-On-Parallela

By

Basma Magdy Hussien Ali

Dina Magdy Mohamed Mohamed

Omayma Gomaa Abdelazem

Somaia Hussien Rashad Mohamed

A Thesis submitted to the Faculty of Engineering at Cairo University In partial fulfilment of the requirements For the Degree of Bachelor of Science in ELECTRONICS AND ELECTRICAL COMMUNICATION ENGINEERING

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT

2016

# LTE-UE-L1-Processing-On-Parallela

By

Basma Magdy Hussien Ali

Dina Magdy Mohamed Mohamed

Omayma Gomaa Abdelazem

Somaia Hussien Rashad Mohamed

Under the Supervision of

Dr. Ahmed Hesham

Dr. Hassan Mostafa

A Graduation Project Report Submitted to the Faculty of Engineering at Cairo University In Partial Fulfillment of the Requirements for the

Degree of

Bachelor of Science

in

Electronics and Communications Engineering

Faculty of Engineering, Cairo University

Giza, Egypt

July 2016

# **Table of Contents**

| List of T | `ables viii                                  |

|-----------|----------------------------------------------|

| List of F | igures ix                                    |

| List of S | ymbols and Abbreviations xi                  |

| Acknow    | ledgments xii                                |

| Abstract  |                                              |

| Chapter   | 1: Introduction0                             |

| 1.1       | Problem Definition                           |

| 1.2       | Problem Solution with Project Provides       |

| 1.3       | Requirements 3                               |

| 1.4       | Project Vision                               |

| Chapter   | 2: Parallella 4                              |

| 2.1       | Overview                                     |

| 2.2       | Parallella System Architecture               |

| 2.2.      | .1 Zynq Memory Map 6                         |

| 2.2.      | .2 Epiphany Memory Map7                      |

| 2.3       | Parallella Features Description              |

| 2.3       | .1 CPU                                       |

| 2.3       | .2 Epiphany Coprocessor                      |

| 2.3       | .3 SDRAM10                                   |

| 2.3       | .4 LED Indicators                            |

| 2.3       | .5 Serial Port11                             |

| 2.3       | .6 Powering the Board11                      |

| 2.4       | Parallella Start & Booting11                 |

| Chapter   | 3: Epiphany SDK14                            |

| 3.1       | Introduction14                               |

| 3.1       | .1 SDK (Software Development Kit) Overview14 |

| 3.1.2              | Epiphany Memory Model                    | 15 |

|--------------------|------------------------------------------|----|

| 3.1.3              | Epiphany Programming Framework           | 16 |

| 3.2 B              | uilding SDK                              | 17 |

| 3.2.1              | Building Steps                           | 17 |

| 3.2.2              | Building check                           | 19 |

| 3.3 E <sub>l</sub> | piphany SDK Tool chain                   | 20 |

| 3.3.1              | C/C++ Compiler (E-GCC)                   | 20 |

| 3.3.2              | Linker (E-LD)                            | 21 |

| 3.3.3              | Instruction Set Simulator (E-Run)        | 23 |

| 3.3.4              | Debugger (E-GDB)                         | 24 |

| 3.3.5              | Hardware Connection Server (E-SERVER)    | 27 |

| 3.4 Ej             | piphany SDK utilities (E-UTILS)          | 28 |

| 3.4.1              | Introduction                             | 28 |

| 3.4.2              | Reset Utility (E-RESET)                  | 29 |

| 3.4.3              | Loader Utility (E-LOADER)                | 29 |

| 3.4.4              | Memory Read Utility (E-READ)             | 30 |

| 3.4.5              | Memory Write Utility (E-WRITE)           | 30 |

| 3.5 Ej             | piphany Hardware Utility Library (e-Lib) | 31 |

| 3.6 Ej             | piphany Host Library (eHAL)              | 32 |

| Chapter 4:         | Frame Structure                          | 33 |

| 4.1 In             | troduction                               | 33 |

| 4.2 Fr             | rame Structure Type 1                    | 35 |

| 4.3 Fr             | rame Structure Type 2                    | 39 |

| 4.4 D              | ownlink Frame Structure                  | 42 |

| 4.5 U              | plink Frame Structure                    | 43 |

| Chapter 5:         | Fixed Point Representation               | 45 |

| 5.1 M              | lotivation                               | 45 |

| 5.2 W      | Vays of Fixed Point Representation              | 46 |

|------------|-------------------------------------------------|----|

| 5.2.1      | Sign/magnitude                                  | 46 |

| 5.2.2      | One's complement                                | 46 |

| 5.2.3      | Two's complement                                | 47 |

| 5.3 Q      | -Format number representation                   | 47 |

| 5.4 C      | onverting Floating Point to Fixed Point Example | 49 |

| Chapter 6: | Scrambler                                       | 51 |

| 6.1 In     | troduction                                      | 51 |

| 6.2 In     | nplementation ways:                             | 52 |

| Chapter 7: | Modulation & Precoder                           | 58 |

| 7.1 In     | troduction:                                     | 58 |

| 7.1.1      | QPSK                                            | 59 |

| 7.1.2      | 16QAM                                           | 59 |

| 7.1.3      | 64QAM                                           | 60 |

| 7.2 In     | nplementation Ways                              | 60 |

| 7.3 Pi     | recoder                                         | 62 |

| Chapter 8: | DFT                                             | 64 |

| 8.1 In     | troduction                                      | 64 |

| 8.2 In     | nplementation way                               | 64 |

| 8.2.1      | Theory and Output Generated Signals             | 64 |

| 8.2.2      | Error Measurement Ways                          | 68 |

| 8.2.2      | 2.1 Comparing the Constellations                | 68 |

| 8.2.2      | 2.2 Calculating SNR                             |    |

| 8.2.2      | 2.3 Calculating EMV                             |    |

| 8.3 IF     | ŦT                                              | 70 |

| Chapter 9: | Hardware Prototype                              | 73 |

| 9.1 M      | lotivation                                      | 73 |

| 9.2 Fi     | reeRTOS                                         | 73 |

| 9.2.1       | Background                                | 73  |

|-------------|-------------------------------------------|-----|

| 9.2.2       | Problem formulation                       | 74  |

| 9.2.3       | Message                                   | 75  |

| 9.2.4       | Message-passing between Cores             | 75  |

| 9.2.4.      | 1 FreeRTOS Queues                         | 76  |

| 9.2.4.2     | 2 Creating the Message Box                | 77  |

| 9.2.4.2     | 3 Mutual Exclusion                        | 78  |

| 9.2.5       | Simulation                                | 78  |

| 9.2.6       | Hardware                                  | 79  |

| 9.3 AR      | M Cross Compiler                          | 79  |

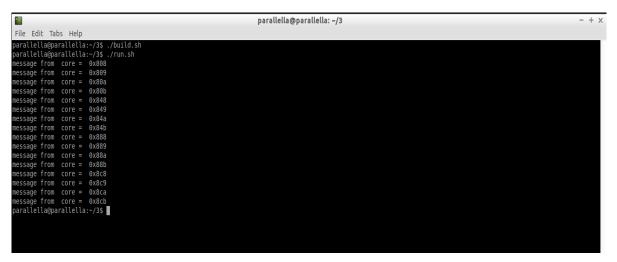

| 9.4 He      | llo world on epiphany core                | 80  |

| 9.4.1       | Introduction                              | 80  |

| 9.4.2       | Implementation                            | 80  |

| 9.4.3       | Results:                                  | 82  |

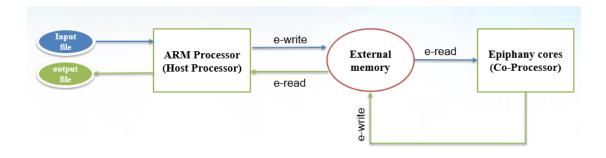

| 9.5 Tes     | st Functionality of Communication Blocks  | 82  |

| 9.5.1       | Introduction                              | 82  |

| 9.5.2       | Modulation block                          |     |

| 9.5.3       | Scrambler & DFT Blocks                    |     |

| 9.6 Op      | timization Levels                         | 84  |

| 9.6.1       | Introduction                              | 84  |

| 9.6.2       | Running each Block on Single Core         | 84  |

| 9.6.3       | Running all Blocks on 12-core in parallel | 84  |

| Conclusion. |                                           | 86  |

| Future Work | ζ                                         |     |

| References  |                                           |     |

| Appendix I  | Supported Tutorials                       | 90  |

| Appendix II |                                           | 91  |

| Appendix II | I Budget                                  | 116 |

# List of Tables

| Table 1-1: Comparison between different systems architecture and epiphany system | ı 4 |

|----------------------------------------------------------------------------------|-----|

| Table 2-1: Parallella Feature Summary                                            | 5   |

| Table 2-2: Zynq Memory Map                                                       | 8   |

| Table 2-3: Epiphany Memory Map                                                   | 9   |

| Table 3-1: General Compiler Options                                              | .21 |

| Table 3-2: Optimization Options                                                  | .21 |

| Table 3-3: Memory Management Scenarios                                           | .24 |

| Table 3-4: Linker Sections                                                       | .24 |

| Table 3-5: Simulator Command Line Options                                        | .25 |

| Table 3-6: Debugger Command Line Options                                         | .28 |

| Table 3-7: eServer Command Line Options                                          | .29 |

| Table 3-8: Loader Command Line Options                                           | .30 |

| Table 3-9: e-read Command Line Options                                           | .31 |

| Table 3-10: e-write Command Line Options                                         | .32 |

| Table 4-1: Frame units V.S. their times                                          | .35 |

| Table 4-2: Cyclic Prefix Types V.S Lengths                                       | .37 |

| Table 4-3: Subcarriers, Resource blocks corresbonding to the B.W                 | .39 |

| Table 4-4: Open Source LTE survey                                                | .42 |

| Table 7-1: The number of bits corresbonding to each modulation scheme            | .60 |

| Table 7-2: QPSK modulation mapping                                               | .60 |

| Table 7-3: 16-QAM modulation mapping                                             | .61 |

| Table 8-1: IFFT Sizes Corresponding to each B.W                                  | .72 |

# List of Figures

| Figure 1-1: CDMA voice call vs. VoIP                                             | 2 |

|----------------------------------------------------------------------------------|---|

| Figure 2-1: Parallella board (top view).                                         | 5 |

| Figure 2-2: Parallella board (bottom view).                                      | 5 |

| Figure 2-3: Zynq connectivity diagram.                                           | 7 |

| Figure 2-4: Parallella accessories12                                             | 2 |

| Figure 2-5: Login in Parallella1                                                 | 3 |

| Figure 3-1: Epiphany SDK14                                                       | 1 |

| Figure 3-2: Epiphany Program build flow1                                         | 7 |

| Figure 3-3: Simulate Hello-World simple code19                                   | 9 |

| Figure 3-4: The eServer Client-Target Connection Concept2                        | 7 |

| Figure 4-1: PUSCH Bit Processing Chain                                           | 3 |

| Figure 4-2: PUSCH Symbol Processing Chain                                        | 3 |

| Figure 4-3: FDD Frame Structure Type 1                                           | 5 |

| Figure 4-4: Uplink resource grid30                                               | 5 |

| Figure 4-5: LTE FDD Frame of 1.4 MHz, Normal CP                                  | 3 |

| Figure 4-6: TDD Frame Structure type 2                                           | 3 |

| Figure 4-7: LTE resource grid for FDD4                                           | 1 |

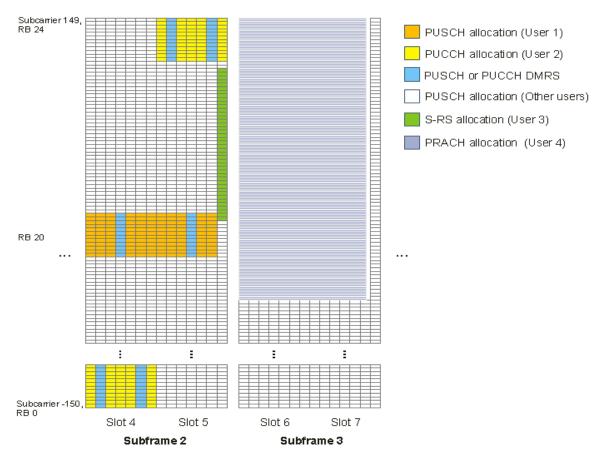

| Figure 4-8: LTE Uplink Subframe 2-3 of 5 MHz, Normal CP                          | 1 |

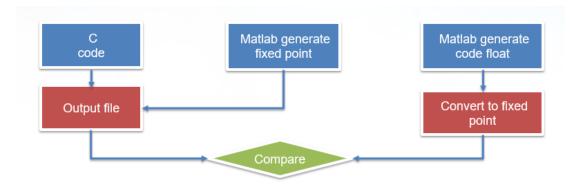

| Figure 5-1: Progress of implement the codes of blocks to generate test cases     | 3 |

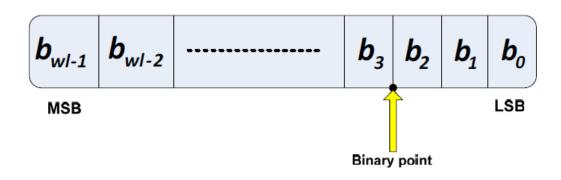

| Figure 5-2: Showing How the conversion of floating point to fixed point happens5 | 1 |

| Figure 6-1: The output From Scrambler Code Versus Test cases                     | 7 |

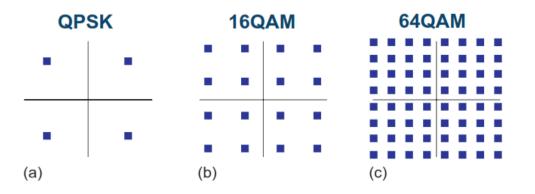

| Figure 7-1: Signal constellations for: (a) QPSK; (b) 16QAM; (c) 64QAM60          | ) |

| Figure 7-2: The output From Modulation Code Versus Test case                     | 1 |

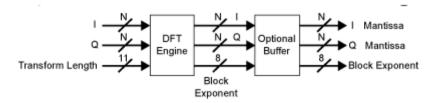

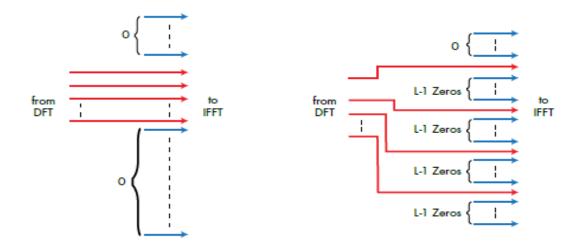

| Figure 8-1: shows the DFT/IDFT reference design blocks6                          | 5 |

| Figure 8-2: The output from DFT code versus test cases                           | 3 |

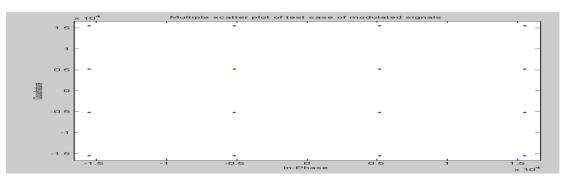

| Figure 8-3: constellation plot of test case of modulated signals6                | 3 |

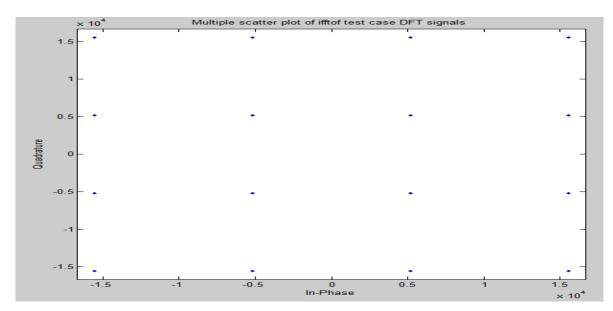

| Figure 8-4: constellation plot of IFFT of test case DFT signals69                | ) |

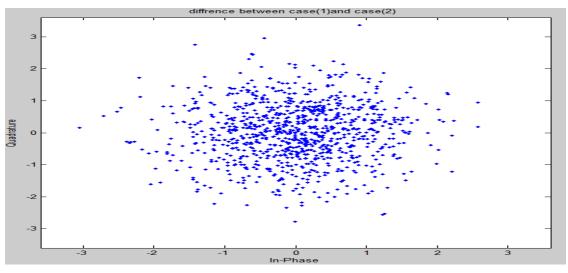

| Figure 8-5: Difference between case 1 and case 269                               | ) |

| Figure 8-6: Localized Mapping V.S. Distributed Mapping72                         | 2 |

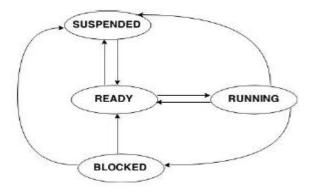

| Figure 9-1: State diagram of FreeRTOS tasks [12]74                               | 1 |

| Figure 9-2: Hello-world with ARM cross compiler                                  | ) |

| Figure 9-3: The way to Implement code on single core on parallella               | 82 |

|----------------------------------------------------------------------------------|----|

| Figure 9-4: The way to Implement code on single core on parallella               | 83 |

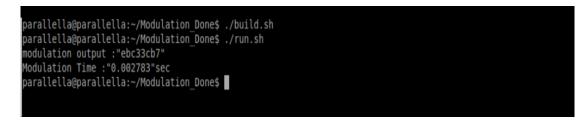

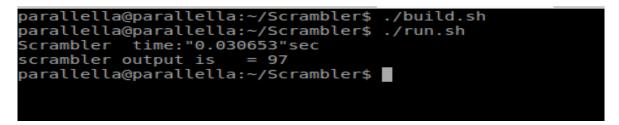

| Figure 9-5: First modulation output and time consumption                         | 83 |

| Figure 9-6: First scrambler output and time consumption                          | 83 |

| Figure 9-7: First DFT output and time consumpion                                 | 85 |

| Figure 9-8: First output and time of each block and over all time of application | 85 |

| Figure 9-9: First DFT output and over all time of application                    | 85 |

# List of Symbols and Abbreviations

| LTE                              | The Long-Term Evolution                                     |  |  |

|----------------------------------|-------------------------------------------------------------|--|--|

| 3GPP                             | the Third Generation Partnership Project                    |  |  |

| GPP                              | general purpose processor                                   |  |  |

| VOLTE                            | voice over LTE                                              |  |  |

| NoC                              | Network-on-Chip                                             |  |  |

| UE                               | User Equipment                                              |  |  |

| L1                               | Physical Layer                                              |  |  |

| SDK                              | Software Development Kit                                    |  |  |

| $M_{\rm sc}^{\rm PUSCH}$         | Scheduled bandwidth for uplink transmission, expressed as a |  |  |

|                                  | number of subcarriers                                       |  |  |

|                                  |                                                             |  |  |

| M <sup>PUSCH</sup> <sub>RB</sub> | Scheduled bandwidth for uplink transmission, expressed as a |  |  |

| KB                               | number of resource blocks                                   |  |  |

| $Q_m$                            | Modulation order: 2 for QPSK, 4 for 16QAM and 6 for 64QAM   |  |  |

|                                  | transmissions                                               |  |  |

| PUSCH                            | Physical Uplink Shared Channel                              |  |  |

| RB                               | Resource Block                                              |  |  |

| СР                               | Cyclic Prefix                                               |  |  |

| MIMO                             | Multi Input Multi Output                                    |  |  |

| PA                               | Power Amplifier                                             |  |  |

# Acknowledgments

First of all, we would like to express our deep sense of respect and gratitude towards our advisors and guides DR. Ahmed Hesham and DR. Hassan Mostafa for their continuous support, advice, and guidance throughout our work.

We are grateful to AXXCELERA EGYPT for supporting some of Graduation Projects for the first year.

Next, we want to express our respects to Eng. Mohamed Taha, Eng. Karim Osama, Eng. Wael Elbreqy, and other Technical References from AXXCELERA EGYPT for their great effort support.

Great thanks to our parents who support us with their valuable patience and love.

# Abstract

As the ubiquitous wireless communication devices consume a lot of processing power, therefore we need to decrease the power consumed by LTE processing units in UEs, also decrease the development time while increasing the throughput the thing that maximize the performance.

The main purpose of that project is to compare experimentally between the power consumption of general purpose processor (GPP) such as Parallella platform and Digital Signal processor (DSP).

The experimental results are collected from Parallella board containing epiphany system of 16 cores and compared with past results found in literature regarding DSP's used in communication applications. The results show that the Parallella board consumes 92 % less power than the DSP.

Therefore, we can consider Parallella platform as a good prototype which minimize power consumption and achieve high performance.

In this documentation we can find the illustration of each block of symbol chain and all experiments which have been done to achieve high level of optimization such as power and time optimization.

# Chapter 1: Introduction

#### **1.1 Problem Definition**

We can say we have enormous mobile data revolution, to adapt the mass-market expansion of smart phones, tablets, notebooks, and laptop computers. This great growth in data mobile services and applications such as Video streaming, social networking and Web browsing, will develop the next generation of wireless standards and also becomes a very great force for the development. As a result, new standards are evolved to provide network capacity and data rates necessary to support worldwide delivery of these types of rich multimedia application.

Nowadays, it is important to understand how cellular systems have developed and also to understand the mobile-communication systems, its complexity and from where they came. The task of developing mobile technologies has also changed, from regional or national concern, to become an increasingly complex task controlled by the global organizations for developing standards such as the "3GPP" (Third Generation Partnership Project) and involving thousands of people.

Mobile communication technologies have a lot of generations, started from 1G which is analog mobile radio system, 2G which is considered the first digital mobile system, and 3G which is the first mobile system used to handle the broadband data. And finally The LTE (Long-Term Evolution) and it's commonly called "4G", but actually it's 3.9G and the upgrade of it is called LTE-Advance and it's actually the 4G. This continuing race of increasing sequence numbers of mobile system generations is in fact just a matter of labels.

LTE and LTE-Advanced have been developed to realize the goal of achieving global broadband mobile communications and to respond to the requirements of this area. The objectives and goals of this developed system include higher radio access data rates, improved system capacity and coverage, flexible bandwidth operations, significantly improved spectral efficiency, low latency, reduced operating costs, multi-antenna support, and seamless integration with the Internet and existing mobile communication systems. So as obvious LTE phones are fast, but the battery is sucked quickly in just some few hours, based on some studies made by Nokia Siemens Networks, they found that LTE devices consume from 5 percent to 20 percent more than previous-generation phones, and also it depends on the used application. In Samsung Galaxy Nexus' review, they found that the Google Navigation running over the LTE network ate battery power faster than the Nexus' car charger could restore it [34].

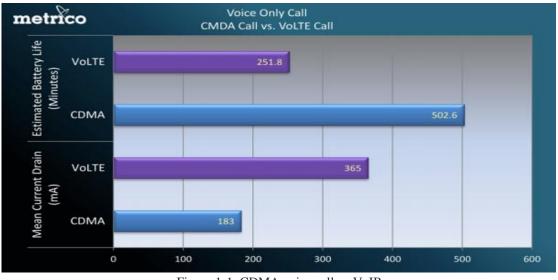

Every mobile carrier wants to replace their old voice services with new VoIP-based systems utilizing their 4G networks, but it looks like they've got some big kinks to iron out in the technology first. Wireless testing and measurement vendor Spirent Communications has identified a big problem with voice over LTE (VoLTE): it consumes twice as much power as a traditional 2G call, which could have big implications for mobile phone battery life.

Metrico Wireless, a radio field testing company Spirent acquired in September, conducted voice trials on a commercial VoLTE-enabled network in two U.S. cities, comparing the power consumption of VoIP calls made over LTE against the power used by the same carrier's CDMA systems as shown on Figure (1-1) [33].

Figure 1-1: CDMA voice call vs.VoIP

It's important to know why LTE is considered battery killer, the first reason is **Phones with LTE has rabbit ears,** All LTE devices sold today use a technology called MIMO, which doesn't just send or receive a single signal, but rather multiple parallel transmissions. Today's devices support two such paths – future devices will support more — which means each phone has two antennas,

each of which requires its own power amplifier. Another reason for LTE to be greedy that LTE devices are co-dependent. Phone screen may be dark, but phone is constantly pining for the network. That means it's periodically scans the airwaves around it to determine which tower it should tether itself to. The more networks there are to choose from the more scans it must make. With the typical operator sporting some combination of GSM, HSPA, CDMA and EV-DO systems —often multiple version of each in different frequency bands — there are a lot of other networks for an LTE device to flip between.

So the major ultimate goal of LTE L1 processing in UEs is to provide maximum performance while consuming minimal power. A lot of platforms are optimized to achieve this goal but there still some challenges in this area, like achieving 64QAM while minimizing the processing power.

#### **1.2 Problem Solution with Project Provides**

Implementing LTE UE-L1 processing on a system with many-cores general-purpose processors (GPP) will decrease both the cost and development time, plus it is eco-friendlier as it will consume less power than the complex DSP processors using now in implementing LTE.

To evaluate implementing LTE UE-L1 processing on GPP platform, we introduce the Epiphany system which consists of GPP clustered in a Network-on-Chip (NoC) that range from 4x4 to 64x64 cores. The Epiphany combines fully-featured floating point C/C++ programmable RISC processors, as each core has separate CPU, each CPU can run a separate and independent program (MIMD not SIMD).

Epiphany introduces a high bandwidth distributed memory system, a low latency Network-On-Chip, and low overhead off-chip IO to bring an unprecedented level of processing to power constrained systems. Table (1-1) below show comparison between Architecture Comparison of different systems and epiphany systems.

| Technology     | FPGA  | DSP       | Epiphany  |

|----------------|-------|-----------|-----------|

| Process        | 28nm  | 40nm      | 28nm      |

| Programming    | VHDL  | OCL/C++/C | OCL/C++/C |

| Area (mm^2)    | 590   | 108       | 10        |

| Chip Power (W) | 40    | 22        | 2         |

| Compile Time   | Hours | Minutes   | Minutes   |

| L1 Memory      | 6MB   | 512KB     | 2MB       |

Table 1-1: comparison between different systems architecture and epiphany systems.

### **1.3 Requirements**

It is required to evaluate the feasibility of implementing one of the LTE UE-L1 (R10) data processing chains (PDSCH or PUSCH) on the Epiphany system represented by parallella platform which consist of 16 epiphany co-processors.

The following steps are required to achieve this:

- 1-Study the LTE UE-L1 system (PDSCH and/or PUSCH), and choose a design that would maximize parallelization gain.

- 2-Choose the blocks that will be implemented.

- 3-Implement C code for these blocks as processing kernels.

- 4-Port these kernels as jobs for the processing cores on the HW platform.

- 5-Synchronize between those jobs running on different cores.

- 6-Implement a testing mechanism that would involve LTE transmission on wire (Ethernet).

#### 1.4 Project Vision

The vision of the company on the long term to use the platform prototype as a complete transmitter of LTE system using min power and with high rate. That low power consumption will help in the far places which is hard to be supported by huge amount of power ex the submarines in petroleum field where I need to coverage it with efficient communication system, low power consumption and far periodic maintenance planning (cost).

# Chapter 2: Parallella

# 2.1 Overview

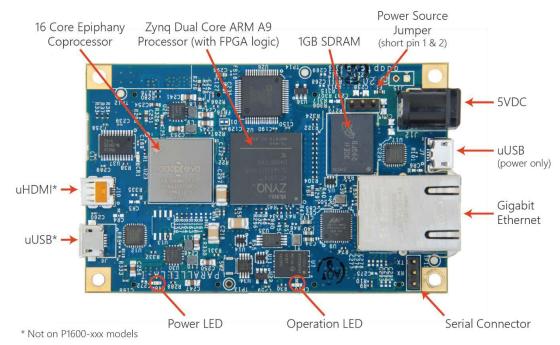

Parallella board is a high performance computing platform based on a dual-core ARM-A9 Zynq System-On-Chip and Adapteva's Epiphany multicore coprocessor. Current commercially available models Table (2-1):

| Model                     | P1600             | P1601                        | P1602                        |  |

|---------------------------|-------------------|------------------------------|------------------------------|--|

| Mnemonic                  | "Microserver"     | "Desktop"                    | "Embedded"                   |  |

| Host                      | Xilinx Zynq D     | ual-core ARM A9              | Xilinx Zynq Dual-core ARM A9 |  |

| Processor                 | XC7Z0             | 010                          | XC7Z020                      |  |

| Coprocessor               |                   |                              |                              |  |

| N/ a ver a ver            |                   | E16G301                      |                              |  |

| Memory                    |                   | 1 GB DDR3                    |                              |  |

| Ethernet                  |                   | Gigabit Ethernet             |                              |  |

| Boot Flash                |                   | 128Mb QSPI Flash             |                              |  |

| Power                     |                   | 5V DC                        |                              |  |

| Storage                   |                   | Micro-SD                     |                              |  |

| USB                       | No                | USB 2.                       | 0 Host Port                  |  |

| HDMI                      | No                | Micr                         | o HDMI                       |  |

| GPIO Pins                 | 0                 | 24                           | 48                           |  |

| eLink                     | 0                 | 2                            | 2                            |  |

| Connectors                |                   |                              |                              |  |

| FPGA                      | 28K Logic Cells   | 28K Logic Cells              | 80K Logic Cells              |  |

| Logic                     | 80 DSP Slices     | 80 DSP Slices 220 DSP slices |                              |  |

| Weight                    | 1.3 oz (36 grams) |                              |                              |  |

| Size                      |                   | x 0.625" (90mmx55mmx18mm)    |                              |  |

| SKU                       | P1600-DKxx        | P1601-DKxx                   | P1602-DKxx                   |  |

| HTS Code<br>(Schedule B ) | 8471.41.0150      | 8471.41.0150 8471.41.0150    |                              |  |

Table 2-1: Parallella Feature Summary

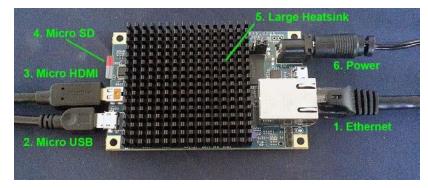

Figure 2-1: Parallella Board (top view)

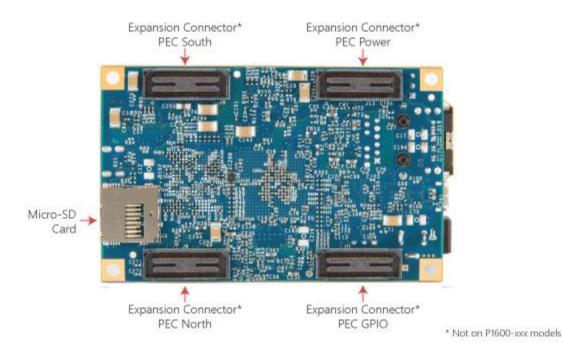

Figure 2-2: Parallella Board (bottom view)

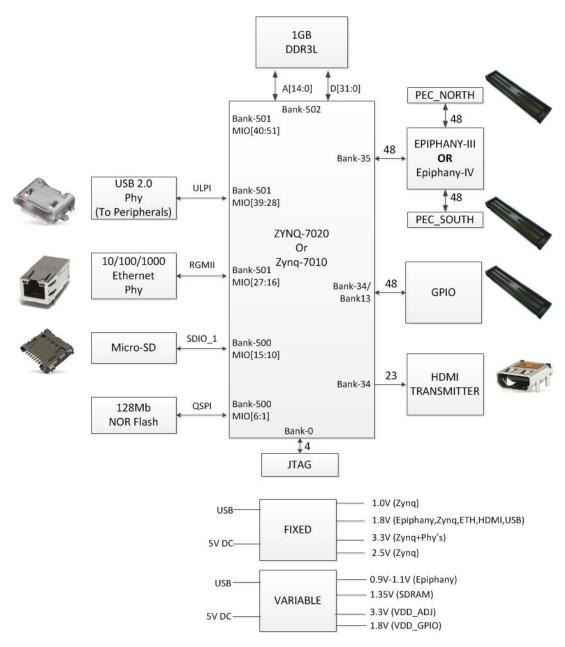

Figure 2-3: Zynq connectivity Diagram

# 2.2 Parallella System Architecture

#### 2.2.1 Zynq Memory Map

Table (2-2) shows the hard-coded memory architecture of the Zynq architecture most relevant to the Parallella architecture.

Table 2-2: Zynq memory map

| Address Start | Address End | Size  | Function | Note                 |

|---------------|-------------|-------|----------|----------------------|

| 0x0010_0000   | 0x3FFF_FFFF | 1GB   | DRAM     | Accessible to all    |

|               |             |       |          | interconnect         |

|               |             |       |          | masters              |

| 0x4000_0000   | 0x7FFF_FFFF | 1GB   | PL       | Custom logic address |

|               |             |       |          | range                |

| 0x8000_0000   | 0xBFFF_FFFF | 1GB   | PL       | Epiphany address     |

|               |             |       |          | range                |

| 0xFC00_0000   | 0xFCFF_FFFF | 16MB  | FLASH    | Quad-SPI linear      |

|               |             |       |          | address for linear   |

|               |             |       |          | mode                 |

|               |             |       |          |                      |

| 0xFFF0_0000   | 0xFFFF_FFFF | 252KB | OCM      | OCM upper address    |

|               |             |       |          | range                |

The ARM communicates with programmable logic, GPIO connected to the programmable logic, and the Epiphany by accessing the memory ranges shown in the table.

The Epiphany 32-bit memory space is mapped into the Zynq memory space allowing for easy sharing of data and resources between the ARM and the Epiphany. The Epiphany address range is a matter of convention and depends on the appropriate AXI master and slave interfaces being implemented within the programmable logic on the Zynq.

### 2.2.2 Epiphany Memory Map

The Epiphany chip is situated within a 1GB section within the Zynq host processor memory map. The offset within the 1GB space occupied by an Epiphany coprocessor is set by the ROWID and COLID pins on the Epiphany chip. The ROWID and COLID can be individually set on boards through the PEC\_POWER connector enabling direct board to board connection through the PEC\_NORTH and PEC\_SOUTH connectors. By default, the address locations of the Epiphany cores on Parallella-16 are as shown in Table (2-3).

| Core Number | Start Address | End Address | Size |

|-------------|---------------|-------------|------|

| (32,8)      | 80800000      | 80807FFF    | 32KB |

| (32,9)      | 8090000       | 80907FFF    | 32KB |

| (32,10)     | 80A00000      | 80A07FFF    | 32KB |

| (32,11)     | 80B00000      | 80B07FFF    | 32KB |

| (33,8)      | 84800000      | 84807FFF    | 32KB |

| (33,9)      | 84900000      | 84907FFF    | 32KB |

| (33,10)     | 84A00000      | 84A07FFF    | 32KB |

| (33,11)     | 84B00000      | 84B07FFF    | 32KB |

| (34,8)      | 88800000      | 88807FFF    | 32KB |

| (34,9)      | 88900000      | 88A07FFF    | 32KB |

| (34,10)     | 88A00000      | 88A07FFF    | 32KB |

| (34,11)     | 88B00000      | 88B07FFF    | 32KB |

| (35,8)      | 8C800000      | 8C807FFF    | 32KB |

| (35,9)      | 8C900000      | 8C907FFF    | 32KB |

| (35,10)     | 8CA00000      | 8CA07FFF    | 32KB |

| (35,11)     | 8CB00000      | 8CB07FFF    | 32KB |

Table 2-3: Epiphany memory map

#### 2.3 Parallella Features Description

#### 2.3.1 CPU

The central processor on the Parallella board is the Zynq<sup>™</sup>-7000 AP SoC. The Zynq represents a new class of processor product which combines an industry-standard ARM® dual-core Cortex<sup>™</sup>-A9 MPCore<sup>™</sup> processing system with Xilinx 28nm programmable logic. The Zynq SoC includes the following set of features:

Dual-core ARM® Cortex<sup>TM</sup>-A9 CPU:

- Coherent multiprocessor support.

- ARMv7-A architecture.

- 32 KB Level 1 4-way set-associative instruction/data caches (independent for each CPU).

- 512 KB 8-way set-associative Level 2 cache shared between CPUs.

- TrustZone® security.

- Jazelle® RCT execution Environment Architecture.

- NEON<sup>TM</sup> media-processing engine.

- Single and double precision Vector Floating Point Unit (VFPU).

- CoreSight<sup>TM</sup> and Program Trace Macrocell (PTM).

• Three watchdog timers, one global timer, two triple-timer counters.

I/O Peripherals and Interfaces:

- 10/100/1000 tri-speed Ethernet MAC peripherals GMII, RGMII, and SGMII interfaces.

- Two USB 2.0 OTG peripherals.

- Two full CAN 2.0B compliant CAN bus interfaces.

- Two SD/SDIO 2.0/MMC3.31 compliant controllers.

- Two full-duplex SPI ports with three peripheral chip selects.

- Two high-speed UARTs (up to 1 Mb/s).

- Two master and slave I2C interfaces.

- 8-Channel DMA Controller with scatter/gather capability.

- JTAG port for ARM debugging and FPGA programming.

- 12-bit ADC input.

- On-chip voltage and temperature sensing.

Programmable Logic:

- LVCMOS, LVDS, and SSTL signaling with 1.2V to 3.3V IO.

- Easily accessible from ARM cores through AXI bus (master or slave).

- Up to 125 programmable IO pins (Z-7020).

- Up to 85K programmable logics cells (Z-7020).

- Up to 560 KB distributed RAM (Z-7020).

- Up to 220 DSP slice and (Z-7020).

### 2.3.2 Epiphany Coprocessor

The Parallella-16 includes the E16G301 device with 16 CPU cores and the Parallella-64 includes the E64G401 device with 64 CPU cores. Both devices have the following basic features: Epiphany Core (eCore):

- 32-bit dual-issue superscalar RISC architecture.

- Quad-bank 32KB local single cycle access memory.

- Floating point instruction set (IEEE754).

- 64-entry register file.

- Dual channel DMA engine.

- Two 32-bit timers.

- Nested interrupt controller.

- Memory protection unit.

- Debug unit.

#### Network-On-Chip (eMesh):

- Three separate networks:

- rMesh for read transactions

- xMesh for off-chip write transactions

- cMesh for on-chip write transactions

- "API-less" network that processes regular load/store transactions.

- All transactions are complete and atomic 104 bit transactions (32-bit address, 64-bit data, and 8 control bits).

- Around robin arbitration at every mesh node.

- Mesh network extends off chip enabling glue-less multi-chip design.

Chip-To-Chip Links (eLink):

- North, east, west, south links for connecting to other Epiphany chips, FPGAs, or ASICs.

- Source synchronous LVDS links with transmit clock aligned in the middle of the data eye.

- Dual data rate communication (positive and negative edge transfers).

- Max transfer of 2 bytes transferred in and out simultaneously per link per clock cycle.

- Automatic bursting for sequential 64-bit write transactions.

# 2.3.3 SDRAM

1GB 32-bit wide DDR3L SDRAM.

### 2.3.4 LED Indicators

- A green LED controlled by the Zynq GPIO pin.

- A red LED controlled by the Epiphany flag pin.

• Two LEDs on the RJ45. The left LED indicates link speed. (amber=1Gb, green=100Mb, off=10Mb). The right indicates that there is activity on the port.

### 2.3.5 Serial Port

A three-pin header for 3.3V UART output from the Zynq.

### 2.3.6 Powering the Board

The Parallella should be powered through a stable 5V/2A power supply. Current consumption for the Parallella board can be as low as 0.3A but can reach 1.5A when fully loaded.

# 2.4 Parallella Start & Booting

Figure 2-4: Parallella accessories

#### **Step1: Ensuring the required accessories**

- A high quality 2000mA rated 5V DC power supply with 5.5mm OD / 2.1mm ID center positive polarity plug.

- An Ethernet cable.

- A fan.

- A micro HDMI to HDMI cable (not needed for headless option as in our project).

- A USB male Micro-B to female Standard-A cable (not needed for headless option as in our project).

#### Step 2: Creating a bootable micro-SD card

• Using "SDFormatter" program to format SD card.

- Using "Win32DiskImager" program to boot Ubuntu image onto SD card

- Another way follows [1].

#### Step 3: Familiarizing with known issues

- The board does get hot so we have to take precautions to cool the board properly. Before letting the board run for hours, we must ensure that the board doesn't overheat. (Preferably by using the 'xtemp' utility script exists on board)

- Boards used without a fan must be placed vertically.

- The Parallella is sensitive to static discharge and must be handled appropriately.

### Step 4: Connect peripherals, fit the heat-sink and apply power

- Connect the cables as indicated by #1, 4 in Figure (2-4)

- Attach a heatsink to the Zynq device using double face sticker shipped with board as indicated by #5 in Figure (2-4)

- Make sure a fan is directed at the board if required. A fan is required when using the small heatsink.

- Monitor the temperature using a utility such as xtemp, and keep the chip temp below 70 degrees Celsius.

- Apply power as indicated by #6 in Figure (2-4).

### Step 5: Connect between PC and Board

Option 1: Connecting using UART cable.

Option 2: Connecting by opening session with board using (ssh parallella@ip) command as we have used in our work.

#### Step 6: Build and run a program

The system will boot and a login screen will appear.

Login with the username parallella and password parallella.

somaia@somaia-Lenovo:~\$ ssh parallella@192.168.1.9 parallella@192.168.1.9's password: Welcome to Linaro 14.04 (GNU/Linux 3.14.12-parallella-xilinx-g40a90c3 armv7l) \* Documentation: https://wiki.linaro.org/ Last login: Sat Mar 12 16:40:35 2016 from somaia-lenovo.zte.com.cn

Figure 2-5: Login in parallella board

# Chapter 3: Epiphany SDK

## 3.1 Introduction

#### 3.1.1 SDK (Software Development Kit) Overview

The Epiphany<sup>™</sup> architecture defines a multicore, scalable, shared-memory computing fabric. It consists of a 2D array of mesh compute nodes connected by a low-latency mesh network-on-chip.

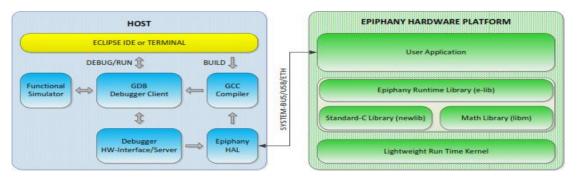

The Epiphany Software Development Kit (eSDK) is a state-of-the art software development environment targeting the Epiphany multicore architecture. The eSDK is based on standard development tools including an optimizing C-compiler, functional simulator, debugger, and multicore integrated development environment (IDE). The eSDK enables out-of-the-box execution of applications written in regular ANSI-C and does not require any C-subset, language extensions, or SIMD style programming. The unparalleled energy efficiency of the Epiphany architecture and the ease of use and fine grain control of the eSDK offer developers best-in-class capabilities for the most demanding real-time applications. The Epiphany SDK framework is illustrated in Figure (3-1) and contains the following key components:

- Optimized ANSI-C compiler (based on gcc).

- Robust multicore Eclipse IDE (on selected platforms "doesn't exist on our platform).

- Multicore debugger (based on gdb).

- Multicore communication and hardware utility libraries.

- Fast functional simulator with instruction trace capability.

Figure 3-1: Epiphany SDK

## 3.1.2 Epiphany Memory Model

The Epiphany cores have access to two types of memory. Both types can be accessed directly [6].

#### Internal Memory

Size: 32KB (0x8000) per core

Location in address space:

- 0x0000000 0x00007fff when a core is referring to its own memory.

- 0xXXX00000 0xXXX07fff when referring to the memory of any other core. The xxx indicate the core.

#### Terminology:

- Internal memory.

- eCore memory.

- SRAM or Static RAM. Not to be confused with Shared memory.

#### Usage:

- Program code, starting at lower addresses.

- Program data (global variables), starting at lower addresses after code.

- Stack (local variables), starting at 0x8000 expanding downwards.

#### External Memory

Size: 32 MB (0x02000000)

Location in address space:

• 0x8e000000 - 0x8ffffff

#### Terminology:

- External memory

- Shared memory

- DRAM or Dynamic RAM

- SDRAM or Shared DRAM

Usage:

• Location: 0x8e000000 - 0x8efffff

Size: 0x01000000 (16 MB)

**Contents**: newlib (the C library, with code, data, stack)

• Location: 0x8f000000 - 0x8ffffff

Size: 0x01000000 (16 MB)

#### **Contents**:

• Location: 0x8f000000 - 0x8f7ffff

Size: 0x00800000 (8 MB)

Section label: shared\_dram

Contents: used by the e\_shm\_xxx functions of the ESDK

**Extra info**: because of a bug, malloc returns addresses from this region which causes this region to be corrupted if one uses any C function that uses malloc internally.

• Location: 0x8f800000 - 0x8ffffff

Size: 0x00800000 (8 MB)

Section label: heap\_dram

**Contents:** is meant to be divided in 512KB for each core (16 \* 512KB = 8MB) and then used for malloc but this does not currently work. Instead malloc returns addresses from shared\_dram

#### 3.1.3 Epiphany Programming Framework

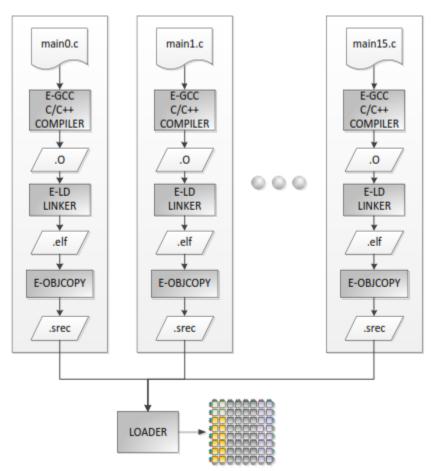

Each one of the Epiphany processor nodes can run independent programs. Figure (3-2) shows the general programming flow for the Epiphany architecture, highlighting the independent build of programs running on different cores and the use of a common loader to load the complete multicore program onto the chip.

Figure 3-2: Epiphany program build flow

## 3.2 Building SDK

#### 3.2.1 Building Steps

Step 1: Installing Prerequisites

#### (The following packages need to be installed in order to build the SDK)

Sudo apt-get install build-essential git bison flex libgmp3-dev libncurses-dev libmpc-dev libmpfr-dev texinfo xzip lzip zip gcc-arm-linux-gnueabihf g++-arm-linux-gnueabihf

#### Step 2: Downloading the SDK

First, we should create a directory for our build environment, for example  $\{HOME\}/epiphany-sdk$ . Next set an environment variable named EPIPHANY\_BUILD\_HOME which points to the root of your build tree.

```

mkdir epiphany-sdk

export EPIPHANY BUILD HOME=$HOME/epiphany-sdk

```

#### (Downloading the SDK Sources)

cd \$EPIPHANY\_BUILD\_HOME

git clone https://github.com/adapteva/epiphany-sdk sdk

#### (Downloading the SDK build Scripts)

mkdir buildroot && cd buildroot

git clone --branch 2016.3 https://github.com/adapteva/epiphany-sdk.git

sdk

#### Step 3: Building the SDK

(Building for Intel x86-64 (on x86-64))

./sdk/build-epiphany-sdk.sh -C -R -a x86\_64

#### Step 4: Adding the SDK to my Path

export PATH=/home/somaia/epiphany-sdk/esdk/tools/e-gnu/bin:\$PATH

(Note: Building SDK is done completely over the Internet, so it needs stable internet also because the building lasts for 12 hours almost [5].)

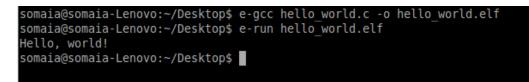

#### 3.2.2 Building check

To check that the SDK have been built successfully, we have run simple code of Hello-World using Compiler and Simulator of SDK.

- 1. We have downloaded text editor "gedit" for writing scripts.

- 2. Write simple code to print Hello-World.

- 3. To compile the code we have to change the path of code script to the path of "e-gnu" of SDK. To avoid changing path of every code to path of SDK we have edited ".bashrc" file with the path of SDK so it can see it always and we don`t need to change path again. Edit ".bachrc" with

```

export PATH=/home/somaia/epiphany-sdk/esdk/tools/e-gnu/bin:$PATH

export EPIPHANY_HOME=/home/somaia/epiphany-sdk/esdk

export EPIPHANY_HDF=/home/somaia/epiphany-sdk/

```

esdk.2015.1/bsps/parallella\_E16G3\_1GB

4. Compile code by this command

\$ e-gcc hello\_world.c -o hello\_world.elf

hello\_world.c: code file name

-o: option to generate output in the next file

hello\_world.elf: output file with elf extension for simulation

5. Simulate code by this command

\$ e-run hello world.elf

Figure 3-3: Simulate hello-world simple code

## 3.3 Epiphany SDK Tool chain

### 3.3.1 C/C++ Compiler (E-GCC)

The GCC compiler supports the following versions of C/C++:

- ISO/IEC 9899:1990 (C89)

- ISO/IEC 9899:1999 (C99)

- ISO/IEC 9899:2011 (C11) (partial)

- ISO/IEC 14882:1998 (C++98)

- ISO/IEC 14882:2011 (C++11) (partial)

To use the compiler to create an executable from a simple program source file without any optimization.

```

$ e-gcc hello_world.c -o hello_world.elf

```

The GCC compiler supports a wide range of options allowing for fine grain compilation process. Some are illustrated in Table (3-1) and some of optimization options are illustrated in Table (3-2).

| Option  | Function                                                         |

|---------|------------------------------------------------------------------|

| -C      | Compile or assemble source code, but do not link                 |

| -o file | Place output in file <i>file</i> .                               |

| version | Print the version number of the compiler                         |

| @file   | Read command-line options from file.                             |

| help    | Print (on the standard output) a description of the command line |

|         | options understood by gcc.                                       |

Table 3-1: General Compiler Options

Table 3-2: Optimization Options

| Option | Function                                                        |

|--------|-----------------------------------------------------------------|

| -00    | Reduce compilation time and make debugging produce the expected |

|        | results. This is the default.                                   |

| -01    | '-O or –O1' turns on the following optimization flags:          |

|        | -fauto-inc-dec -fcprop-registers                                |

|        | -fdce -fdefer-pop                                               |

|        | -fdelayed-branch -fdse                                          |

|        | -fguess-branch-probability -fif-conversion2                     |

|        | -fif-conversion -finline-small-functions                        |

|        | -fipa-pure-const -fipa-reference                                |

|        | -fmerge-constants -fsplit-wide-types                            |

|        | -ftree-ccp -ftree-ch                                            |

| <b>F</b> |                                                                          |

|----------|--------------------------------------------------------------------------|

|          | -ftree-copyrename -ftree-dce                                             |

|          | -ftree-dominator-opts -ftree-dse                                         |

|          | -ftree-fre -ftree-sra                                                    |

|          | -ftree-ter -funit-at-a-time                                              |

|          |                                                                          |

|          | '-O' also turns on '-fomit-frame-pointer'                                |

| -O2      | GCC performs nearly all supported optimizations that do not involve      |

|          | a space-speed tradeoff. It turns on all optimization flags in O1 and the |

|          | following additional flags:                                              |

|          | -fthread-jumps -falign-functions                                         |

|          | -falign-jumps -falign-loops                                              |

|          | -falign-labels -fcaller-saves                                            |

|          | -fcrossjumping -fcse-follow-jumps                                        |

|          | -fcse-skip-blocks -fdelete-null-pointer-checks                           |

|          | -fdevirtualize -fexpensive-optimizations                                 |

|          | -fgcse -fgcse-lm                                                         |

|          | -finline-small-functions -findirect-inlining                             |

|          | -fipa-sra -foptimize-sibling-calls                                       |

|          | -fpartial-inlining -fpeephole2                                           |

|          | -fregmove -freorder-blocks                                               |

|          | -freorder-functions -frerun-cse-after-loop                               |

|          | -fsched-interblock -fsched-spec                                          |

|          | -fschedule-insns -fschedule-insns2                                       |

|          | -fstrict-aliasing -fstrict-overflow                                      |

|          | -ftree-switch-conversion -ftree-pre                                      |

|          | -ftree-vrp                                                               |

| -03      | Optimize yet moreO3 turns on all optimizations specified by -O2          |

| 00       | and                                                                      |

|          | also turns on:                                                           |

|          | -finline-functions -funswitch-loops                                      |

|          | -fpredictive-commoning -fgcse-after-reload                               |

|          | -ftree-vectorize -fipa-cp-clone                                          |

| L        |                                                                          |

#### **3.3.2** Linker (E-LD)

The Epiphany linker 'e-ld' combines a number of objects and archives, relocates their data and resolves symbol references.

To use the linker to create an elf executable from an object file using the default linker file for simulation using the Epiphany instruction set simulator.

```

$ e-ld my object.o -o exec.elf

```

The link process is controlled by a linker script written in the GNU linker command language. The purpose of the linker script is to describe how the sections in the input files should be mapped into the output file, and to control the memory layout of the output file. If you do not supply a linker file to 'e-ld', it will use a default linker file.

Executables compiled with the default linker will only execute correctly using the 'e-run' instruction set simulator and will not work correctly when loaded on specific hardware targets. To correctly link for specific hardware targets, you should use the '-T' option to specify one of the board specific linker files that come with the board support package (BSP) or your own custom linker file.

The linker description files that come with the different Epiphany Board Support Packages have a number of key words that allow fine grained management of code and data placement from within the C/C++ source code. The keywords gives the programmer and support libraries complete control of the placement of data and code within the memory system on a per-symbol, per-file, and per-object library. The keywords are derived from section names within the linker descriptor file and can be augmented by the user at his discretion. Table (3-3) shows configurations of the three basic linker descriptor files. The 'legacy' scenario is to be used for bringing up code quickly but will run slowly since all data and code is placed in external memory. The 'fast' scenario is used to place user code internally and standard library 'code externally. The 'internal' scenario can be used for to effectively place all code and data in the local memory by default. The three descriptor files effectively determine the default placement of all sections and symbols within the objects. The user can override these settings on an individual basis from the C/C++ source code using the attributes defined in Table (3-4) to specify that certain variables and/or functions should be placed in specific program output sections. Note that with all of the predefined LDF's, the heap is allocated externally. This means that use of stdio library will render the program very slow.

Table 3-3: Memory Management Scenarios

| File         | User Code         | Standard          | Stack             | Note                                                                                                                                                                                                                            |

|--------------|-------------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | & Data            | Library           |                   |                                                                                                                                                                                                                                 |

| legacy.ldf   | External<br>SDRAM | External<br>SDRAM | External<br>SDRAM | Use to run any legacy code<br>with up to 1MB of<br>combined code and data.                                                                                                                                                      |

| fast.ldf     | Internal<br>SRAM  | External<br>SDRAM | Internal<br>SRAM  | Places all user code and<br>static data in local memory,<br>including the stack. Use to<br>implement fast critical<br>functions. It is the user's<br>responsibility to ensure that<br>the code fits within the local<br>memory. |

| internal.ldf | Internal<br>SRAM  | Internal<br>SRAM  | Internal<br>SRAM  | Places all code and static<br>data in local memory,<br>including the stack. Use to<br>implement fastest<br>applications. It is the user's<br>responsibility to ensure that<br>the code fits within the local<br>memory.         |

#### Table 3-4: Linker Sections

| Section      | User Controllable Sections                  |

|--------------|---------------------------------------------|

| .text        | Application code, read only                 |

| .data        | Application data (global variables that are |

|              | not constant)                               |

| .rodata      | Application data, read only (constants,     |

|              | strings)                                    |

| .bss         | Static variables initialized to zero        |

| .text_bank0  | Starts at end of reserved section in bank0  |

| .text_bank1  | Starts at the beginning of bank1            |

| .text_bank2  | Starts at the beginning of bank2            |

| .text_bank3  | Starts at the beginning of bank3            |

| .data_bank0  | End of .text_bank0                          |

| .data_bank1  | End of .text_bank1                          |

| .data_bank2  | End of .text_bank2                          |

| .data_bank3  | End of .text_bank3                          |

| .code_dram   | Code section in external memory             |

| .shared_dram | Data section in external memory             |

| .heap_dram   | Heap section in external memory             |

## 3.3.3 Instruction Set Simulator (E-Run)

The Epiphany Instruction Set Simulator (ISS) is an accurate and fast functional representation of the Epiphany Instruction Set Architecture. The simulator accurately models the instruction set and

register map of a single Epiphany core, but does not model pipeline behavior or any of the non-CPU hardware mechanisms such as the eMesh Network-On-Chip, DMA, or timers. The simulator runs in a host Linux environment, takes a binary ELF file as an input and supports standard I/O. To simplify program debugging and profiling, the simulator supports outputting program traces. Simulation of the execution of an Epiphany elf executable using the ISS within a Linux host platform is done by this command

\$ e-run hello\_world.elf

To get an instruction trace of the executed program, use the '-t' option before the hello\_world.elf argument as follows:

\$ e-run -t hello world.elf

Table 3-5: Simulator Command Line Options

| Option                      | Function                                                                            |

|-----------------------------|-------------------------------------------------------------------------------------|

| -t,trace                    | Output simulated instruction trace to scree                                         |

| memory-region ADDRESS, SIZE | Defines a memory region as valid for<br>simulator.<br>Default is to allow 0x0 → 1MB |

| help                        | Prints help                                                                         |

#### **3.3.4 Debugger (E-GDB)**

The Epiphany debugger (e-gdb) is based on the popular GNU GDB debugger. It allows to see what is going on inside a program while it executes. Some of the powerful debug features enabled by the debugger include:

- Interactive program load.

- Stopping program on specific conditions (usually a breakpoint placed in source code).

- Examine complete state of machine and program once program has stopped.

- Continuing program one instruction at a time or until the next stop condition is met.

The Epiphany debugger supports program debugging using the functional simulator as a target or the hardware platform as a target using the 'e-server'. The only difference between the two modes of debugging is the argument specified with the 'target' command within the debugger client. The simulator only supports debugging programs running on a single Epiphany CPU core and is not multi-core aware.

To debug a simple "Hello World" program with the Epiphany instruction set simulator.

In a Linux shell, start an e-gdb session using your executable.

```

$ e-gdb hello world.elf

```

Inside e-gdb, connect to the instruction set simulator debugging target.

(gdb) target sim

Load the program to the core memory.

(gdb) load

Place a breakpoint at the main function entry point.

(gdb) b main

Run the functional simulator.

(gdb) run

Continue program execution from breakpoint.

(gdb) c

Program then runs until completion and displays.

"Hello World!"

Exit debugger

(gdb) q

Debugging a program running on an Epiphany based hardware target.

Make sure that a connection has been established with the hardware using the e-server program:

\$ e-server -hdf \${EPIPHANY\_HOME}/bsps/emek3/emek3.xml -testmemory

In a Linux shell, start a e-gdb session using your executable (same as for the simulator).

\$ e-gdb hello world.elf

Inside e-gdb, connect to the TCP/IP socket connected to core that you want to debug.

(gdb) target remote:51000

Load the program the core memory.

(gdb) load

Place a breakpoint at the main function entry point.

(gdb) b main

Continue program execution from breakpoint.

(gdb) c

Program then runs until completion and displays.

"Hello World!"

Exit debugger

(gdb) q

Invoke the debugger by running the program 'e-gdb'. Once started, 'e-gdb' reads commands from the terminal until you tell it to exit. You can also run 'e-gdb' with a variety of arguments and options, to specify more of your debugging environment at the outset.

The most common way to start 'e-gdb' is to simply specify the program as the only argument: \$ e-gdb program.elf

| Option       | Function                                                     |

|--------------|--------------------------------------------------------------|

| -x file      | Execute gdb commands from file <i>file</i> .                 |

| -d directory | Add <i>directory</i> to the path to search for source files. |

| -quiet   q   | "Quiet". Do not print the introductory and copyright         |

| -silent      | messages.                                                    |

Table 3-6: Debugger Command Line Options

## 3.3.5 Hardware Connection Server (E-SERVER)

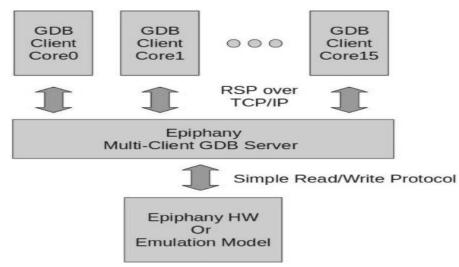

The GDB client runs on the Linux host machine and communicates with the Epiphany GDB server using GDB's internal RSP (remote serial protocol) over TCP/IP ports. The e-server responds to the GDB client or Loader requests and controls the hardware or hardware emulation model. Each core in the system needs a separate GDB client and connects to the GDB server using a unique TCP/IP port. By default, cores connect to the e-server starting at port 51000. The e-server responds to the e-loader requests in the dedicated port.

An illustration of the GDB server/client operations is shown below in Figure (3-3):

Figure 3-4: The eServer Client-Target Connection Concept

To start the Target Server, open a terminal window and type the following in the command line:

\$ e-server -hdf

\${EPIPHANY\_HOME}/bsps/zedboard/zed\_E16G3\_512mb.xml

The debug server now responds with status messages regarding the connection process and the results of the memory test, if performed. The output should be similar to the following:

```

Using the HDF file: zed_E16G3_512mb.xml

Listening for RSP on port 51000

Listening for RSP on port 51001

Listening for RSP on port 51002

Listening for RSP on port 51004

Listening for RSP on port 51005

:

Listening for RSP on port 51006

Listening for RSP on port 51007

Listening for RSP on port 51010

Listening for RSP on port 51010

Listening for RSP on port 51011

```

Table 3-7: eServer Command line Options

| Argument        | Note                                          |  |

|-----------------|-----------------------------------------------|--|

| -hdf file       | Mandatory argument, specifies the platform    |  |

|                 | specific description file containing platform |  |

|                 | definitions, normally located in the          |  |

|                 | esdk/bsps/{platform} directory.               |  |

| show-memory-map | Print out the supported memory map.           |  |

| test-memory     | Test the memory before serving the            |  |

|                 | debugger clients (*only for select platforms) |  |

The run-time connection from a host to the epiphany target is performed via the eHAL library.

## **3.4** Epiphany SDK utilities (E-UTILS)

#### 3.4.1 Introduction

The Epiphany SDK is provided with a group of command-line utility programs. These programs are used to perform Epiphany system related tasks during program development and debugging. The e-utils programs include:

e-reset

e-loader e-read e-write

### 3.4.2 Reset Utility (E-RESET)

The Epiphany reset utility (e-reset) is used to reset the Epiphany subsystem, in case it gets stuck due to some unstable situation, or in order to bring it to a known state.

\$ e-reset

#### 3.4.3 Loader Utility (E-LOADER)

The Epiphany loader (e-loader) is responsible for loading programs onto the hardware platform. The input to the loader is a compiled and linked Epiphany program that was generated by e-gcc/e-ld. currently, the loader supports binary images formatted as a text file with a standard S-record (known as SREC) file format. This format is an ASCII hexadecimal ("hex") text encoding for binary data. The S-record is an output of the binary utility 'e-objcopy'.

When loading a binary image on the chip there is a need to translate the internal core addresses to global space addresses. During compile time, the build tools do not know what core will be the target of the executable. This information is known only at load time. Thus, the insertion of the core ID data has to be done prior to sending the SREC file to the e-loader. When loading images of more than one core, each partial SREC has to be pre-processed separately.

e-loader [-s|--start] [-r|--reset] <e-program> [row col [rows cols]]

| Option                  | Function                                                              |

|-------------------------|-----------------------------------------------------------------------|

| -r,reset                | Perform a full hardware reset of the Epiphany platform before loading |

|                         | the program.                                                          |

| -s,start                | With this option set, the loaded programs are started after they have |

|                         | finished loading on all cores in workgroup.                           |

| <e-program></e-program> | Path to the program image to load onto the core workgroup.            |

| row, col                | Absolute coordinates of first core in workgroup to be loaded. The     |

|                         | default values are the platform's first physical core.                |

| rows, cols              | Size of cores workgroup to be loaded. The default values are (1, 1).  |

| h,help                  | Display a help message.                                               |

Table 3-8: Loader Command line Options

After building an Epiphany elf program, translate from elf to S-record program load format:

\$ e-objcopy --srec-forceS3 --output-target srec main1.elf main1.srec

Load program onto the target, on a 4\*4 block of cores starting at core 0x808 (32, 8) and start it immediately after:

\$ e-loader --start main.srec 32 8 4 4

Or, perform a system reset and load the program onto a single core at the chip's origin. Then wait for host command to start the program.

\$ e-loader --reset main.srec

### 3.4.4 Memory Read Utility (E-READ)

The Epiphany memory read utility (e-read) is used to read words from memory locations on the

Epiphany chip(s) or the External Memory.

```

e-read [-v|-r] <row> [<col>] <address> [<num-words>]

```

Table 3-9: e-read Command line Options

| Table 5-9. e-reau Coll     |                                                                                   |  |  |

|----------------------------|-----------------------------------------------------------------------------------|--|--|

| Option                     | Function                                                                          |  |  |

| <row></row>                | Row coordinate of the target core. To read data from External                     |  |  |

|                            | Memory, enter -1.                                                                 |  |  |

|                            |                                                                                   |  |  |

|                            | The core coordinates are relative to the platform's chip bounding box.            |  |  |

|                            | That is, all of the Epiphany chips are considered one workgroup,                  |  |  |

|                            | where the first core of the first chip is at coordinates (0,0).                   |  |  |

| [ <col/> ]                 | Row coordinate of the target core. When reading from External                     |  |  |

|                            | Memory, this parameter is omitted.                                                |  |  |

| <address></address>        | The start address of the read data. Address is given as local space when          |  |  |

|                            | reading from a core memory, or as an offset from the platform's                   |  |  |

|                            | External Memory base. Address should be in hexadecimal format and                 |  |  |

|                            | is rounded down to the word (4-bytes) alignment.                                  |  |  |

| [ <num-words>]</num-words> | Number of words to read from the target, starting at <address>. If this</address> |  |  |

|                            | parameter is omitted, a single word is read.                                      |  |  |

| [-v]                       | Verbose mode - print more information.                                            |  |  |

| [-r]                       | Raw mode - print only the memory contents.                                        |  |  |

## 3.4.5 Memory Write Utility (E-WRITE)

The Epiphany memory write utility (e-write) is used to write words to memory locations on the Epiphany chip(s) or the External Memory.

e-write [-v] <row> [<col>] <address> [<val0> <val1> ...]

Table 3-10: e-write Command line Options

| Option                         | Function                                                                                                                                                                                               |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <row></row>                    | Row coordinate of the target core. To read data from External                                                                                                                                          |  |  |

|                                | Memory, enter -1.                                                                                                                                                                                      |  |  |

|                                | The core coordinates are relative to the platform's chip bounding                                                                                                                                      |  |  |

|                                | box. That is, all of the Epiphany chips are considered one                                                                                                                                             |  |  |

|                                | Workgroup, where the first core of the first chip is at coordinates                                                                                                                                    |  |  |

|                                | (0,0).                                                                                                                                                                                                 |  |  |

| [ <col/> ]                     | Row coordinate of the target core. When reading from External                                                                                                                                          |  |  |

|                                | Memory, this parameter is omitted.                                                                                                                                                                     |  |  |

| <address></address>            | The start address of the read data. Address is given as local space                                                                                                                                    |  |  |

|                                | when reading from a core memory, or as an offset from the                                                                                                                                              |  |  |

|                                | platform's External Memory base. Address should be in                                                                                                                                                  |  |  |

|                                | hexadecimal format and is rounded down to the word (4-bytes)                                                                                                                                           |  |  |

|                                | Alignment.                                                                                                                                                                                             |  |  |

| [ <val0> <val1>]</val1></val0> | Number of words to write to the target, starting at <address>. If</address>                                                                                                                            |  |  |

|                                | This parameter is omitted, the input is taken in interactive mode<br>from the standard input, one word at a time, until an empty line is<br>entered. Values are entered as 32-bit hexadecimal numbers. |  |  |

## 3.5 Epiphany Hardware Utility Library (e-Lib)

The Epiphany Hardware Utility library provides functions for configuring and querying the Epiphany hardware resources. These routines automate many common programming tasks that are not provided by the C and C++ languages and are specific to the Epiphany architecture.

The master header file for the eLib, which includes all the per-family headers, is the "e-lib.h" header file. Include this header file at the beginning of a program that uses the eLib functions and objects.

#include ``e-lib.h"

In order to use this library to build an Epiphany program, use the e-gcc compiler option -le-lib on the build command line.

## 3.6 Epiphany Host Library (eHAL)

The Epiphany Hardware Abstraction Layer (eHAL) library provides functionality for communicating with the Epiphany chip when the application runs on a host. The host can be a PC or an embedded processor. The communication is performed using memory writes to and reads from shared buffers that the applications on both sides should define. The library interface is defined in the e-hal.h header file.

In order to use this library in your application, the compiler and linker must be configured with the paths to the header file and the library binary. In your tools options use the following configurations:

```

$ gcc -I${EPIPHANY_HOME}/tools/host/include \

-L${EPIPHANY_HOME}/tools/host/lib_le-hal ...

```

# Chapter 4: Frame Structure

#### 4.1 Introduction

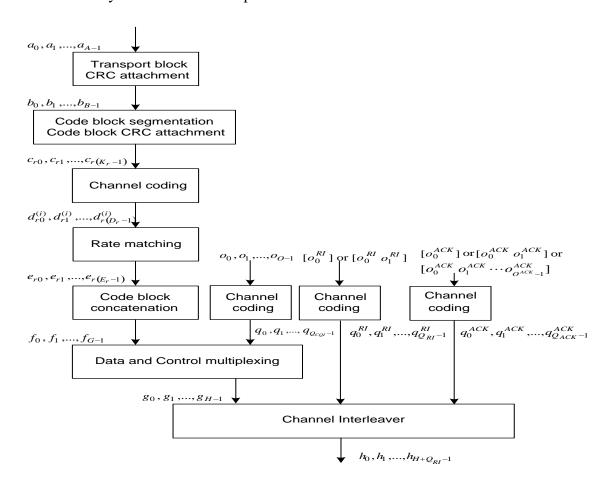

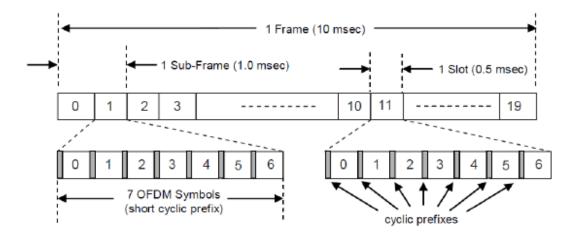

The bits that are carried on the radio waves undergo a lot of processing before these are ready for transmission. The processing makes them resilient to the attenuation, and also packs them in a way to make them economical to transmit over the air. The processing starts right from the point where they leave the MAC layer so the first stage of processing is the Transport Channel Processing which is called the bit chain in Figure (4-1) and the bit sequence resulting from this stage is input to the next stage which is called the symbol chain as in Figure (4-2). Hence, we can say that the PUSCH coding processing is divided into 2 processing chains, the bit chain and the symbol chain. Here In the project we are working in the physical layer for the uplink shared data and we are interested in the symbol chain to be implemented.

Figure 4-1: PUSCH Bit Processing Chain

Figure 4-2: PUSCH Symbol Processing Chain

Let's now take a quick overview about the symbol processing chain blocks.

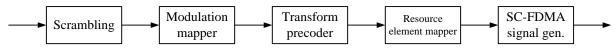

The baseband signal representing the physical uplink shared channel is defined in terms of the following steps: [10]

- Scrambling (change the input sequence by using a known random sequence)

- Modulation of scrambled bits to generate complex-valued symbols

- Transform Preceding to generate complex-valued symbols

- Mapping of complex-valued symbols to resource elements

- Generation of complex-valued time-domain SC-FDMA signal for each antenna port

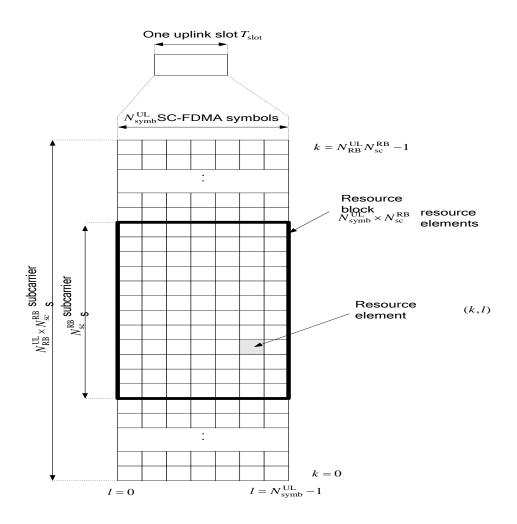

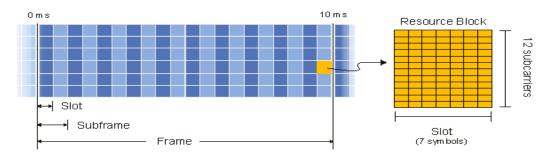

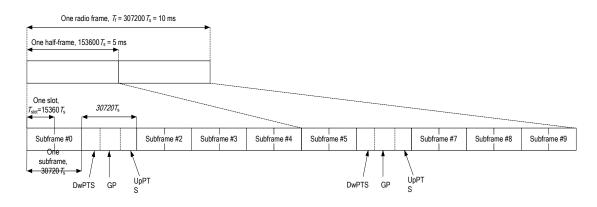

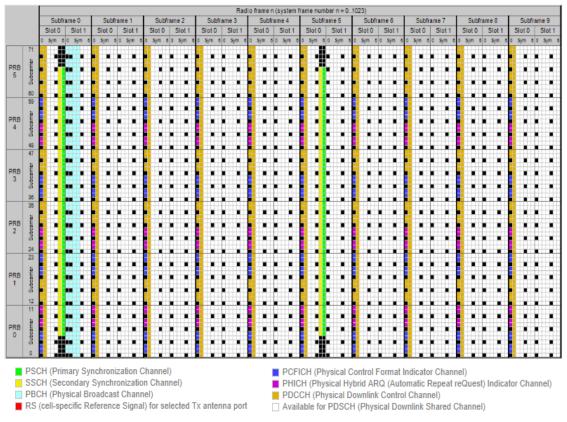

But before we are talking about the symbol chain blocks in deep, their use and implementation ways, let's talk about the Frame Structure.