## OFDM over Optical Fiber Channel

By

Asmaa Ali Rayan

Alaa Amr Othman

Maha Emad Abd El-Maqsoud

Under the Supervision of

Dr. Hassan Mostafa

Dr. Tawfik Ismail

A Graduation Project Report Submitted to the Faculty of Engineering at Cairo University In Partial Fulfillment of the Requirements for the Degree of

Bachelor of Science

in

Electronics and Communications Engineering

Faculty of Engineering, Cairo University

Giza, Egypt

July 2015

#### Contents

| Table of Figures                          | VIII      |

|-------------------------------------------|-----------|

| Table of Tables                           | X         |

|                                           | 2         |

| Chapter 1: Introduction                   | 2         |

| 1.1 Motivation & project definition       | 2         |

| 1.2 OFDM                                  |           |

| 1.2.1 Introduction                        |           |

| 1.2.2. Brief History                      |           |

| 1.2.1.1 OFDM Advantages                   |           |

| 1.2.1.2 OFDM disadvantages                | 5         |

| 1.2.2 Orthogonality and OFDM              | 6         |

| 1.3 Block Diagram                         | 6         |

| Blocks in details:                        | 7         |

| 1.3.1 Modulation and Demodulation of Data | 7         |

| 1.3.2 Serial to Parallel Converter        |           |

| 1.3.3 IFFT/FFT                            |           |

| 1.3.4 Guard Interval                      |           |

| 1.3.5 Cyclic Prefix                       | 9         |

| Chapter2.1 Introduction to WI-FI          |           |

| 2.1.1 Introduction                        |           |

| 2.1.2 Brief History                       |           |

| 2.1.3 Frequency and Data Rates            |           |

| 2.1.4 Architecture of 802.11              |           |

| 2.1.5 Wireless LAN Components             |           |

| 2.1.6 Range                               |           |

| 2.1.7 Benefits                            |           |

| Chapter3. System Explanation              |           |

| 3.1. Block Diagram                        |           |

| 3.2. Transmitter Blocks Implementation    |           |

| 3.2.1. Scrambler                          |           |

| 3.2.1.1 Function of Block                 |           |

| OFDM OVER OPTICAL ACCESS NETWORK          | II   Page |

|   | 3.2.1.2 Structure                                    | . 18 |

|---|------------------------------------------------------|------|

|   | 3.2.1.3 Description for VHDL Code flow chart         | . 19 |

|   | 3.2.1.4 Post Layout Simulation                       | 20   |

|   | 3.2.1.5 Performance measurement                      | 20   |

|   | 3.2.2 Encoder                                        | 21   |

|   | 3.2.2.1 Introduction                                 | 21   |

|   | 3.2.2.2 Convolutional Codes                          | . 21 |

|   | 3.2.2.3 Puncturing Convolutional Codes               | . 23 |

|   | 3.2.2.4 Function of the Block                        | . 25 |

|   | 3.2.2.5 Structure                                    | . 25 |

|   | 3.2.2.6. The VHDL code description                   | . 26 |

|   | 3.2.2.7. Flow chart of the encoder                   | 28   |

|   | 3.4.2.8. Post Layout Simulation                      | . 29 |

|   | 3.2.2.9 Performance measures                         | . 29 |

|   | 3.2.3 Interleaver                                    | . 29 |

|   | 3.2.3.1. Function of block                           | . 29 |

|   | 3.2.3.3 Interleaver Implementation                   | . 31 |

|   | 3.2.3.5 Performance Measurement                      | 32   |

|   | 3.2.4 Mapper                                         | 32   |

|   | 3.2.4.1. Function of the block                       | . 32 |

|   | 3.2.4.2 Block diagram                                | . 36 |

|   | 3.2.4.3 The VHDL Code description                    | . 37 |

|   | 3.2.4.4. The Calculated I and Q values in the mapper | 38   |

|   | 3.2.4.5. Flow chart for the mapper                   | 40   |

|   | 3.2.4.6 Post Layout Simulation                       | . 41 |

|   | 3.2.4.7 Performance Measurement                      | 41   |

|   | 3.2.5. Framer                                        | 41   |

|   | 3.2.5.1. Function of the Block                       | 41   |

|   | 3.2.5.3 VHDL Description                             | . 43 |

|   | 3.2.5.4. Post Layout Simulation                      | . 44 |

|   | 3.2.5.5. Performance measurement                     | . 44 |

|   | 3.2.6 FFT/IFFT                                       | . 45 |

| О | FDM OVER OPTICAL ACCESS NETWORK III   P a g          | е    |

| 3.2.6.1 CFFT core                                  |           |

|----------------------------------------------------|-----------|

| 3.2.6.2 Description                                |           |

| 3.2.6.3 Block diagram                              |           |

| 3.2.6.4 Timing                                     |           |

| 3.2.6.5 Gain                                       |           |

| 3.2.6.6 Interfacing the CFFT core to the system    |           |

| 3.2.6.7 Structure:                                 |           |

| 3.2.6.8 Post Layout Simulation                     | 50        |

| 3.2.6.9 Performance measurements:                  | 51        |

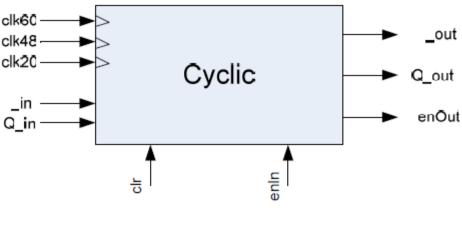

| 3.7.2 Cyclic Extension                             | 51        |

| 3.2.7.1 Function of Block                          |           |

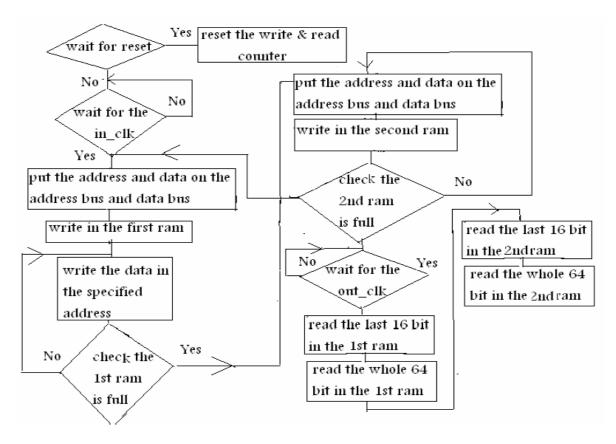

| 3.2.7.3 The VHDL code description                  |           |

| 3.2.7.4. Flow chart of the cyclic extension block: | 53        |

| 3.2.7.5 Post Layout Simulation                     | 54        |

| 3.2.7.6 Performance measurement                    | 54        |

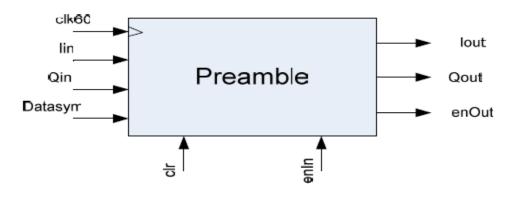

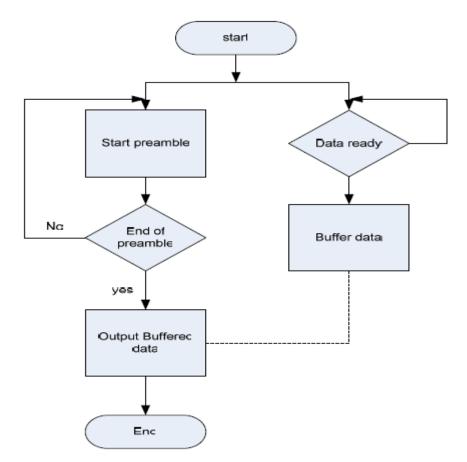

| 3.2.8 Preamble                                     | 54        |

| 3.2.8.1 Function of the Block                      | 54        |

| 3.2.8.2. Structure                                 | 55        |

| 3.2.8.3. Flow chart of the Preamble block          | 55        |

| 3.2.8.4 Post Layout Simulation                     |           |

| 3.2.8.5 Performance measurement                    |           |

| 3.3 Receiver Blocks Implementation                 |           |

| 3.3.1 Packet divider                               |           |

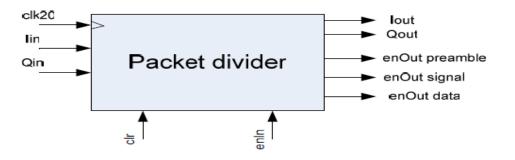

| 3.3.1.1 Structure                                  |           |

| 3.3.1.2 Operation:                                 | 59        |

| Chapter4. Controller Implementation                | 61        |

| 4.1. Transmitter Controller Implementation         | 61        |

| 4.1.1 Introduction                                 | 61        |

| 4.1.2. Data Rates                                  | 61        |

| 4.1.3 Idea of Controller                           | 61        |

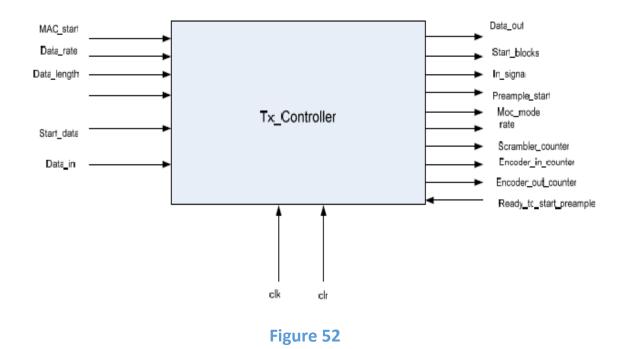

| 4.1.4. Structure                                   |           |

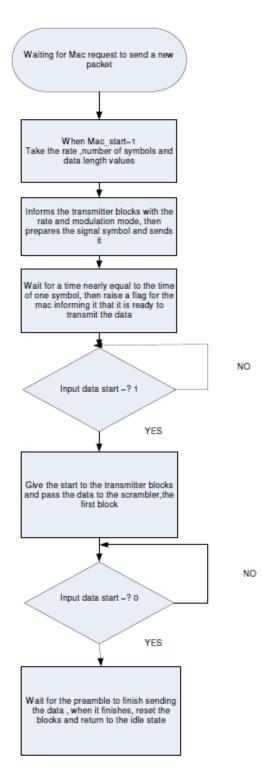

| 4.1.5 VHDL Description using Flow Chart            | 63        |

| OFDM OVER OPTICAL ACCESS NETWORK                   | IV   Page |

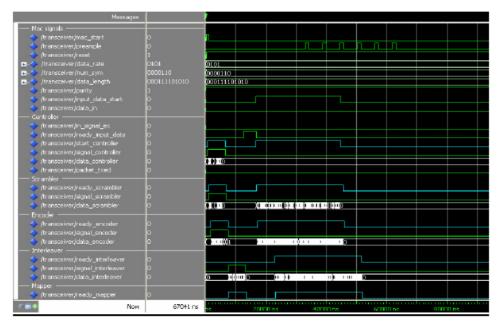

| 4.1.6. Post layout simulation                                                                                               | 64        |

|-----------------------------------------------------------------------------------------------------------------------------|-----------|

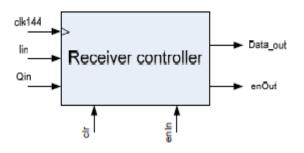

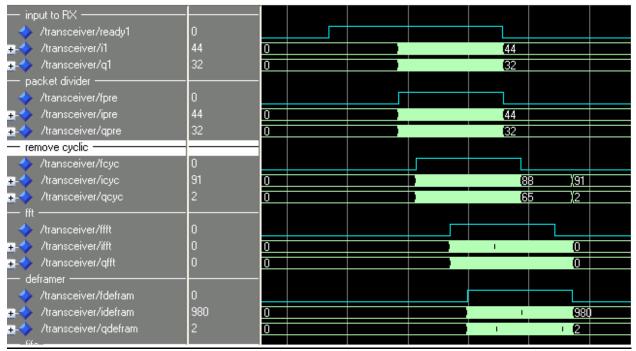

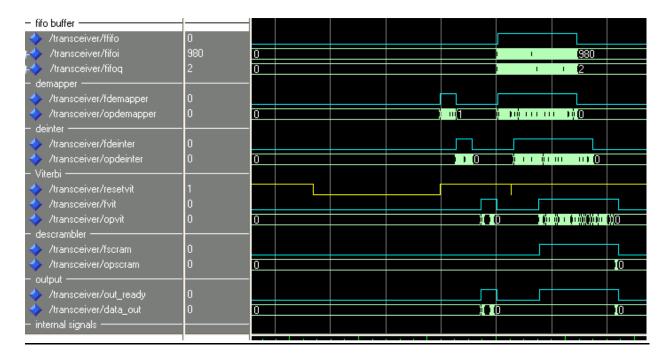

| 4.2. Receiver Controller Implementation                                                                                     | 65        |

| 4.2.2 Introduction                                                                                                          | 65        |

| 4.2.2 Structure                                                                                                             | 67        |

| 4.2.3 Post Layout Simulation                                                                                                | 68        |

| Chapter5. Synchronization                                                                                                   |           |

| 5.1 Timing Synchronization                                                                                                  |           |

| 5.1.1 Packet Detection                                                                                                      |           |

| 5.1.1.1 Double Sliding Window Packet Detection                                                                              |           |

| 5.1.1.2. Using the Structure of the Preamble for Packet Detection: (Delay and Corr                                          | elate) 77 |

| 5.2 Residual Phase Error Correction Using CORDIC Algorithm                                                                  | 85        |

| 5.2.1 Introduction                                                                                                          | 85        |

| 5.2.2 Block Diagram for Our phase Correction Implementation                                                                 |           |

| 5.2.3 Flow Chart for Our Design Implementation                                                                              |           |

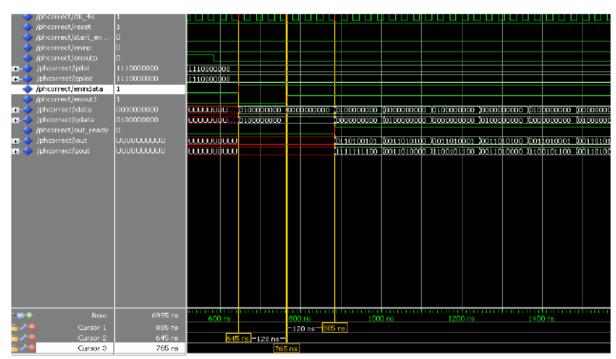

| 5.2.4 Simulation for the Phase Correction Implementation                                                                    |           |

| 5.2.5 Design performance                                                                                                    |           |

| Chapter6. System Implementation                                                                                             |           |

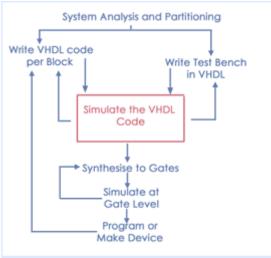

| 6.1 Design Flow using VHDL                                                                                                  |           |

| 6.1.1 System-level Verification                                                                                             |           |

| 6.1.2 RTL design and test-bench creation                                                                                    |           |

| 6.1.3 RTL verification (70% of design time at RTL)                                                                          |           |

| 6.1.4 Look-ahead Synthesis                                                                                                  |           |

| 6.2 Quartus II                                                                                                              |           |

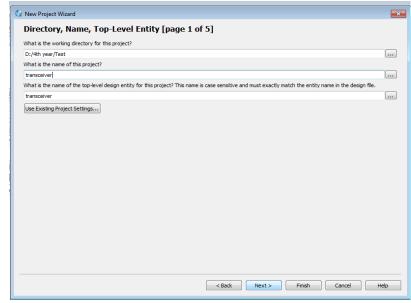

| 6.2.1 Creating project:                                                                                                     |           |

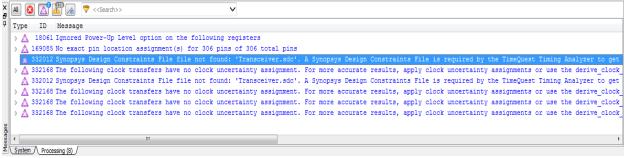

| 6.2.2 Managing Timing Constraints:                                                                                          |           |

| 6.2.3 Customizing Internal Memory IP Cores                                                                                  |           |

| 6.3 Function simulation using ModelSim                                                                                      |           |

| 1- Open the Design >> write in the Transcript Window these steps:                                                           |           |

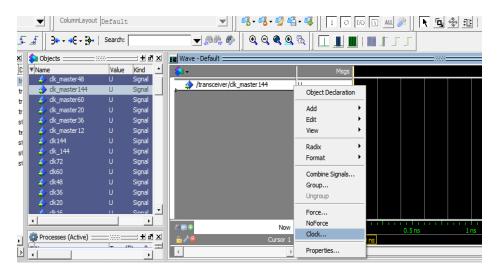

| 2-Create a Stimulus. First thing we need to do is to create a stimulus on our inpuction click on Add Wave >>click on Clock. | -         |

| 6.4 Verification on FPGA kit                                                                                                |           |

| 6.6 Introduction to Nios Development Board and Stratix III FPGA:                                                            | 102       |

|                                                                                                                             |           |

| Chapter7. Optical Fibers                                                      | 105       |

|-------------------------------------------------------------------------------|-----------|

| 7.1 introduction                                                              | 105       |

| 7.2 Optical fiber advantages                                                  | 105       |

| 7.3 Basic Fiber Optic Communication System                                    | 107       |

| 7.4 How Fiber Works                                                           | 107       |

| 7.5 How to Choose Optical Fiber Single-Mode Fiber Performance Characteristics | 109       |

| 7.6 Single-Mode Propagation                                                   | 110       |

| 7.6.1 Single-Mode Characteristics                                             | 111       |

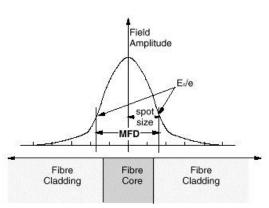

| 7.6.1.1 Mode Field Diameter (MFD) and Spot Size                               | 111       |

| 7.6.1.2 Field Strength at the Fiber End                                       | 111       |

| 7.61.3 Bend Loss in Single-Mode Fiber                                         | 112       |

| 7.6.1.4 Cutoff Wavelength                                                     | 112       |

| Chapter8. OFDM Over Optical Access Network                                    | 114       |

| 8.1 Introduction                                                              | 114       |

| 8.2 Light Fundamentals                                                        | 115       |

| 8.3 Wave Division Multiplexing Technique (WDM)                                | 116       |

| 8.4. Direct Detection OFDM                                                    | 117       |

| 8.5. Effective Wavelengths In Optical Transmissions                           | 118       |

| 8.6 Difference Between RF OFDM and OFDM Over Optical Channel                  | 119       |

| 8.7. FUTURE WORK                                                              | 119       |

| 8.7.1 Principle of Coherent Optical OFDM                                      | 119       |

| 8.8 difference between OFDM with optical fiber channel and CO-OFDM            | 120       |

| Chapter9. Opti-System                                                         | 123       |

| 9.1. Introduction                                                             | 123       |

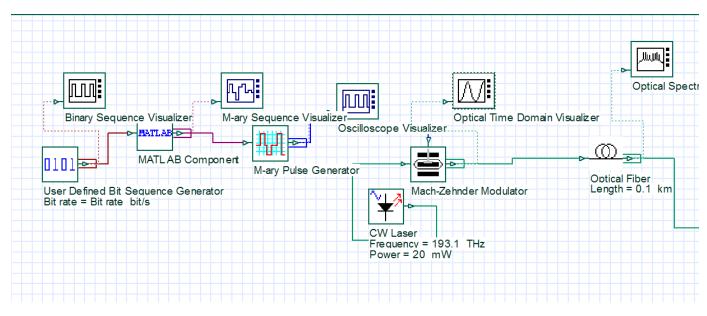

| 9.2 Simulation Main Blocks                                                    | 124       |

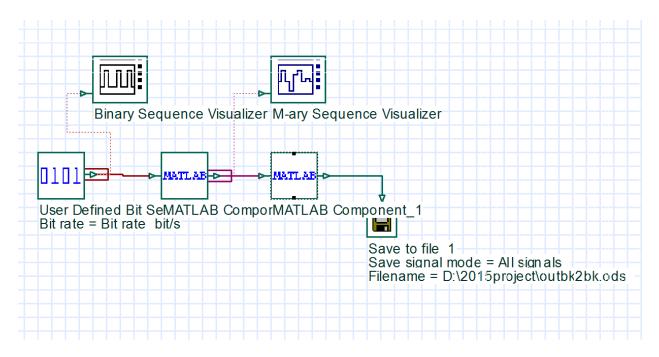

| 9.2.1 User defined Bit Sequence Block:                                        | 124       |

| 9.2.2 MATLAB Block:                                                           | 125       |

| 9.2.3 M-ary Pulse Generator:                                                  | 125       |

| 9.2.4 Mach-Zender Modulator:                                                  | 126       |

| 9.2.5 Optical Fiber:                                                          | 127       |

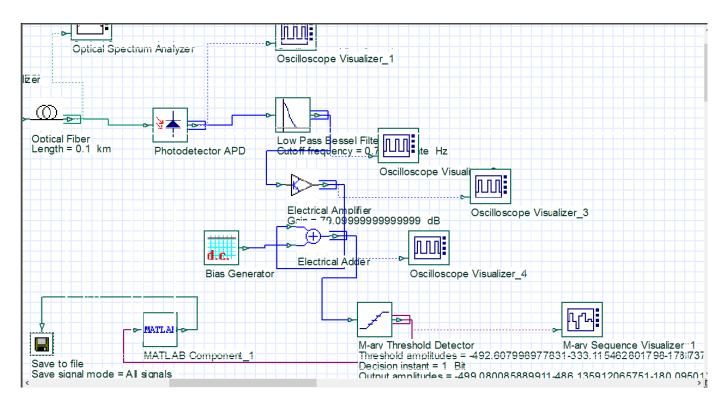

| 9.2.6 Photo-Detector:                                                         | 127       |

| 9.2.7 Low Pass Bessel Filter:                                                 | 127       |

| OFDM OVER OPTICAL ACCESS NETWORK                                              | VI   Page |

| 9.2.7 Electrical amplifiers:                                            | 127  |

|-------------------------------------------------------------------------|------|

| 9.2.9 DC Offset Block and Electrical Adder:                             | 127  |

| 9.2.10 M-ary Threshold Detector:                                        | 128  |

| 9.3. Schematic                                                          | 128  |

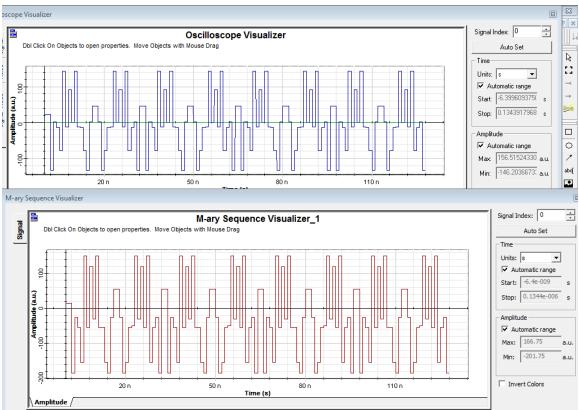

| 9.3.1 Back To Back testing                                              | 128  |

| 9.3.1.1. 1 <sup>st</sup> step: Testing the System back to back:         | 128  |

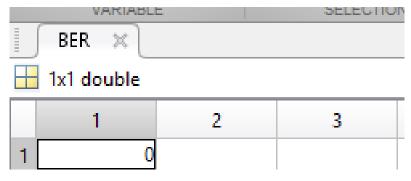

| 9.3.1.2. Results                                                        | 128  |

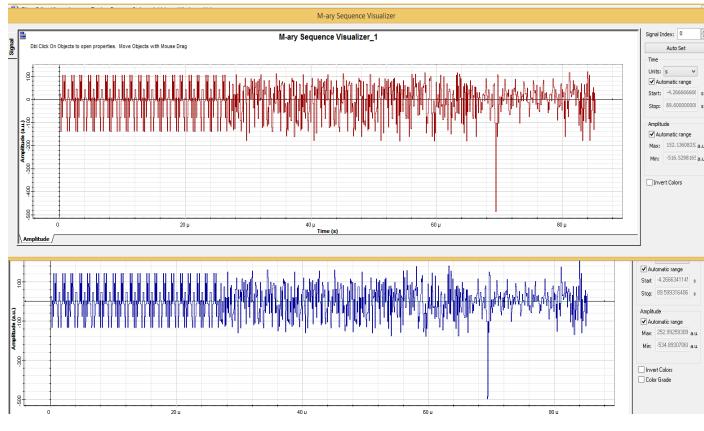

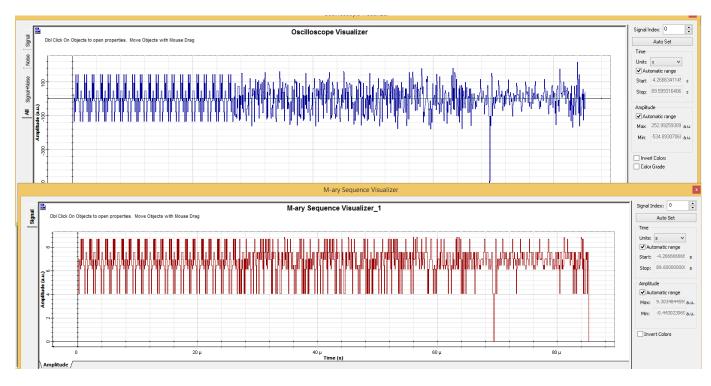

| 9.3.2. 2 <sup>nd</sup> , Testing the system with 100 m fibers length    | 129  |

| 9.3.2.1. System Schematic                                               | 129  |

| 9.3.2.2. Results                                                        | 130  |

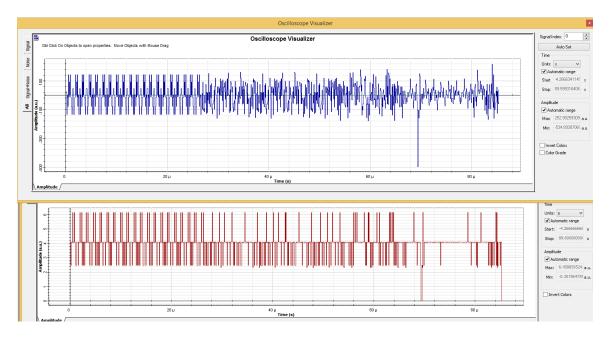

| Data sent from transmitter bock VS data received at the receiver block: | 131  |

| 1-Opti-System Block visualizer at 30km 128 bit sequence length          | XI   |

| Before channel vs before receiver                                       | XI   |

| Simulations at 80 db                                                    | XI   |

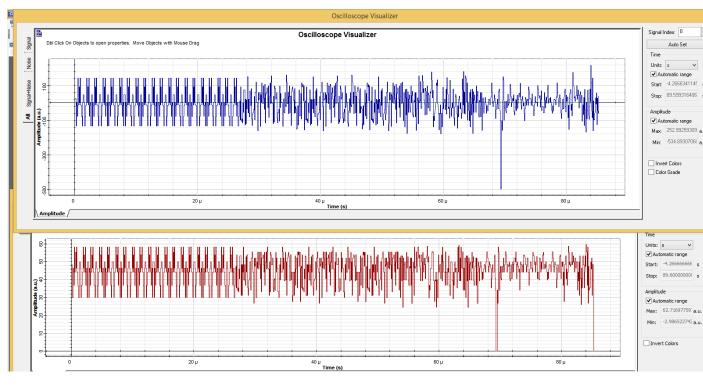

| 2-Opti-System Block visualizer at 90km 1024 bit sequence length         | XI   |

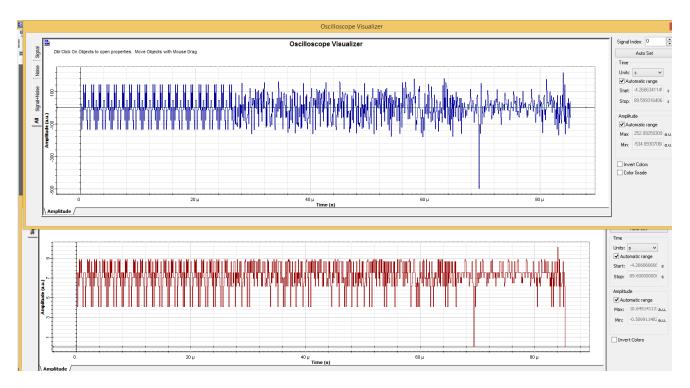

| 3-Opti-System Block visualizer at 100km 1024 bit sequence length        | XII  |

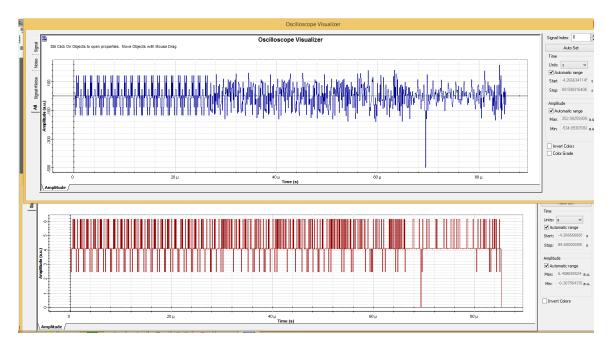

| At 100 db gain                                                          | XIII |

| 1-Opti-System Block visualizer at 100km 1024 bit sequence length        | XIII |

| 2-Opti-System Block visualizer at 140km 1024 bit sequence length        | XIV  |

| 3-Opti-System Block visualizer at 150km 1024 bit sequence length        | XV   |

| 4-Opti-System Block visualizer at 170km 1024 bit sequence length        | XVI  |

| Sample Opti-system Matlab code                                          | XVII |

| References                                                              | XX   |

#### Table of Figures

| Figure 1 OFDM block diagram                                                       | 6    |

|-----------------------------------------------------------------------------------|------|

| Figure 2 parallel to series converter                                             | 7    |

| Figure 3 16-QAM Constellation                                                     | 7    |

| Figure 4 IFFT description                                                         | 8    |

| Figure 5 OFDM Frame with Guard Time                                               | 9    |

| Figure 6 Inter-Carrier Interference (ICI)                                         | 9    |

| Figure 7 Adding Cyclic Extension                                                  | 9    |

| Figure 8 Block diagram of OFDM                                                    | . 16 |

| Figure 9 Block diagram of WIFI                                                    | . 17 |

| Figure 10 Data scrambler                                                          | . 18 |

| Figure 11                                                                         | . 18 |

| Figure 12                                                                         | . 19 |

| Figure 13                                                                         | . 20 |

| Figure 14                                                                         | . 22 |

| Figure 15 Puncturing patterns of IEEE                                             | . 24 |

| Figure 16 Convolutional encoder (K=7)                                             | . 25 |

| Figure 17                                                                         | . 25 |

| Figure 18 An example of the bit stealing and bit insertion procedure (r=3/4,2/ 3) | . 27 |

| Figure 19                                                                         | . 28 |

| Figure 20                                                                         | . 29 |

| Figure 21 Rate dependent parameters                                               | . 31 |

| Figure 22                                                                         | . 31 |

| Figure 23 BPSK, QPSK, 16-QAM, and 64-QAM constellation bit encoding               | . 34 |

| Figure 24                                                                         | . 36 |

| Figure 25                                                                         | . 40 |

| Figure 26                                                                         | . 41 |

| Figure 27 The location of the pilots in the frame                                 | . 42 |

| Figure 28                                                                         | . 42 |

| Figure 29 Inputs and outputs of the IFFT block in the 802.11a WLAN standard       | . 43 |

| Figure 30                                                                         | . 44 |

| Figure 31 conversion from frequency domain to time domain in transmitter          | . 45 |

| Figure 32 conversion from time domain to frequency domain in receiver             | . 45 |

| Figure 33 output of the two operations back to back                               | . 45 |

| Figure 34 CFFT Block Diagram                                                      | . 47 |

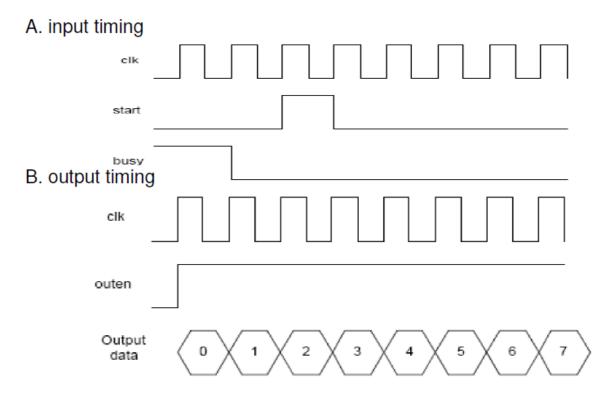

| Figure 35 Timing of input and output of CFFT core                                 | . 47 |

| Figure 36                                                                         | . 48 |

| Figure 37                                                                         | . 49 |

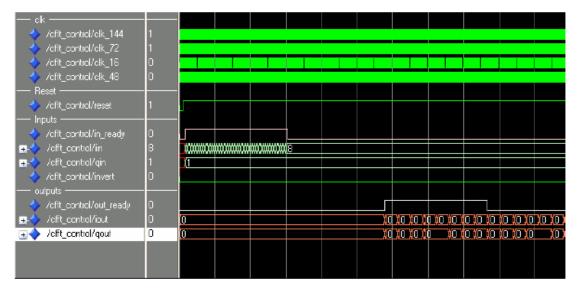

| Figure 38 post layout simulation of CFFT_Control component                        | . 50 |

| Figure 39 Input Zoom in                                                           | . 50 |

| Figure 40 Output Zoom in                                                          | . 50 |

| Figure 41 Matlab output for the same input                                     | . 51 |

|--------------------------------------------------------------------------------|------|

| Figure 42 OFDM symbol after cyclic extension                                   | . 52 |

| Figure 43                                                                      | . 52 |

| Figure 44                                                                      | . 53 |

| Figure 45                                                                      | . 54 |

| Figure 46                                                                      | . 55 |

| Figure 47                                                                      | . 55 |

| Figure 48                                                                      | . 56 |

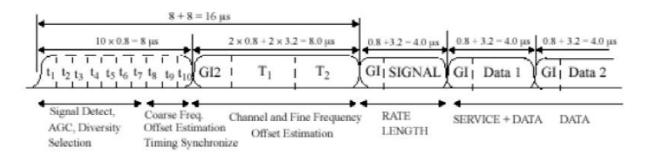

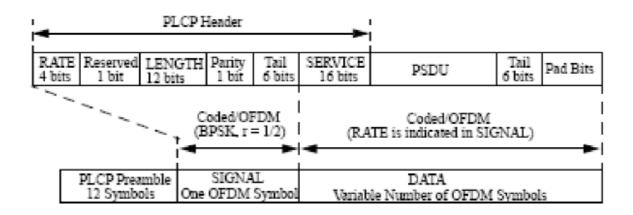

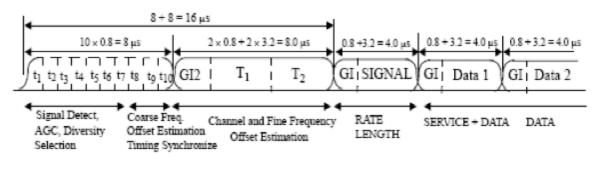

| Figure 49 Formation of WiFi Packet                                             | . 57 |

| Figure 50 OFDM training structure                                              | . 57 |

| Figure 51                                                                      | . 58 |

| Figure 52                                                                      | . 62 |

| Figure 53                                                                      | . 63 |

| Figure 54                                                                      | . 64 |

| Figure 55                                                                      | . 64 |

| Figure 56                                                                      | . 67 |

| Figure 57 post layout simulation of receiver controller                        | . 68 |

| Figure 58                                                                      | . 68 |

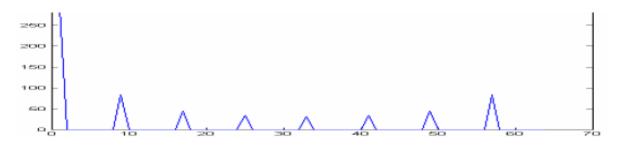

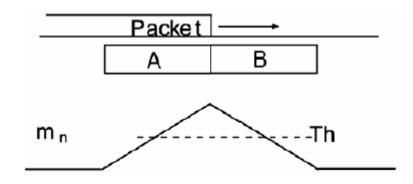

| Figure 59 The response of the double sliding window packet detection algorithm | . 71 |

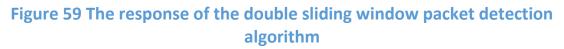

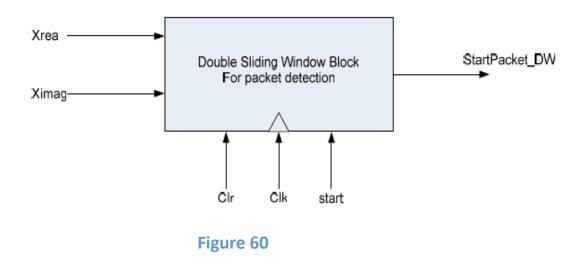

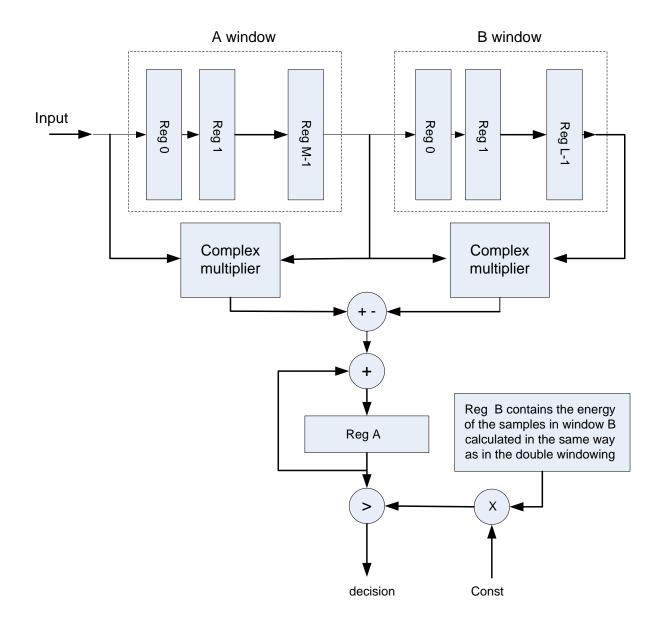

| Figure 60                                                                      | . 72 |

| Figure 61                                                                      | . 74 |

| Figure 62                                                                      | . 75 |

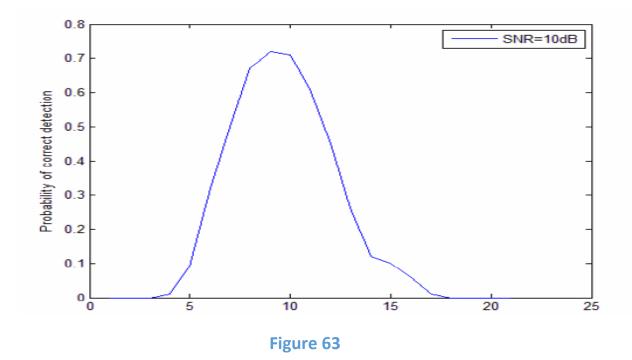

| Figure 63                                                                      | . 77 |

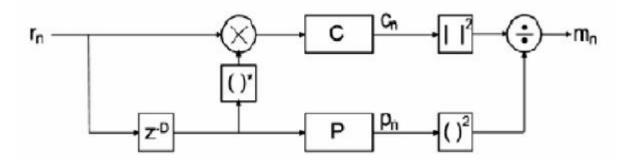

| Figure 64 Signal flow structure of the delay and correlate algorithm           | . 78 |

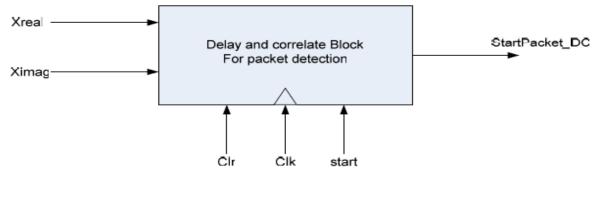

| Figure 65                                                                      | . 79 |

| Figure 66                                                                      | . 80 |

| Figure 67                                                                      | . 81 |

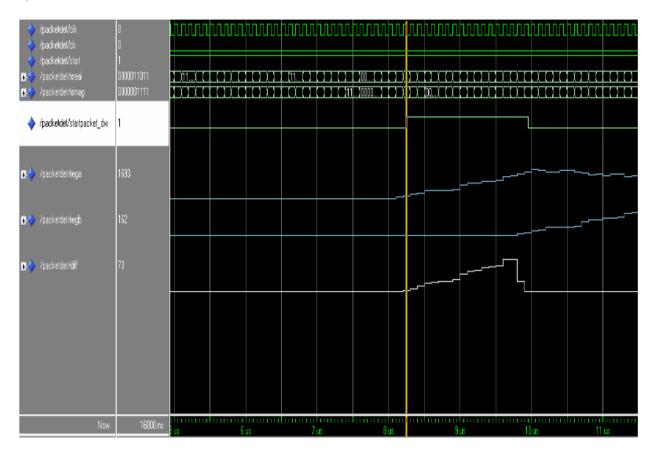

| Figure 68                                                                      | . 82 |

| Figure 69                                                                      | . 83 |

| Figure 70                                                                      | . 84 |

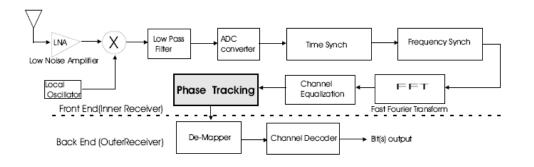

| Figure 71 OFDM receiver front end and synchronization architecture             | . 86 |

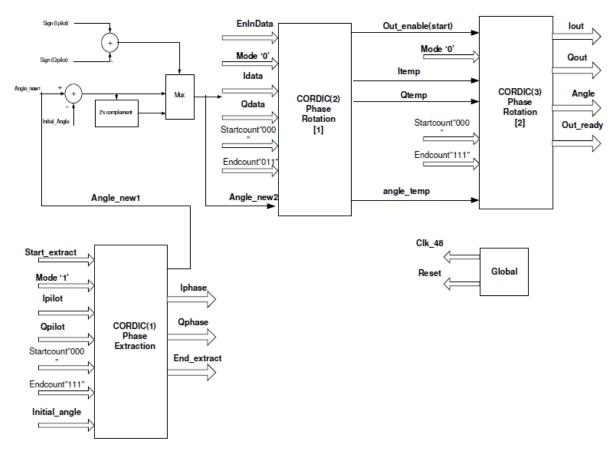

| Figure 72 Block Diagram for the phase correction Implementation using CORDIC   |      |

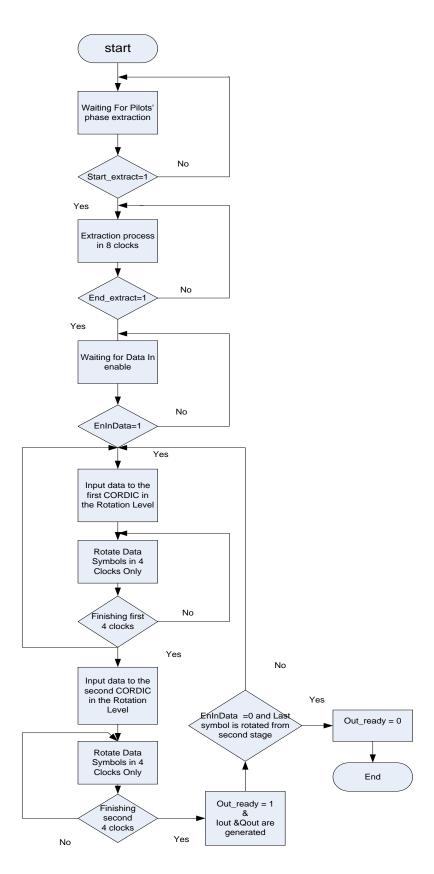

| Figure 73                                                                      |      |

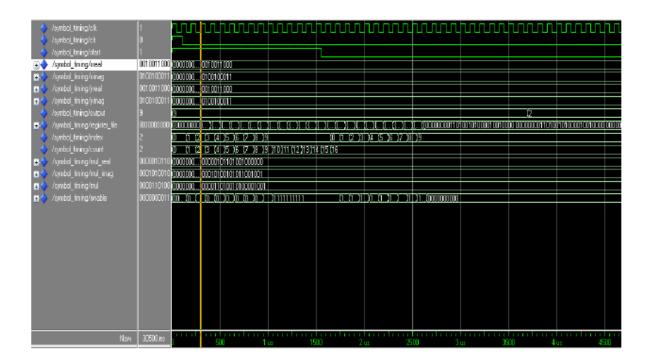

| Figure 74                                                                      | . 92 |

| Figure 75                                                                      |      |

| Figure 76                                                                      |      |

| Figure 77 Warning of Constrain file                                            |      |

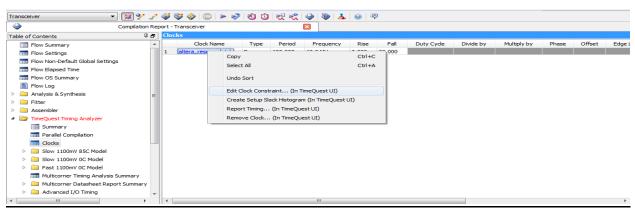

| Figure 78 Compilation Report Window                                            |      |

| Figure 79 Creating Clock                                                       |      |

| Figure 80                                                                      |      |

| Figure 81                                                                      |      |

| Figure 82                                                                      |      |

| ····                                                                           |      |

| Figure 83                                                  |      |

|------------------------------------------------------------|------|

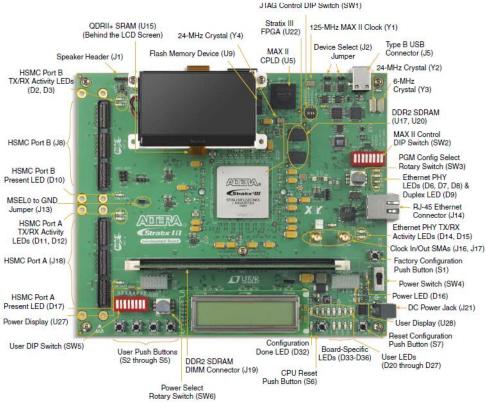

| Figure 84 Stratix III kit                                  | 102  |

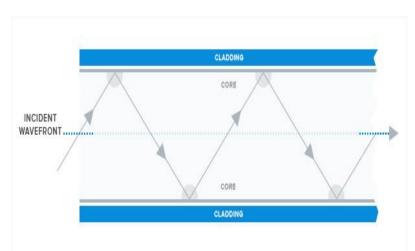

| Figure 85 Data transmission in fibers                      | 107  |

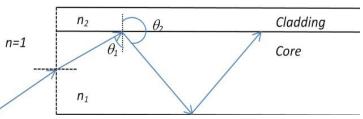

| Figure 86 Total reflection in optical fibers               | 108  |

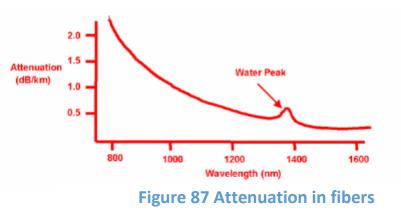

| Figure 87 Attenuation in fibers                            | 109  |

| Figure 88 Signal amplitude as distance increases in fibers | 109  |

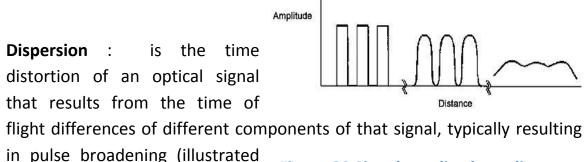

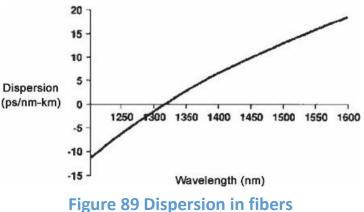

| Figure 89 Dispersion in fibers                             | 110  |

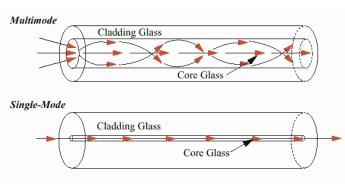

| Figure 90 Fiber operating modes                            | 111  |

| Figure 91 Single fiber bend loss                           | 112  |

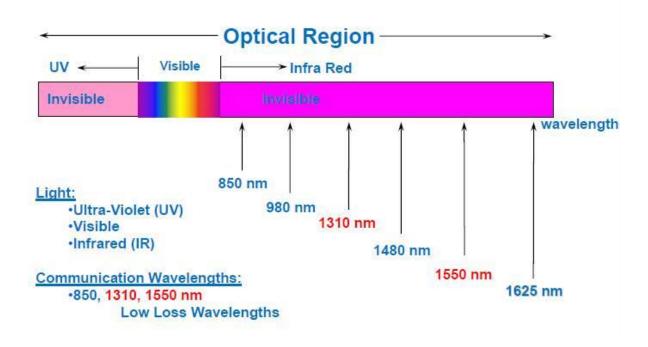

| Figure 92 Optical region (RCDD)                            | 115  |

| Figure 93 Light reflection and refraction (htt31)          | 116  |

| Figure 94 Wavelength division multiplexing technique       | 116  |

| Figure 95 Power distribution in WDM                        | 117  |

| Figure 96 Wave lengths in optical transmission             |      |

| Figure 97 up-converter/down-converter                      | 120  |

| Figure 98 User defined binary sequence block configuration | 124  |

| Figure 99 MATLAB block configuration                       | 125  |

| Figure 100. Mach-Zehnder modulator                         | 126  |

| Figure 101 Back to black testing                           | 128  |

| Figure 102 Back to back BER results                        | 129  |

| Figure 103 100 m test- Transmitter blocks                  | 129  |

| Figure 104 100m test-receiver blocks                       | 130  |

| Figure 105 100m BER results                                | 130  |

| Figure 106 Data sent before channel and after              | 131  |

| Figure 107                                                 | XI   |

| Figure 108                                                 | XII  |

| Figure 109                                                 | XIII |

| Figure 110                                                 | XIV  |

| Figure 111                                                 | XV   |

| Figure 112                                                 | XVI  |

| Figure 113                                                 | XVII |

#### Table of Tables

| Table 3. 1                                                | . 24 |

|-----------------------------------------------------------|------|

| Table 3. 2 Modulation-dependent normalization factor KMOD | . 33 |

| Table 3. 3 BPSK encoding table                            | . 35 |

| Table 3. 4 QPSK encoding table 5 QPSK encoding table      | . 35 |

| Table 3. 5 16-QAM encoding table                          | . 35 |

| Table 3. 6 64-QAM encoding table                          | . 36 |

| Table 4. 1                                                                    | 61  |

|-------------------------------------------------------------------------------|-----|

|                                                                               |     |

| Table 5. 1 illustration of the probability of correct detection for different |     |

|                                                                               |     |

| Table6. 1                                                                     | 100 |

## CHAPTER 1

## CHAPTER 1

#### Chapter 1: Introduction

#### 1.1 Motivation & project definition

OFDM over optical access network, OFDM implemented on FPGA over optical access network rather than wireless network. As The combination of radio over fiber (RoF) and orthogonal frequency division multiplexing (OFDM) techniques has resulted in a high-data-rate at lower cost in the last mile of wireless networks.

The purpose of implementing this system is to increase data rate as the wireless system OFDM increased the data rate to the range of 1Gbps, and as the demand for high speed data rate and high capacity of bandwidth has increased due to recent advances in technology in the access networks bandwidth, so a new way of thinking started. These trials aims to increase the data rate in the range of tens or hundreds of Gbps for data transmission, regardless the transmission technique used with the best modulation scheme to achieve the highest possible signal to noise ratio (SNR) and a higher accuracy.

Increasing data rate to higher range than the range of 4G communication systems which operating on the range of 1G, makes it possible to reach to the fifth generation of communication systems 5G.

The integration of fiber optics and wireless communication systems has many advantages. Such as, increasing data rate and lower power consumption with higher bandwidth than that achieved with wireless communications. Also, it helps to send high data rates to long distances without the need to add repeaters or to regenerate the signal (Fuertes, 2005-03-22).

#### 1.2 OFDM

Orthogonal Frequency Division Multiplexing (OFDM) is a multicarrier modulation technique which is common used nowadays in wireless network such as 4G mobile communications, it's also used for digital television and audio broadcasting. Long distance communication is improved using OFDM, cause of its ability to cope with severe channel conditions without complex equalization filters and its ability to eliminate the inter-symbol interference (ISI).

#### 1.2.1 Introduction

Orthogonal frequency-division multiplexing (OFDM) is a method of digital modulation in which a signal is split into several narrowband channels at different frequencies. Recently, a worldwide convergence has occurred for the use of Orthogonal Frequency Division Multiplexing (OFDM) in wireless communication applications as an emerging technology for high data rates.

Wireless communication is having the fastest growth phase because of unprecedented evolution in the field. Orthogonal frequency-division multiplexing (OFDM) is a method of digital modulation in which a signal is split into several narrowband channels at different frequencies. OFDM has been adopted by several technologies such as Asymmetric Digital Subscriber Line (ADSL) services, IEEE 802.11a/g, IEEE 802.16a, Digital Audio Broadcast (DAB), and digital terrestrial television broadcast: DVD in Europe, ISDB in Japan 4G, IEEE 802.11n, IEEE 802.16, and IEEE 802.20.

The principle of work of OFDM that it converts a frequency-selective channel into a parallel collection of frequency flat sub channels which makes it robust against large delay spreads. OFDM provides many advantages over this conventional technique. The subcarrier frequencies of OFDM are chosen so that the signals are mathematically orthogonal over one symbol period. So the effect of inter-channel interference is eliminated.

#### 1.2.2. Brief History

The IEEE initiated the 802.11 project in 1990 with a scope "to develop a Medium Access Control (MAC) and Physical Layer (PHY) specification for wireless connectivity for fixed, portable, and moving stations within an area."

In 1997, IEEE first approved the 802.11 international interoperability standard. In 1999, the IEEE ratified the 802.11a and the 802.11b wireless networking communication standards. The goal was to create a standards-based technology that could span multiple physical encoding types, frequencies, and applications. The 802.11a standard uses orthogonal frequency division multiplexing (OFDM) to reduce interference. This technology uses the 5 GHz frequency spectrum and can process data at up to 54 Mbps.

#### 1.2.1.1 OFDM Advantages

Because using wireless environment fading usually impairs signals and multipath delay .In such wireless channels extreme fading of the signal amplitude occurs and Inter Symbol Interference (ISI), multipath effects due to the frequency selectivity of the channel appears at the receiver side, a considerable delay and losses will lead to a high probability of errors so the system's overall performance becomes very poor.

OFDM advantages are its robustness against channel dispersion and the ease of phase and channel estimation in a time-varying environment. One of the major strengths of the orthogonal frequency-division multiplexing (OFDM) modulation format is its rich variation and ease of adaption to a wide range of applications. OFDM has although the ability to control the signal as hard as it is possible. As it;

- Makes efficient use of the spectrum by allowing overlap.

- By dividing the channel into narrowband flat fading sub-channels, OFDM is more resistant to frequency selective fading than single carrier systems are.

- Eliminates ISI and IFI through use of a cyclic prefix.

- Using adequate channel coding and interleaving one can recover symbols lost due to the frequency selectivity of the channel.

- Channel equalization becomes simpler than by using adaptive equalization techniques with single carrier systems.

- It is possible to use maximum likelihood decoding with reasonable complexity.

- OFDM is computationally efficient by using FFT techniques to implement the modulation and demodulation functions.

- Is less sensitive to sample timing offsets than single carrier systems are.

- Provides good protection against channel interference and impulsive parasitic noise.

#### 1.2.1.2 OFDM disadvantages

The essential disadvantages of OFDM are its high peak-to-average power ratio (PAPR) and sensitivity to frequency and phase noise, the main reason of system sensitivity as it requires high frequency and time synchronization accuracy between transmitter and receiver. OFDM is very sensitive for the error of frequency and time synchronization, which means frequency and time offset.

- The OFDM signal has a noise like amplitude with a very large dynamic range, therefore it requires RF power amplifiers with a high peak to average power ratio.

- It is more sensitive to carrier frequency offset and drift than single carrier systems are due to leakage of the DFT.

#### 1.2.2 Orthogonality and OFDM

As the orthogonality is the principle of work of OFDM, it is important to define the orthogonality concept used in OFDM. If the FDM system has the ability to use a set of subcarriers that are orthogonal to each other, a higher level of spectral efficiency could have been achieved using FDM (frequency division multiplexing). The use of orthogonal subcarriers would allow the subcarriers' spectra to overlap, thus increasing the spectral efficiency. Orthogonality means: If two random processes are uncorrelated, then they are orthogonal. The transmitted signal at the transmitted is divided into several signals to be carried on OFDM sub-carriers which are mathematically orthogonal. Then at the receiver side, the signals from the subcarriers are then combined to form an estimate of the source signal from the transmitter. The orthogonal and uncorrelated nature of the subcarriers is exploited in OFDM with powerful results.

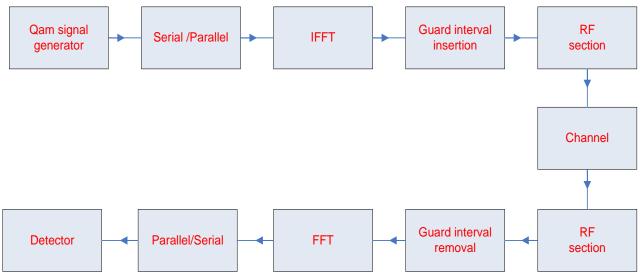

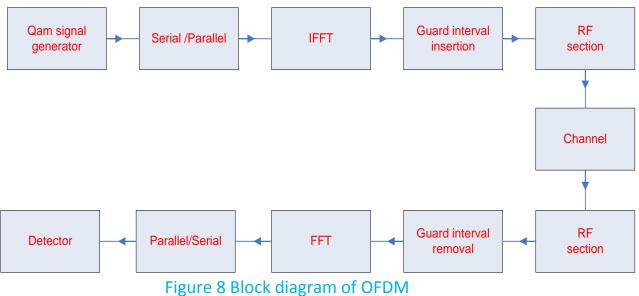

Figure 1 OFDM block diagram

#### Blocks in details:

#### 1.3.1 Modulation and Demodulation of Data

Modulation is a process of mixing a signal which contains information data with a sinusoid to produce a new signal. This new signal, will have certain benefits over an un-modulated signal .The process by which information signals, analog or digital, are transformed into waveforms suitable for transmission across the channel.

After bit interleaving, the data bits are entered serially to the constellation mapper. The data bits shall be modulated by using 16-QAM modulation; the encoded and interleaved binary serial input data shall be divided into groups of NBPSC (4) bits and converted into complex numbers representing 16-QAM constellation points.

#### 1.3.2 Serial to Parallel Converter

The input serial data stream is formatted into the word size required for transmission, e.g. 4 bits/word for QAM, and shifted into a parallel format. The data is then transmitted in parallel by corresponding each data word to one carrier in the transmission.

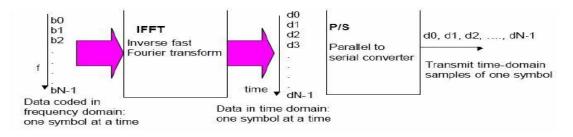

#### 1.3.3 IFFT/FFT

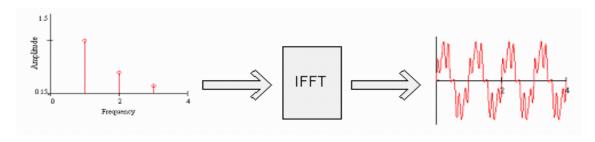

Since the OFDM signal is in the time domain, so IFFT is used in the transmitter, which can convert frequency domain samples to time domain samples. The IFFT is useful for OFDM because it generates samples of a waveform with frequency components satisfying orthogonality conditions. Then, the parallel to serial block creates the OFDM signal by sequentially outputting the time domain samples. This operation ensures that subcarriers do not interfere with one another.

Receiver performs the inverse of the transmitter.

Figure 4 IFFT description

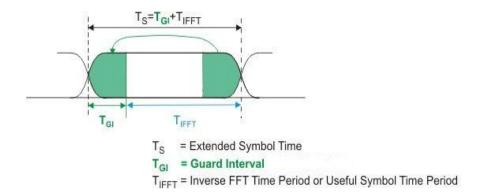

#### 1.3.4 Guard Interval

The guard interval is used to eliminate inter-symbol and inter-carrier interference (ISI) completely.

Guard time is chosen larger than the expected delay spread such that the multipath component for one symbol can't interfere with the next symbol.

#### Figure 5 OFDM Frame with Guard Time

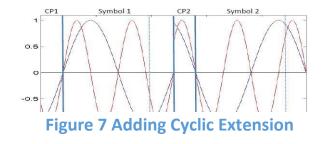

#### 1.3.5 Cyclic Prefix

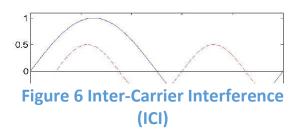

To eliminate ICI (Inter-Carrier Interference) which is the cross talk between different subcarriers which means they are no longer orthogonal.

OFDM symbols are cyclically extended in the guard time. This

ensures that delayed replicas of the OFDM symbol always have an integer number of cycles within the FFT interval.

# Chapter 2

## CHAPTER 2

#### Chapter2.1 Introduction to WI-FI

#### 2.1.1 Introduction

WLAN technology and the WLAN industry date back to the mid-1980s when the Federal Communications Commission (FCC) first made the RF spectrum available to industry. During the 1980s and early 1990s, growth was relatively slow. Today, however, WLAN technology is experiencing tremendous growth. The key reason for this growth is the increased bandwidth made possible by the IEEE 802.11 standard. A brief introduction to the 802.11 and WLAN technology follows.

#### 2.1.2 Brief History

The IEEE initiated the 802.11 project in 1990 with a scope "to develop a Medium Access Control (MAC) and Physical Layer (PHY) specification for wireless connectivity for fixed, portable, and moving stations within an area." In 1997, IEEE first approved the 802.11 international interoperability standard. In 1999, the IEEE ratified the 802.11a and the 802.11b wireless networking communication standards. The goal was to create a standards-based technology that could span multiple physical encoding types, frequencies, and applications. The 802.11a standard uses orthogonal frequency division multiplexing (OFDM) to reduce interference. This technology uses the 5 GHz frequency spectrum and can process data at up to 54 Mbps.

#### 2.1.3 Frequency and Data Rates

IEEE developed the 802.11 standards to provide wireless networking technology like the wired Ethernet that has been available for many years. The IEEE 802.11a standard is the most widely adopted member of the 802.11 WLAN family. It operates in the licensed 5 GHz band using OFDM technology. The popular 802.11b standard operates in the unlicensed 2.4 GHz-2.5 GHz Industrial, Scientific, and Medical (ISM) frequency band using a direct sequence spread-spectrum technology. The ISM band has become popular for wireless communications because it is available worldwide. The

802.11b WLAN technology permits transmission speeds of up to 11 Mbits/second.

#### 2.1.4 Architecture of 802.11

The IEEE 802.11 standard permits devices to establish either peer-topeer (P2P) networks or networks based on fixed access points (AP) with which mobile nodes can communicate. Hence, the standard defines two basic network topologies: the infrastructure network and the ad hoc network. The infrastructure network is meant to extend the range of the wired LAN to wireless cells. A laptop or mobile device may move from cell to cell (from AP to AP) while maintaining access to the resources of the LAN. A cell is the area covered by an AP and is called a "basic service set" (BSS). The collection of all cells of an infrastructure network is called an extended service set (ESS). This first topology is useful for providing wireless coverage of large areas. By deploying multiple APs with overlapping coverage areas, organizations can achieve broad network coverage. WLAN technology can be used to replace wired LANs totally and to extend LAN infrastructure. A WLAN environment has wireless client stations that use radio modems to communicate to an AP.

Client stations are generally equipped with a wireless network interface card (NIC) that consists of the radio transceiver and the logic to interact with the client machine and software. An AP comprises essentially a radio transceiver on one side and a bridge to the wired backbone on the other. The AP, a stationary device that is part of the wired infrastructure, is analogous to a cell-site (base station) in cellular communications. All communications between the client stations and between clients and the wired network go through the AP.

#### 2.1.5 Wireless LAN Components

A WLAN comprises two types of equipment: a wireless station and an access point. A station, or client, is typically a laptop or notebook personal computer (PC) with a wireless NIC. A WLAN client may also be a desktop or handheld device, or equipment within a kiosk on a manufacturing floor or other publicly accessed area. Wireless laptops and notebooks - "wireless enabled" - are identical to laptops and notebooks except that they use wireless NICs to connect to access points in the network. The wireless NIC is commonly inserted in the client's Personal Computer Memory Card International Association (PCMCIA) slot or Universal Serial Bus (USB) port. The NICs use radio signals to establish connections to the WLAN. The AP, which acts as a bridge between the wireless and wired networks, typically comprises a radio, a wired network interface such as 802.3, and bridging software. The AP functions as a base station for the wireless network, aggregating multiple wireless stations onto the wired network.

#### 2.1.6 Range

The reliable coverage range for 802.11 WLANs depends on several factors, including data rate required and capacity, sources of RF interference, physical area and characteristics, power, connectivity, and antenna usage. Theoretical ranges are from 29 meters (for 11 Mbps) in a closed office area to 485 meters (for 1 Mbps) in an open area. However, through empirical analysis, the typical range for connectivity of 802.11 equipment is approximately 100 meters (about 320 ft.) indoors. Special high-gain antennas can increase the range to several miles make WLAN the ideal technology for many applications. APs may also provide a "bridging" function. Bridging connects two or more networks together and allows them to communicate - to exchange network traffic. Bridging involves either a point-to-point or a multipoint configuration. In a point-to-point architecture, two LANs are connected to each other via the LANs' respective APs. In multipoint bridging, one subnet on a LAN is connected to several other subnets on another LAN via each subnet AP.

For example, if a computer on Subnet A needed to connect to computers on Subnets B, C, and D, Subnet A's AP would connect to B's, C's, and D's respective APs. Enterprises may use bridging to connect LANs between different buildings on corporate campuses. Bridging AP devices are typically placed on top of buildings to achieve greater antenna

reception. The typical distance over which one AP can be connected wirelessly to another by means of bridging is approximately 2 miles. This distance may vary depending on several factors including the specific receiver or transceiver being used

#### 2.1.7 Benefits

**User Mobility**: Users can access files, network resources, and the Internet without having to physically connect to the network with wires. Users can be mobile yet retain high-speed, real time access to the enterprise LAN.

**Rapid Installation**: The time required for installation is reduced because network connections can be made without moving or adding wires, or pulling them through walls or ceilings, or making modifications to the infrastructure cable plant.

**Flexibility**: Organizations can enjoy the flexibility of installing and taking down WLANs in locations as necessary. Users can quickly install a small WLAN for temporary needs such as a conference, trade show, or standards meeting.

**Scalability**: WLAN network topologies can easily be configured to meet specific application and installation needs and to scale from small peer-to-peer networks to very large enterprise networks that enable roaming over a broad area.

Because of these fundamental benefits, the WLAN market has been increasing steadily over the past several years, and WLANs are still gaining in popularity. WLANs are now becoming a viable alternative to traditional wired solutions.

## Chapter 3

## CHAPTER 3

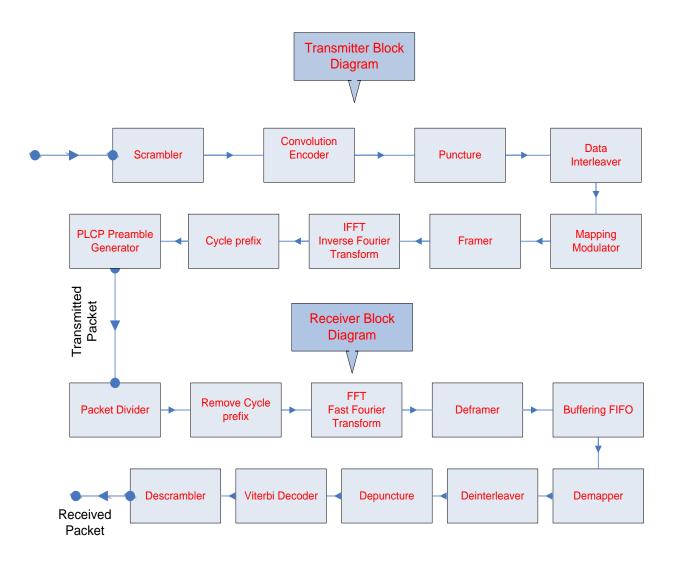

### Chapter3. System Explanation

### 3.1. Block Diagram

#### 3.2. Transmitter Blocks Implementation

All the transmitter and receiver block are synthesized and tested (post layout simulation) on STRATIX II EP2S60 (class, 2013).

#### 3.2.1. Scrambler

#### 3.2.1.1 Function of Block

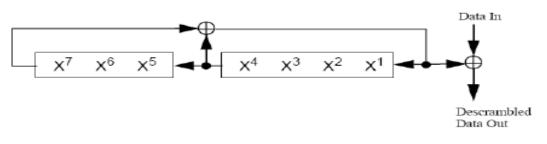

It is used to scramble the transmitted data , by using a generator polynomial S(x) where:

S(x) = x7 + x4 + 1

And this sequence is XOR with the transmitted data bit as seen in figure 10.

**Figure 10 Data scrambler**

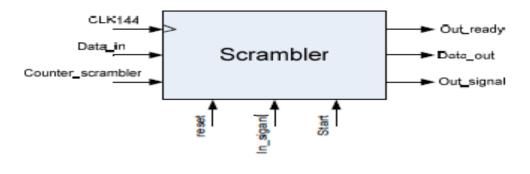

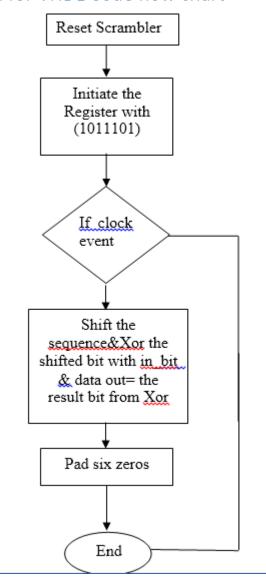

#### 3.2.1.2 Structure

Figure 11

Figure 12

#### Padding

According to the standard there are six zeros follow the data, those six scrambled "zero" bits following the "data" are replaced with six nonscrambled "zero" bits. Those bits return the convolutional encoder to the "zero state" and are denoted as "tail bits". The PPDU tail bit field shall be six bits of "0," which are required to return the convolutional encoder to the "zero state." This procedure improves the error probability of the convolutional decoder, which relies on future bits when decoding and which may be not be available past the end of the message. The PLCP tail bit field shall be produced by replacing six scrambled "zero" bits following the message end with six non-scrambled "zero" bits.

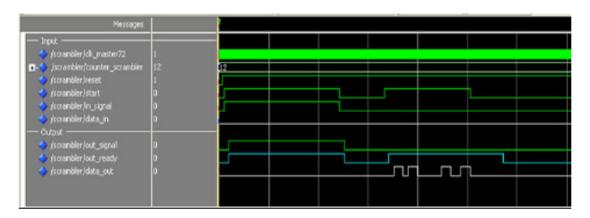

#### 3.2.1.4 Post Layout Simulation

#### Figure 13

#### 3.2.1.5 Performance measurement

| Logic utilization         | < 1%                  |

|---------------------------|-----------------------|

| Combinational ALUTs       | 112 / 48,352 ( < 1 %) |

| Dedicated logic registers | 31 / 48,352 ( < 1 %)  |

| Total registers           | 31                    |

| Total block memory bits   | 0 / 2,544,192 ( 0 %)  |

| Max freq                  | 250.69Mhz             |

#### 3.2.2 Encoder

#### 3.2.2.1 Introduction

Channel codes are a very important component of any modern digital communication system, and they make today's effective and reliable wireless communications possible.

The basic measure of channel coding performance is coding gain, which is usually measured in dBs as the reduction of required to achieve a certain bit error rate in AWGN channel. Hence, coding gain is the measure in the difference between the signal to noise ratio (SNR) levels between the uncoded system and coded system required to reach the same bit error rate (BER) levels when used with the error correcting code (ECC).

#### 3.2.2.2 Convolutional Codes

Convolutional codes are one of the mostly widely used channel codes in today's systems; all the major cellular systems (GSM, IS-95) in use today use convolutional channel codes. IEEE 802.11a and HiperLAN/2 WLAN standards also use convolutional error correcting code, and IEEE 802.11b includes an optional mode that uses them. Convolutional codes owe their popularity to good performance and flexibility to achieve different coding rates.

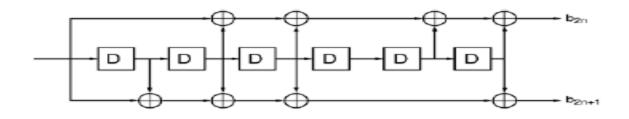

A convolutional code is defined by a set of connections between stages of one or more shift registers and the output bits of the encoder. The number of shift registers k is equal to the nominator of the code rate and the number of output bits n is equal to the denominator. The rate of a convolutional code is generally expressed as k/n . The number of connections required to describe a code is equal to the product of k and n. For each output bit there are k connections that define how the value of the output bit is calculated from the state of the shift registers. For example, Figure (14)shows the convolutional encoder used in IEEE 802.11a. This is a rate code 1/2 with connections 1338 and 1718. The connections are defined as octal numbers, the binary representations are 001 011 0112 and 001 111 0012. The octal notation is used to shorten the expressions, when connections for different convolutional codes are tabulated. From the binary notation, the structure of the encoder is easily constructed. The connections are aligned to the end of the shift register, and a value of 1 means that the shift register stage output is connected to one of the output bits of the encoder using a binary XOR operation. In Figure (14) the connection 1338 that defines values the even indexed bits b2n and the connection 1718 defines the values of the odd indexed bits b2n+1. Figure (14) state rate 1/2 convolutional encoder used in IEEE 802.11a.

Figure 14

The number of shift register elements determines how large a coding gain the convolutional code can achieve. The longer the shift registers, the more powerful the code is; unfortunately, the decoding complexity of the maximum likelihood Viterbi algorithm grows exponentially with the number of shift register elements. This complexity growth limits the currently used convolutional codes to eight shift register elements, and IEEE 802.11a uses only six, due to its very high speed data rates. The performance of a convolutional code is determined by the minimum free distance of the code. Free distance is defined using the Hamming distance that is equal to the number of position in which two code words are different. Free distance of a convolutional code is the minimum Hamming distance between two different code words. Before we can calculate the free distance of our encoder we may see first the different representations of the convolutional encoder.

#### 3.2.2.3 Puncturing Convolutional Codes

Usually communications systems provide a set of possible data rates; for example, IEEE 802.11a has eight different data rates: 6, 9, 12, 18, 24, 36, 48, and 54 Mbits/s. Now if the system could only change the data rate by adjusting the constellation size, and not the code rate, a very large number of different rates would be difficult to achieve as the number of constellations and the number of points in the largest constellation would grow very quickly. Another solution would be to implement several different convolutional encoders with different rates and change both the convolutional code rate and constellation. However this approach has problems in the receiver that would have to implement several different decoders for all the codes used. Puncturing is a very useful technique to generate additional rates from a single convolutional code. Puncturing was first discover by Cain, Clark, and Geist, and subsequently the technique was improved by Hagenauer. The basic idea behind puncturing is not to transmit some of the bits output by the convolutional encoder, thus increasing the rate of the code. This increase in rate decreases the free distance of the code, but usually the resulting free distance is very close to the optimum one that is achieved by specifically designing a convolutional code for the punctured rate. The receiver inserts dummy bits to replace the punctured bits in the receiver, hence only one encoder/decoder pair is needed to generate several different code rates.

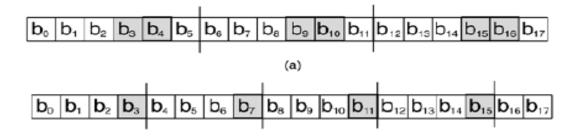

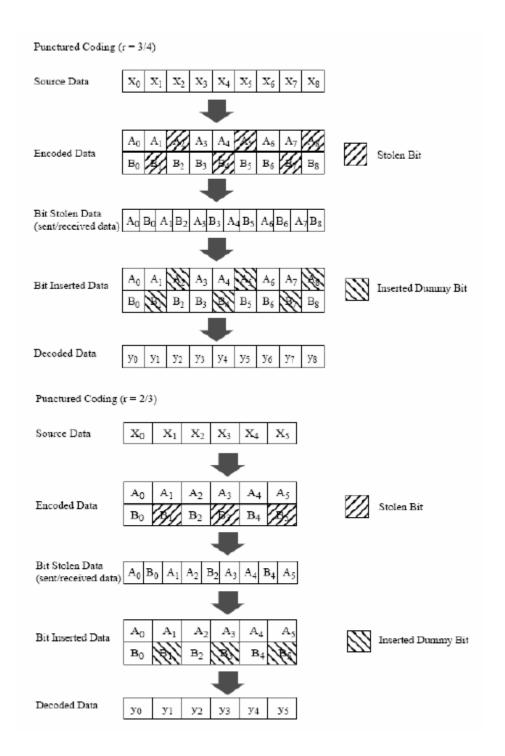

The bits that are not transmitted are defined by a puncturing pattern. Puncturing pattern is simply a set of bits that are not transmitted within a certain period of bits. Figure 28 shows the two different puncturing patterns of IEEE 802.11a. The pattern (a) is used to generate rate 3/4 code from the rate 1/2 mother convolutional code. This puncturing pattern has a period of six bits, and bits 3 and 4 are punctured (not transmitted) from each period.

The puncturing rate is equal to 4/6=2/3 and the overall code rate is equal to 1/2\*(2/3) = 3/4, since 2/3 of the original encoded bits are output from the puncture.

The other punctured code rate of IEEE 802.11a is a rate 2/3 code. The puncturing pattern is shown in Figure (15) has a period of 4 bits, and the fourth bit is punctured, the puncturing rate is, 3/4 hence the overall code rate is  $1/2^*(3/4) = 2/3$ .

**Figure 15 Puncturing patterns of IEEE**

Table 3.1 shows the free distances and the asymptotic coding gains of the three code rates used in IEEE 802.11a. The table also shows the optimum rate 3/4 and 2/3 codes; as you can see, the performance loss due to using punctured codes, instead of the optimum ones, is very small. The rate 1/2 is naturally the optimum code, because the original code is 1/2 a rate code. Therefore the table does not show the punctured free distance and coding gain values for this rate.

| Table 3.4. Free Ddistances of the 64 State Convolutional Codes Used in IEEE 802.11a |                       |      |                   |        |                     |      |                 |        |

|-------------------------------------------------------------------------------------|-----------------------|------|-------------------|--------|---------------------|------|-----------------|--------|

| Code<br>Rates                                                                       | Punctured<br>Distance | Free | Punctured<br>Gain | Coding | Optimum<br>Distance | Free | Optimum<br>Gain | Coding |

| $\frac{1}{2}$                                                                       | -                     |      | -                 |        | 10                  |      | 7.0 dB          |        |

| $\frac{2}{3}$                                                                       | 6                     |      | 6.0 dB            |        | 7                   |      | 6.7 dB          |        |

| $\frac{3}{4}$                                                                       | 5                     |      | 5.7 dB            |        | 6                   |      | 6.5 dB          |        |

#### **Table 3.1**

#### 3.2.2.4 Function of the Block

The IEEE 802.11a/b/g specification offers support for a variety of other modulation and coding alternatives. For example, the standard allows engineers to combine BPSK, QPSK, and 16-QAM modulations with convolution encoding (R = 1/2 and constraint length seven) to generate data rates of 6, 12, and 24 Mbps. All other combinations of encoding rates, including R = 2/3 and R = 3/4 combined with 64- QAM, are used to generate rates up to 54 Mbps, which are optional in the standard.

Figure 16 Convolutional encoder (K=7)

#### 3.2.2.5 Structure

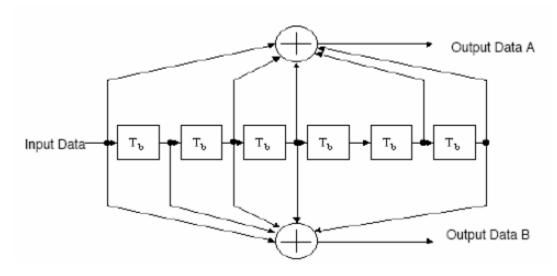

# 3.2.2.6. The VHDL code description

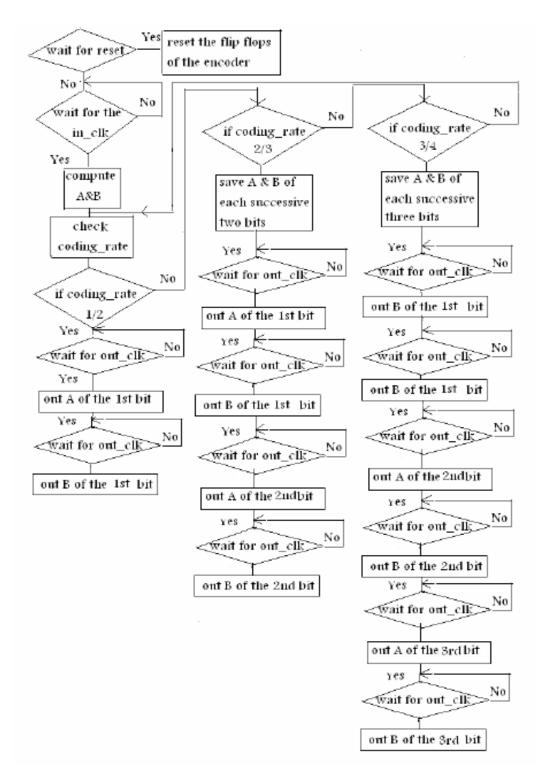

The encoder is formed by 6 flip flops where the input to the encoder is the input to the first flip flop and the output is A & B where, A<=inbit xor srg(4) xor srg(3) xor srg(1) xor srg(0); B<=inbit xor srg(5) xor srg(4) xor srg(3)xor srg(0); We will save the input to the encoder in a register with a variable size according to the coding rate: At rate 1/2 we don't need to use this register, at each clock of the in\_clk we will have a new inbit we will compute A and B at the same time and will out A with the 1st out clk and B will out with 2nd out clk. At rate 2/3 we will use a register with a size =4 bits , we will have a new inbit each in clk then compute A and B and save them in the register then out A of the 1st bit with the 1st out clk, out B of the same bit at the 2nd out clk, out A of the 2nd bit at the 3rd out clk and ignore B of this bit. At rate 3/4 we will use a register with a size =6 bits ,we will have a new inbit each in clk then compute A and B and save them in the register then out A of the 1st bit with the 1st out clk, out B of the same bit at the 2nd out\_clk ,out A of the 2nd bit at the 3rd out\_clk and ignore B of this bit then out B of the 3rd bit at the 4th out clk and ignore A of this bit.

Figure 18 An example of the bit stealing and bit insertion procedure (r=3/4,2/3)

#### 3.2.2.7. Flow chart of the encoder

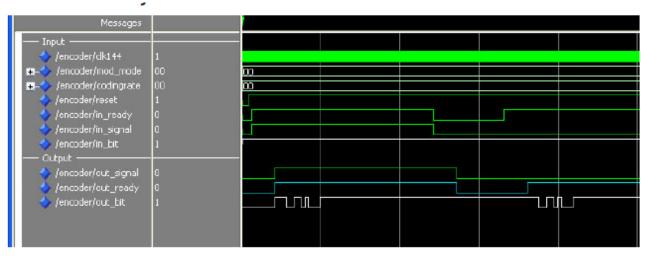

# 3.4.2.8. Post Layout Simulation

#### Figure 20

#### 3.2.2.9 Performance measures

| Logic utilization         | < 1%                  |  |

|---------------------------|-----------------------|--|

| Combinational ALUTs       | 117 / 48,352 ( < 1 %) |  |

| Dedicated logic registers | 40 / 48,352 ( < 1 %)  |  |

| Total registers           | 40                    |  |

| Total block memory bits   | 0 / 2,544,192 ( 0 %)  |  |

| Max freq 229.57 MHz       |                       |  |

#### 3.2.3 Interleaver

#### 3.2.3.1. Function of block

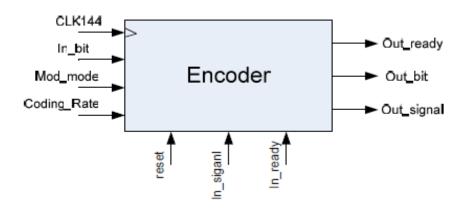

Interleaving aims to distribute transmitted bits in time or frequency or both to achieve desirable bit error distribution after demodulation. What constitutes a desirable error distribution depends on the used FEC code. WLAN systems generally assume a very slowly fading channel, also called quasi-stationary, that does not change during one packet. WLAN systems are wide bandwidth systems, and therefore usually experience frequency selective fading channel. OFDM technology is well suited for communication over slow frequency selective fading channels. Interleaving necessarily introduces delay into the system because bits are not received in the same order as the information source transmits them. The overall communication system usually dictates some maximum delay the system can tolerate, hence restricting the amount of interleaving that can be used.

All encoded data bits shall be interleaved by a block interleaver with a block size corresponding to the number of bits in a single OFDM symbol, NCBPS. The interleaver is defined by a two-step permutation. The first permutation ensures that adjacent coded bits are mapped onto nonadjacent subcarriers. The second ensures that adjacent coded bits are mapped alternately onto less and more significant bits of the constellation and, thereby, long runs of low reliability (LSB) bits are avoided. We shall denote by k the index of the coded bit before the first permutation; i shall be the index after the first and before the second permutation, and j shall be the index after the second permutation, just prior to modulation mapping. The first permutation is defined by the rule

i = (NCBPS/16) (k mod 16) + floor(k/16) k = 0,1,...,NCBPS - 1

The function floor (.) denotes the largest integer not exceeding the parameter. The second permutation is defined by the rule

$j = s \times floor(i/s) + (i + NCBPS - floor(16 \times i/NCBPS)) \mod s$ i = 0,1,... NCBPS - 1

The value of s is determined by the number of coded bits per subcarrier, NBPSC, according to

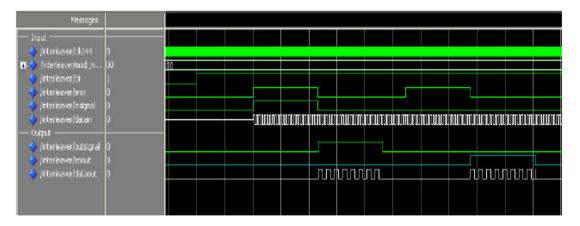

# 3.2.3.3 Interleaver Implementation

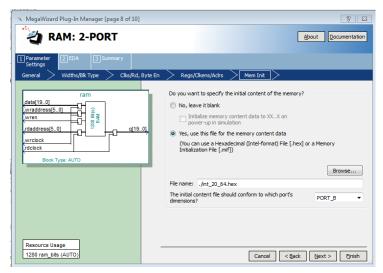

The implementation is based on the equations mentioned above, after simulating these equations on Matlab the interleaving addresses is generated by VHDL conditions ,these addresses is used to save the coming data (original arranged data) into LPM RAMs by the interleaved addresses, then reading this data out and sending them using the linear address of the RAM.

| Data rate<br>(Mbits/s) | Modulation | Coding<br>rate (R) | Coded<br>bits per<br>subcarrier<br>(NBPSC) | Coded bits<br>per<br>OFDM<br>symbol<br>(NCBPS) | Data bit<br>per<br>OFDM<br>symbol<br>(NDBPS) |

|------------------------|------------|--------------------|--------------------------------------------|------------------------------------------------|----------------------------------------------|

| 6                      | BPSK       | 1/2                | 1                                          | 48                                             | 24                                           |

| 9                      | BPSK       | 3⁄4                | 1                                          | 48                                             | 36                                           |

| 12                     | QPSK       | 1/2                | 2                                          | 96                                             | 48                                           |

| 18                     | QPSK       | 3⁄4                | 2                                          | 96                                             | 72                                           |

| 24                     | 16-QAM     | 1/2                | 4                                          | 192                                            | 96                                           |

| 36                     | 16-QAM     | 3⁄4                | 4                                          | 192                                            | 144                                          |

| 48                     | 64-QAM     | 2/3                | 6                                          | 288                                            | 192                                          |

| 54                     | 64-QAM     | 3⁄4                | 6                                          | 288                                            | 216                                          |

#### Figure 21 Rate dependent parameters

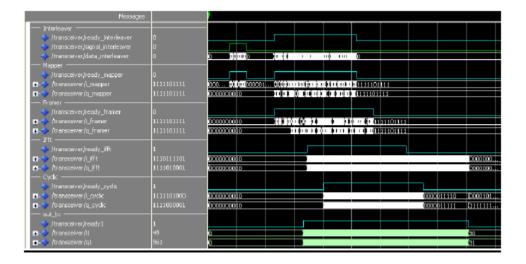

# 3.2.3.4 Post Layout Simulation

#### Figure 22

#### 3.2.3.5 Performance Measurement

| Logic utilization         | < 1%                     |

|---------------------------|--------------------------|

| Combinational ALUTs       | 224 / 48,352 ( < 1 %)    |

| Dedicated logic registers | 52 / 48,352 ( < 1 %)     |

| Total registers           | 52                       |

| Total block memory bits   | 512 / 2,544,192 ( < 1 %) |

| Max freq 201.25 MHz       |                          |

#### 3.2.4 Mapper

#### 3.2.4.1. Function of the block

The OFDM subcarriers shall be modulated by using BPSK, QPSK, 16-QAM, or 64-QAM modulation, depending on the RATE requested. The encoded and interleaved binary serial input data shall be divided into groups of NBPSC (1, 2, 4, or 6) bits and converted into complex numbers representing BPSK, QPSK, 16-QAM, or 64-QAM constellation points. The conversion shall be performed according to Gray-coded constellation mappings, illustrated in Figure 116, with the input bit, b0, being the earliest in the stream. The output values, d, are formed by multiplying the resulting (I+jQ) value by a normalization factor KMOD, as described in this equation.

$d = = (I + jQ) \times KMOD$

The normalization factor, KMOD, depends on the base modulation mode, as prescribed in Table 81. Note that the modulation type can be different from the start to the end of the transmission, as the signal changes from SIGNAL to DATA, as shown in Figure 107. The purpose of the normalization factor is to achieve the same average power for all mappings. In practical implementations, an approximate value of the normalization factor can be used, as long as the device conforms with the modulation accuracy requirements.

| Modulation | K <sub>MOD</sub> |

|------------|------------------|

| BPSK       | 1                |

| QPSK       | 1/√2             |

| 16-QAM     | 1/√10            |

| 64-QAM     | 1/√42            |

Table 3. 2 Modulation-dependent normalization factor KMOD

| QPSK Q  |                | b <sub>0</sub> b <sub>1</sub> | 0000           | 1 01 01          | 11 01   | <sup>+3</sup> 1          |

|---------|----------------|-------------------------------|----------------|------------------|---------|--------------------------|

|         | +†<br>10<br>-1 | Ī                             | 00_00          | o 01_00<br>      | 11.00   | 10,00                    |

| 64-QAM  |                |                               | Q,             |                  | b       | <sub>0</sub> b1b2b3 b4b5 |

| 000 100 | 001 100        | 011 100                       | 010 100 110 10 | 00 111,100       | 101 100 | 100_100                  |

| 000 101 | 001 101        | 011_101                       | 010 101 110 10 | 01 111_101       | 101 101 | 100 101                  |

| 000 111 | 001_111        | 011_111                       | 010 111 110 11 |                  | 101_111 | 100_111                  |

| 000_110 | 001_110        | 011_110                       | 010_110_1      | 10 111_110       | 101_110 | 100_110                  |

| 000 010 | 001 010        | <br>011_010                   | 010 010 110 01 | +3<br>10 111 010 | 101 010 | 100 010 I                |

| 000 011 | 001_011        | 011_011                       | 010 011 110 01 | 11 111.011       | 101 011 | 100 011                  |

| 000 001 | 001 001        | 011_001                       | 010 001 110 00 | 01 111.001       | 101 001 | 100 001                  |

| 000,000 | 001 000        | 011,000                       | 010 000 110 00 | 0 111 000        | 101,000 | 100 000                  |

| 000,000 | 001 000        | 011 000                       | 010 000 110 00 | 0 111,000        | 101 000 | 100 000                  |

16-QAM

00\_10

00\_11

01 10

01 11

11\_10

11\_11

b0b1b2b3

10\_10

10\_11

#### Figure 23 BPSK, QPSK, 16-QAM, and 64-QAM constellation bit encoding

For BPSK, b0 determines the I value, as illustrated in Table 3.3. For QPSK, b0 determines the 1 value and b1 determines the Q value, as illustrated in Table 3.4. For 16-QAM, b0b1 determines the I value and b2b3 determines the Q value, as illustrated in Table 3.5. For 64-QAM, b0b1b2 determines the I value and b3b4b5 determines the Q value, as illustrated in Table 3.6.

BPSK

bn

| $Inputbit(b_0)$ | I-out | Q-out |

|-----------------|-------|-------|

| 0               | -1    | 0     |

| 1               | 1     | 0     |

#### Table 3. 3 BPSK encoding table

| Input bit (b <sub>0</sub> ) | I-out |

|-----------------------------|-------|

| 0                           | -1    |

| 1                           | 1     |

| Input bit $(b_1)$ | Q-out |

|-------------------|-------|

| 0                 | -1    |

| 1                 | 1     |

#### Table 3. 4 QPSK encoding table 5 QPSK encoding table

| Input bits (b <sub>0</sub> b <sub>1</sub> ) | I-out |

|---------------------------------------------|-------|

| 00                                          | -3    |

| 01                                          | -1    |

| 11                                          | 1     |

| 10                                          | 3     |

| Input bits (b <sub>2</sub> b <sub>3</sub> ) | Q-out |

|---------------------------------------------|-------|

| 00                                          | -3    |

| 01                                          | -1    |

| 11                                          | 1     |

| 10                                          | 3     |

Table 3. 5 16-QAM encoding table

| Input bits (b <sub>0</sub> b <sub>1</sub> b <sub>2</sub> ) | I-out | Input bits $(b_3  b_4  b_5)$ | Q-out |

|------------------------------------------------------------|-------|------------------------------|-------|

| 000                                                        | -7    | 000                          | -7    |

| 001                                                        | -5    | 001                          | -5    |

| 011                                                        | -3    | 011                          | -3    |

| 010                                                        | -1    | 010                          | -1    |

| 110                                                        | 1     | 110                          | 1     |

| 111                                                        | 3     | 111                          | 3     |

| 101                                                        | 5     | 101                          | 5     |

| 100                                                        | 7     | 100                          | 7     |

#### Table 3. 6 64-QAM encoding table

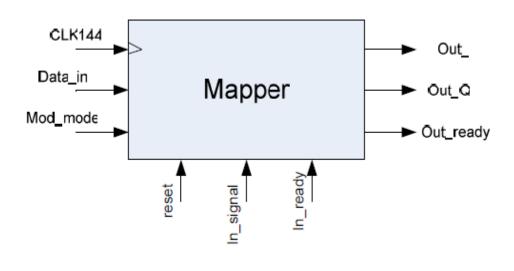

3.2.4.2 Block diagram

# 3.2.4.3 The VHDL Code description

The mapper will work when the data from previous block (interleaver) become ready, i.e. when data\_ready signal become activated (high). - The mapper receives 1 bit at a time from the interleaver, so it should form a group of bits such that each group consists of (1,2,4 or 6) bits according to the modulation mode used and the mapper should convert each group into a complex number, therefore we've made in the code 6 states for the input clock (clk1,clk2,clk3,clk4,clk5,clk6), where at each i/p clock, 1 bit is input to the mapper, and we've made a latch (b) with size equals 6 bits (because the max # of bits/symbol=6 bits) to store the required group of bits, where I and Q will be calculated after the group of bits is formed. - And then I and Q will be computed at an output clock (clk\_out\_mapper), and out\_ready signal become activated. - If we press reset (i.e. reset=0), we will start processing beginning from the 1st state (clk1).

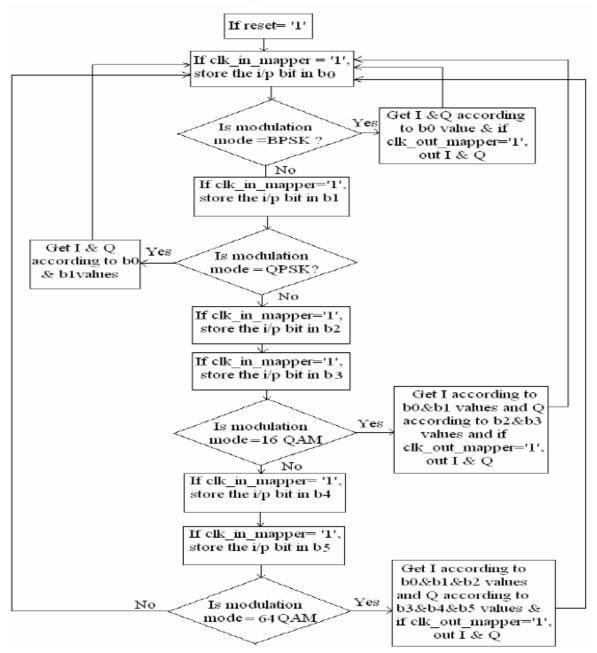

#### At the first input clock (at clk1):

The input bit is stored in b (0). -Then if the modulation\_mode is BPSK, mapper'll check the value of the bit, and according to its value, I and Q are computed and out\_ready become activated (high), then I and Q are outputted if clk\_out='1' and then return again to the 1st state for receiving a new input bit. -But if the modulation\_mode isn't BPSK, we'll enter the 2nd state (clk2).

#### At the 2nd input clock (at clk2):

At clk2, the 2nd input bit is stored in b (1). -And if modulation\_mode is QPSK , mapper'll check the values of both b(0)&b(1) together and according to their values, I and Q are computed and then outputted if clk\_out='1' and then return again to the 1st state for receiving a new bit. But if modulation\_mode isn't QPSK, we'll enter the 3rd state (clk3).

#### At the 3rd input clock (at clk3):

-where at clk3, the 3rd input bit is stored in b (2) then we'll enter the 4th state(clk4).

At the 4th input clock (at clk4): -At clk4 the 4th input bit is stored in b (3). -And if modulation\_mode is 16 QAM , b(0)&b(1) together will determine I value while b(2)&b(3) together will determine Q value as shown in the constellation mapping , and if clk\_out ='1' , I and Q will be outputted. And then return again to 1st state.

-But if modulation\_mode isn't 16 QAM, we'll enter 5th state (clk5).

# At the 5th input clock (at clk5):

-In this state the 5th input bit is stored in b (4) then we'll enter 6th state (clk6).

#### At the 6th input clock (at clk6):

- At clk6 the 6th input bit is stored in b (5). - And if modulation\_ mode is 64 QAM, b(0)&b(1)&b(2) together will determine I value while b(3)&b(4)&b(5) together will determine Q value as seen from the signal constellation, then we'll enter 1st state(clk1), and if clk\_out ='1', I and Q will be outputted, and the above steps will be similarly repeated again for the remaining incoming data bits.

# 3.2.4.4. The Calculated I and Q values in the mapper

9 bits will be needed to represent each of I and Q, where 2 bits for the integer # before the point and 7 bits for the fractions. So, we've calculate I and Q values in 9 bits according to the modulation mode used, where there is a modulation factor (Kmod ) that is taken into consideration.

| 1)- Bpsk:         | 2)- Qpsk:                      |

|-------------------|--------------------------------|

| +1=01000000=80H   | +1/√2= +0.7071=001011010=5AH   |

| -1=110000000=180H | -1/v2= -0.7071=110100110 =1A6H |

#### 3)- 16Qam:

+1/v10= +0.3162=000101000=28H

- -1/V10= -0.3162=111011000 =1D8H

- +3/v10=+0.9487=001111001=79H

- -3/v10= -0.9487= 110000111=187H

4)- 64Qam:

+1/v42=+0.1543=000010011=13H

-1/V42=-0.1543=111101101 =1EDH

+3/v42=+0.4629=000111011=3BH

-3/v42=-0.4629=111000101=1C5H

+5/v42=+0.7715=001100010=62H

-5/v42=-0.7715=110011110=19EH

+7/v42=+1.0801=010001010=8AH

-7/V42=-1.0801=101110110=176H

#### 3.2.4.5. Flow chart for the mapper

Figure 25

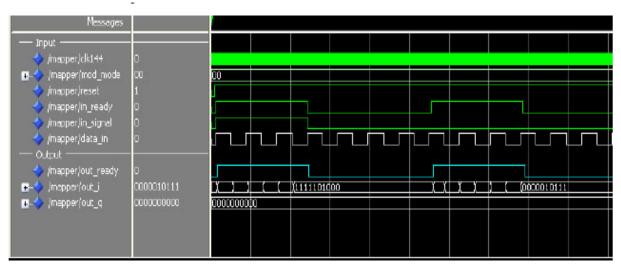

# 3.2.4.6 Post Layout Simulation

#### Figure 26

#### 3.2.4.7 Performance Measurement

| Logic utilization         | < 1%                 |

|---------------------------|----------------------|

| Combinational ALUTs       | 32 / 48,352 ( < 1 %) |

| Dedicated logic registers | 14 / 48,352 ( < 1 %) |

| Total registers           | 14                   |

| Total block memory bits   | 0 / 2,544,192 ( 0 %) |

| Max freq 483.56Mhz        |                      |

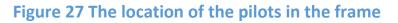

#### 3.2.5. Framer

#### 3.2.5.1. Function of the Block

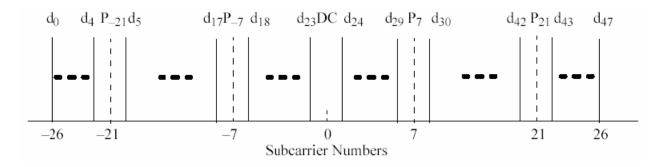

In each OFDM symbol, four of the subcarriers are dedicated to pilot signals. These pilots are used for tracking the frequency and phase errors in the OFDM received signal. They also help in estimating and correcting the channel effect. These pilot signals shall be put in subcarriers -21, -7, 7 and 21. The pilots shall be BPSK modulated by a pseudo binary sequence to prevent the generation of spectral lines.

3.2.5.2. Block Diagram

#### 3.2.5.3 VHDL Description

I\_in and Q\_in are the complex outputs (real and imaginary) from the mapper . The in\_ready signal is also from the mapper to indicate the start of the transmission. The out\_ready signal indicates that a valid output is ready in I\_out and Q\_out signals. This block receives 48 input (I & Q ) from the mapper we insert zeros and pilots , Hence the output will be 64 sample including this zeros and pilots. Pilots are calculated from the out put of the PN-Generator described above, which produce an output each 64 clock cycle. In the implementation of this block, we used double buffering in order to pipeline the operation. The output pattern is formed as the standard required for the IFFT input as shown in Figure (29).

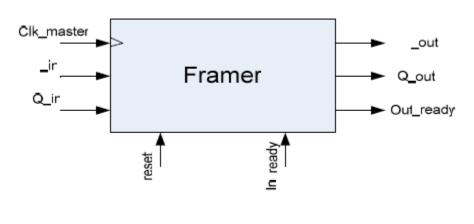

# Figure 29 Inputs and outputs of the IFFT block in the 802.11a WLAN standard

This block has 1 symbol delay as it stores a complete symbol, output the symbols in the right order, insert pilots and zeros in their positions.

Theoretical notes: The negative part of the input OFDM symbol is transformed to the end of the symbol in the framer because the IFFT block has a range from 0 to 64, and this has nothing to do with the signal as the frequency domain of the DFT is periodic, therefore, this is theoretically right. The Zeros insertion in the middle of the output frame is actually in the high frequency part of the symbol (in the symbol, the max. freq. is at sample 64/2 [ from the DFT properties] ).

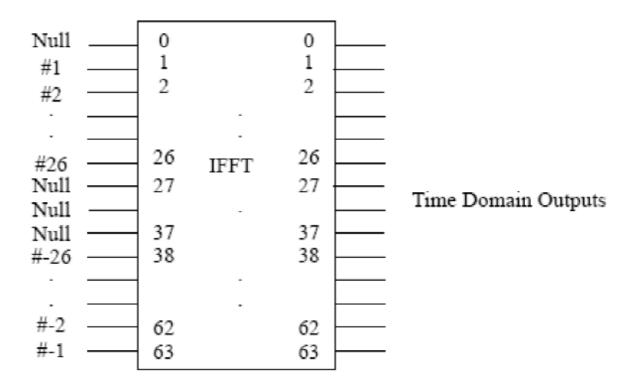

#### 3.2.5.4. Post Layout Simulation

#### Figure 30

#### 3.2.5.5. Performance measurement

| Logic utilization         | < 1%                      |

|---------------------------|---------------------------|

| Combinational ALUTs       | 77 / 48,352 ( < 1 %)      |

| Dedicated logic registers | 50 / 48,352 ( < 1 %)      |

| Total registers           | 50                        |

| Total block memory bits   | 2560 / 2,544,192 ( < 1 %) |

| Max freq                  | 166.67Mhz                 |

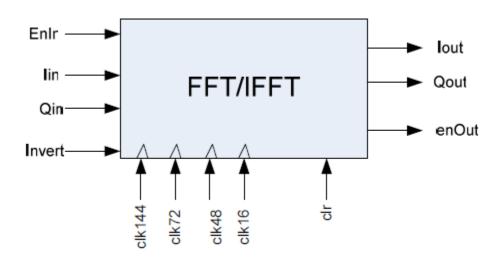

#### 3.2.6 FFT/IFFT

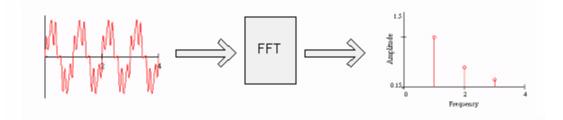

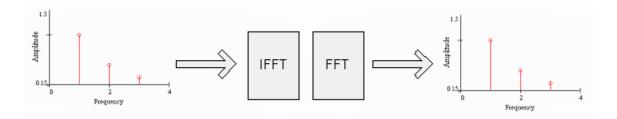

The fast Fourier Transform and inverse fast Fourier Transform operations must be carried out in the transmitter and the receiver of the Wi-Fi system as they carry out the conversion of OFDM symbol from Frequency domain to time domain in transmitter and vice versa in receiver.

Figure 31 conversion from frequency domain to time domain in transmitter

Figure 32 conversion from time domain to frequency domain in receiver

Figure 33 output of the two operations back to back

#### **IFFT/FFT** illustration

#### 3.2.6.1 CFFT core

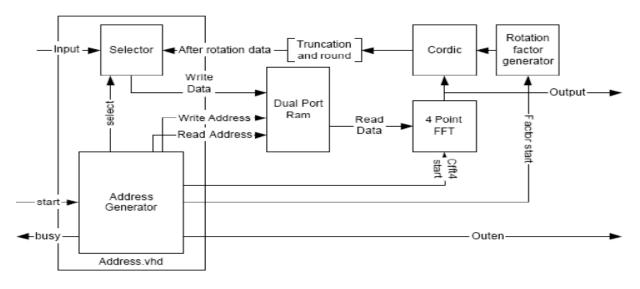

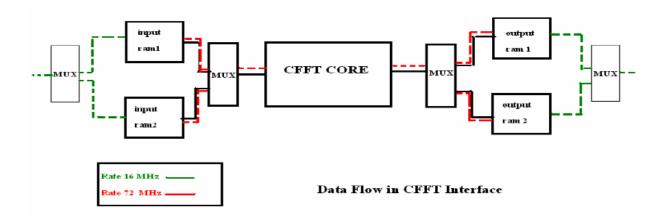

In our Wi-Fi Transceiver we used the CFFT core done by ZHAO Ming and available in the website opencores.org and we connected our interface to this component to control it and make it compatible with our design's handshaking system and compatible with the input and output data rates to it.

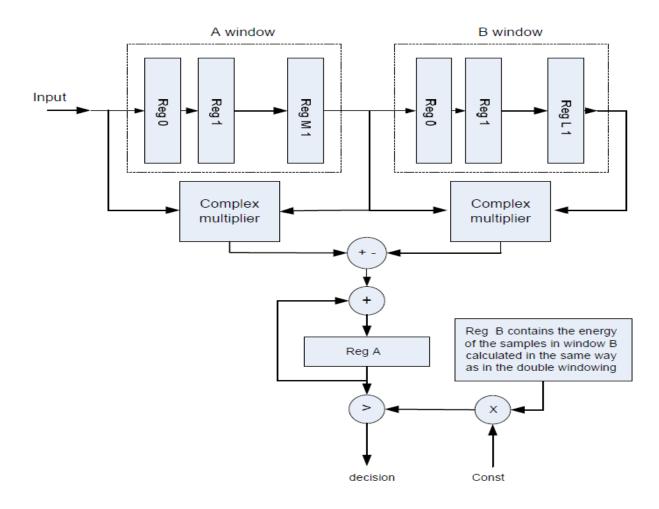

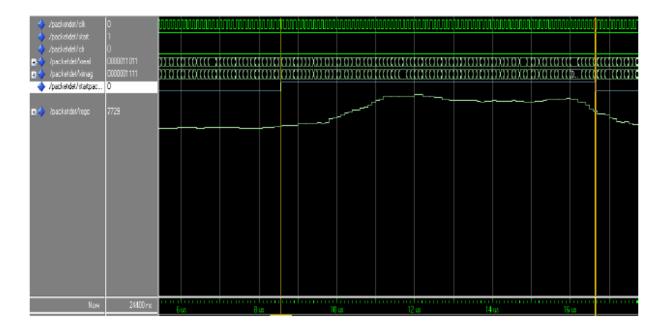

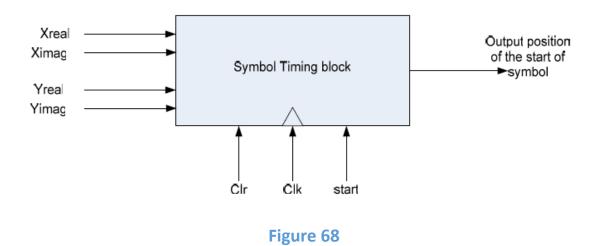

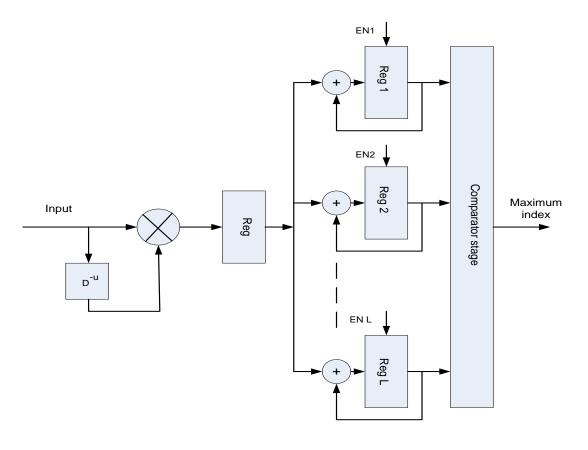

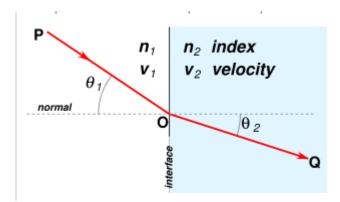

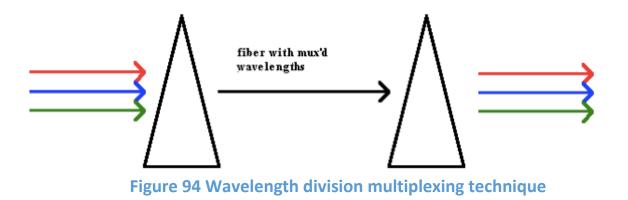

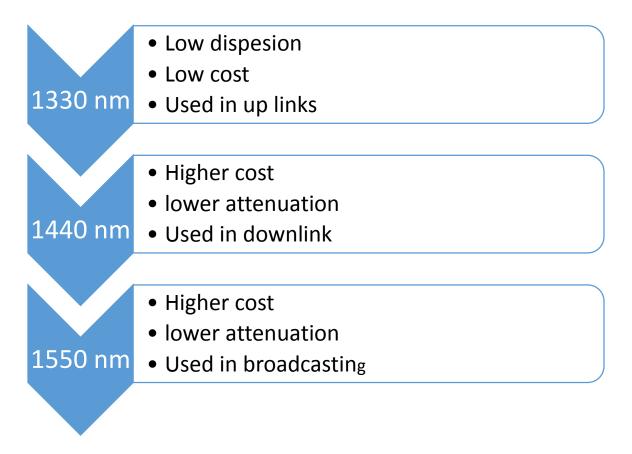

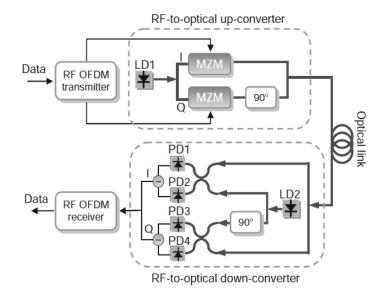

#### 3.2.6.2 Description