# AUTOMATED CURRENT MIRROR LAYOUT TOOL (ACML)

## **Prepared by:**

Abanoub Atef Farid

Marina Hamdy Zaky

Mario Adel Messiha

Nada Khaled Ahmed

Omar Mohamed Ezzat

Omar Tarek Abdel-Wahab

Under the Supervision of Associate Prof. Hassan Mostafa

A Graduation Project Report Submitted to

The Faculty of Engineering at Cairo University in

Partial Fulfillment of the Requirements for the

Degree of Bachelor of Science in

Electronics and Communications Engineering Faculty of Engineering, Cairo

University Giza, Egypt

July 2019

# Abstract

Analog circuit design automation is likely to play a key role in the design process of the next generation of mixed-signal integrated circuits (ICs) and application specified integrated circuits (ASICs).

In the digital domain, computer-aided design (CAD) tools are fairly well developed and commercially available to the design community. Unfortunately, the story is quite different on the analog side.

In this thesis, we summarize the work done over a period of nearly 7 months in collaboration with a promising IC solution corporation, Si-Vision, to produce analog physical design tool for the design of analog integrated circuits (ICs) is presented. This tool offers great flexibility that allows analog circuit designers to bring their special design knowledge and experiences into the physical design process to create high-quality analog circuit layouts. Different from conventional layout systems that are limited to the optimization of single devices, our layout generation tool attempts to optimize more complex modules, at this level the tool is working with current mirrors and differential pairs, which are two of the main building blocks of any analog circuit. This tool covers the following three major analog physical designs stages. 1) Pattern Generation: Saves physical designer's time and headache by auto-generating the CM or DP optimum matching pattern according to given inputs. 2) Placement: This placement algorithm features a novel genetic placement stage followed by a fast communication scheme with the router. 3) Routing: The router imitates the man made CM and DP approaches, Specification-based constructive routing finally completes the interconnection of the entire layout. Several testing circuits have been applied to demonstrate the design efficiency and the effectiveness of this tool. Experimental results show that this new layout tool is capable of producing high quality layouts comparable to those manually done by layout experts but with much less design time.

## Acknowledgements

We are using this opportunity to express our gratitude to everyone who supported us throughout the graduation project. We are thankful for their aspiring guidance and friendly advice.

First, we want to thank our major advisor Dr. Hassan Mustafa for his encouragement and patience, his care about following up each stage in the project and his suggestions to solve some problems we faced during the project work, so we would like to thank him very much for his support and understanding over this year.

We would like to express our gratitude for the team of brilliant engineers at Si-Vision IC Solution Corporation for their help, support and for the valuable training sessions we received throughout the project including but limited to Eng. Shrouk Shafie, Eng. Mostafa Nashaat, Eng. Islam Nashaat, Eng. Moustafa Hussien, Eng Mohammed Shehata.

Moreover, we would like to thank, in particular, Eng. Fady Atef who provided us an opportunity to join their team as intern. We are extremely thankful and indebted to him for sharing expertise, and sincere and valuable guidance and encouragement extended to us. Without his precious support it would not have been possible to complete this tool.

Last but not least, we want to thank our families for their support, tolerance and love during this year especially during the hard times they were always there having faith in what we do. We are grateful to our families, colleagues and friends for always motivating us, without them we wouldn't have come so far.

# **Table of Contents**

| Abstra  | act                                                            | ii  |

|---------|----------------------------------------------------------------|-----|

| Ackno   | owledgements                                                   | iii |

| Table   | of Contents                                                    | iv  |

| List of | f Tables                                                       | vi  |

| List of | f Figures                                                      | vii |

| List o  | f Acronyms                                                     | x   |

| Chap    | ter 1. Introduction                                            | 1   |

| 1.1.    | Motivation                                                     | 1   |

| 1.2.    | Analog Layout Generation and Verification processes            | 2   |

| 1.3.    | Problem statement                                              |     |

| 1.4.    | Solution approach                                              | 12  |

| 1.5.    | Organization                                                   | 13  |

| Chap    | ter 2. Background and Related work                             | 14  |

| 2.1.    | Introduction                                                   | 14  |

| 2.2.    | Prior work                                                     |     |

| 1.      | AIDA tool {Analog Integrated Circuit Design Automation}        | 18  |

| 2.      | ALADIN: A Layout Synthesis Tool for Analog Integrated Circuits | 21  |

| 3.      | LAYLA the Analog Layout Tool                                   | 23  |

| Chap    | ter 3. Tool Overview                                           | 29  |

| 3.1.    | Intro and features                                             | 29  |

| 3.2.    | USER GUIDE                                                     | 33  |

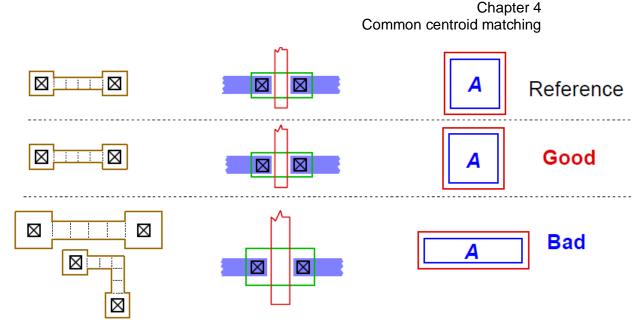

| Chap    | ter 4. Common centroid matching                                |     |

| 4.1.    | Matching in Analog layout                                      |     |

| 1.      | Sources of matching errors                                     |     |

| 2.      | Rules of optimum matching                                      | 44  |

| 3.      | Geometric effects                                              | 48  |

| 4.      | Diffusion effects                                              | 50  |

| 5.      | Thermal effects                                                | 50  |

| 6.      | Stress effects                                                 | 51  |

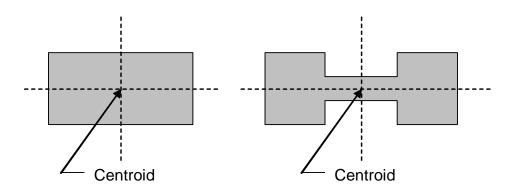

| 4.2.    | Common centroid matching                                       | 52  |

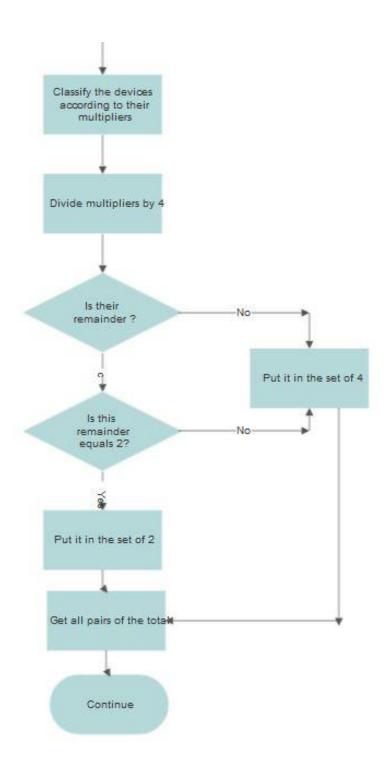

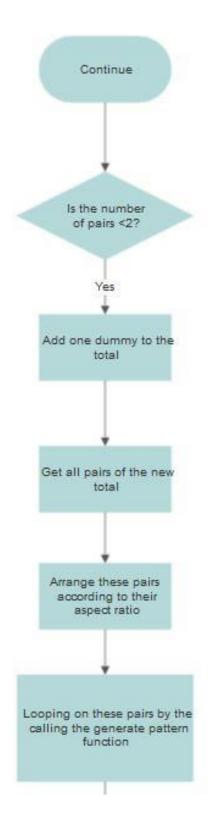

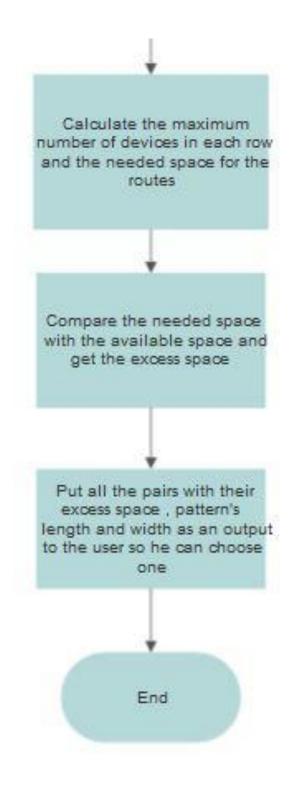

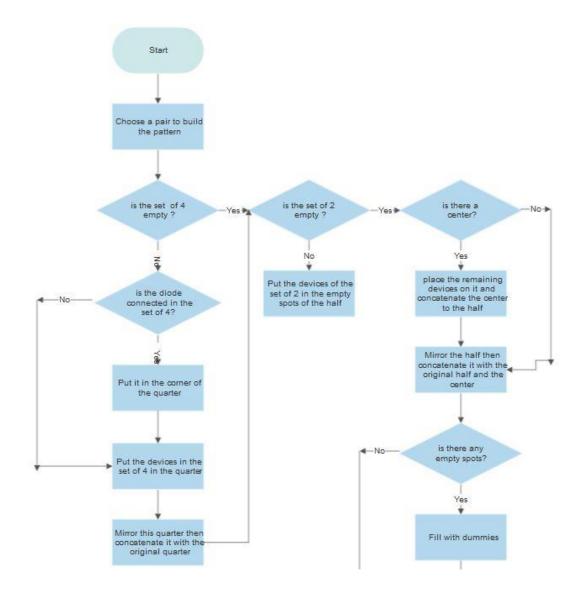

| 4.3.    | First version of the algorithm                                 | 62  |

| 4.4.    | Current Algorithm                                              | 67  |

| Chap    | ter 5. Automatic Routing of Current Mirrors                    |     |

| 5.1.    | Opening thoughts on routing of analog devices.                 |     |

| 5.2.    | ACML router flow                                               |     |

| 5.3.    | Placing the gates contacts                                     |     |

| 5.4.    | The implant extension                                          |     |

| 5.5.  | Sources and drains metal extension and putting vias | 89  |

|-------|-----------------------------------------------------|-----|

| .5.6  | Bulk connections                                    | 91  |

| 5.7.  | Gates global routing                                | 92  |

| 5.8.  | Drains local routing                                | 93  |

| 5.9.  | Drains global routing                               | 94  |

| .5.10 | Placing Metal VIAS                                  |     |

| 5.11. | Verification                                        | 100 |

| Chapt | ter 6. Results                                      | 102 |

| _     | Tool overview                                       |     |

| 6.2.  | Tool's detailed output                              | 103 |

| 1.    | Test case #1                                        | 103 |

| 2.    | Test case #2                                        | 106 |

| Chapt | ter 7. Conclusion and future work                   | 110 |

| .7.1  | Conclusion                                          | 110 |

| .7.2  | Future work                                         | 112 |

| Refer | ences                                               | 117 |

# List of Tables

| Table 1: Analog layout aware sizing tools                          | Error! Bookmark not defined.     |

|--------------------------------------------------------------------|----------------------------------|

| Table 2: BAD for routability matching pattern example              |                                  |

| Table 3: good for routability matching pattern example             |                                  |

| Table 4: Matching pattern example 3                                |                                  |

| Table 5: Matching pattern example 4                                |                                  |

| Table 6: Quarter cell of first version of the tool's algorithm     |                                  |

| Table 7: Half-cell of the first version of tool's algorithm        |                                  |

| Table 8: total array for first version of tool's algorithm         |                                  |

| Table 9: Current version of tool's algorithm final matching patter | rn for source shared devices67   |

| Table 10: Current version of tool's algorithm final matching patt  | tern for source shared devices67 |

# List of Figures

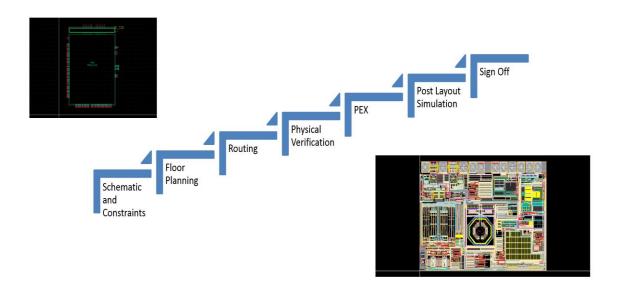

| Figure 1: Layout design procedure                                                                                                    | 3       |

|--------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 2: Steps of floor planning                                                                                                    | 4       |

| Figure 3: Design implementation steps                                                                                                | 6       |

| Figure 4: Layout verification steps                                                                                                  | 6       |

| Figure 5: Capacitance is everywhere. Everything is talking to everything else                                                        | 8       |

| Figure 6: An example for well-matched differential pair                                                                              | 10      |

| Figure 7: Casually placed layout, poor matching                                                                                      | 10      |

| Figure 8: Imaginary line of symmetry helps components match.                                                                         | 11      |

| Figure 9: Real devices encased within a ring of dummy devices                                                                        | 12      |

| Figure 10: Layout automation solution approaches                                                                                     | 14      |

| Figure 11: AIDA tool                                                                                                                 | 19      |

| Figure 12: AIDA's Graphical User Interface navigating the sizing solution set and showing corresponding floorplan and global routing |         |

| Figure 13: Block diagram in ALADIN                                                                                                   | 22      |

| Figure 14: Circuit/layout synthesis using ALADIN                                                                                     | 23      |

| Figure 15: Software Architecture of LAYLA                                                                                            | 24      |

| Figure 16: Chronological representation of analog layout generators                                                                  | 27      |

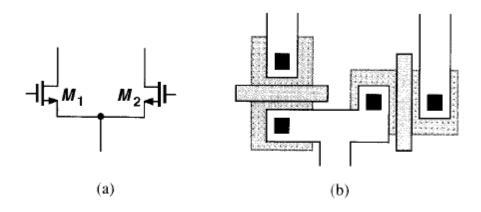

| Figure 17: CM schematic                                                                                                              | 33      |

| Figure 18: Tool's GUI interaction with user                                                                                          | 33      |

| Figure 19: Tool's GUI response for user selection                                                                                    | 34      |

| Figure 20: Inputs for GUI                                                                                                            | 34      |

| Figure 21: GUI first output to user                                                                                                  | 36      |

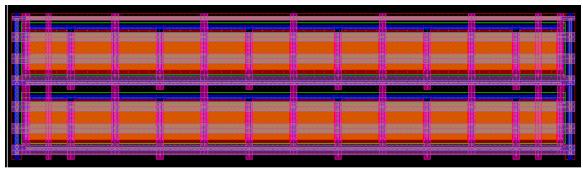

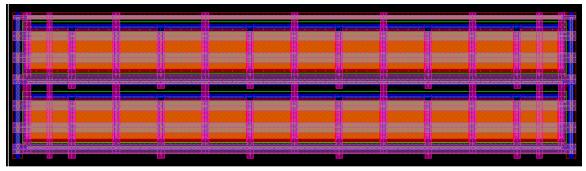

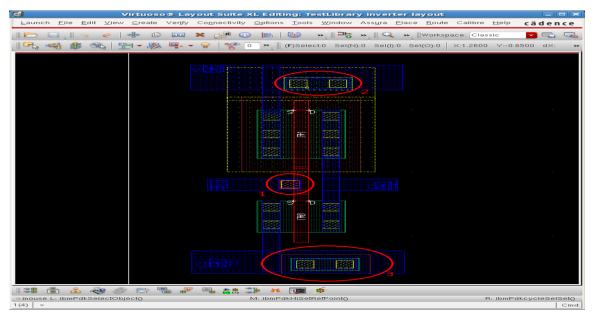

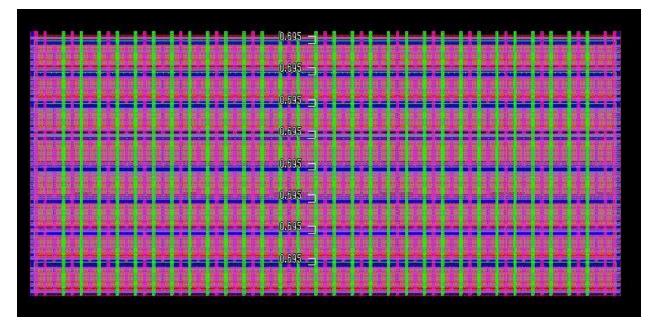

| Figure 22: Final tool's output, fully routed CM                                                                                      | 37      |

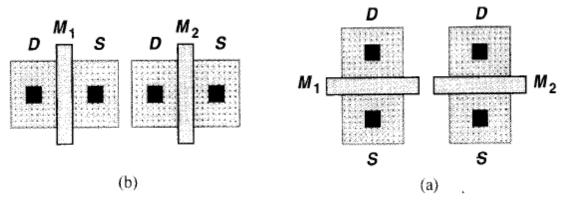

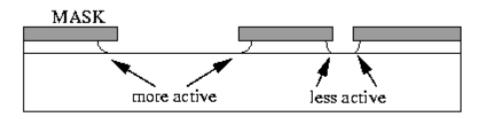

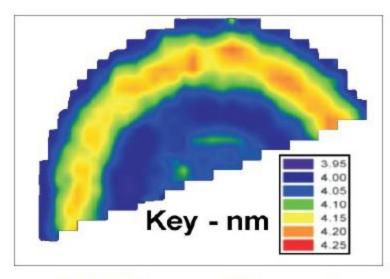

| Figure 23: Gradient Mismatch                                                                                                         | 40      |

| Figure 24: Process variations                                                                                                        | 41      |

| Figure 25: Matching                                                                                                                  | 42      |

| Figure 26: Temperature gradient                                                                                                      | 44      |

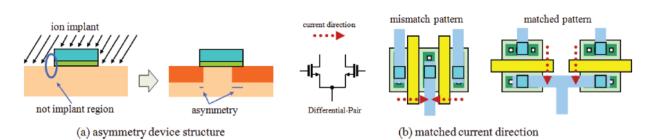

| Figure 27: Asymmetry device structures and matching current directions                                                               | 45      |

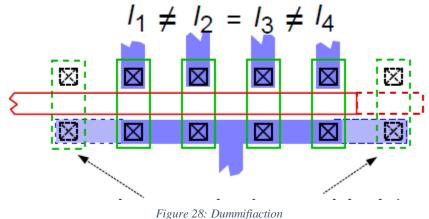

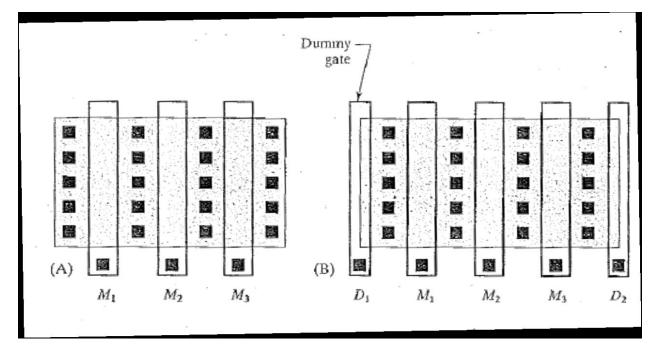

| Figure 28: Dummifiaction                                                                                                             | 46      |

| Figure 29: Transistor size vs Mismatch                                                                                               | 48      |

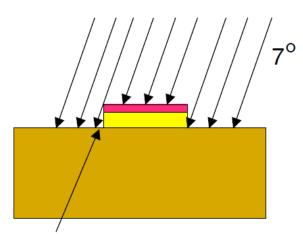

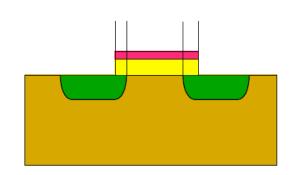

| Figure 30: Etching process                                                                                                           | 49      |

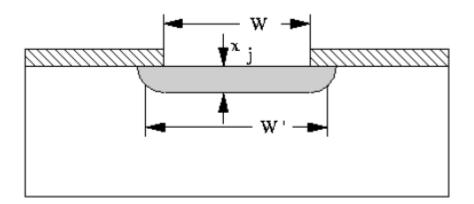

| Figure 31: Diffusion effect                                                                                                          | 50      |

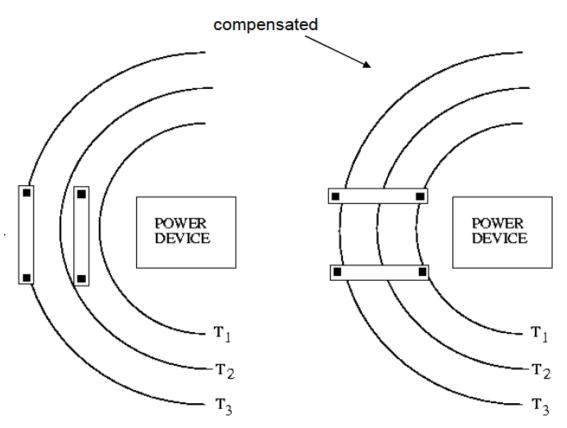

| Figure 32: overcoming temperature gradient                                                                                           | 51      |

| Figure 33: Common Centroid matching pattern for 2 devices Error! Bookmark not de                                                     | efined. |

| Figure 34: Common Centroid matching pattern for 3 devices Error! Bookmark not de                                                     | efined. |

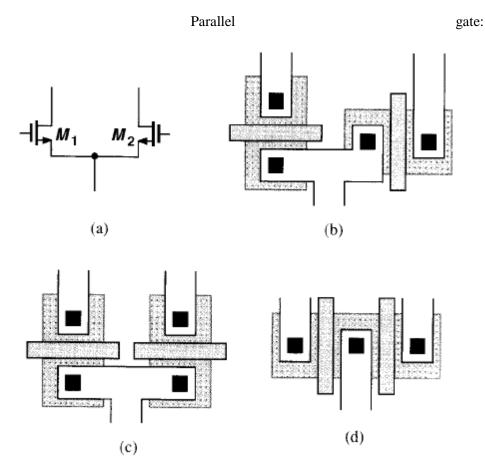

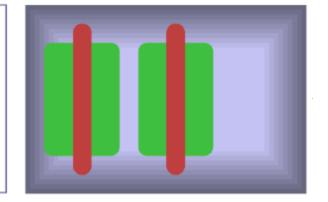

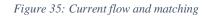

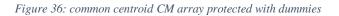

| Figure 35: Cross-Quad matching                                                                                                       | 56      |

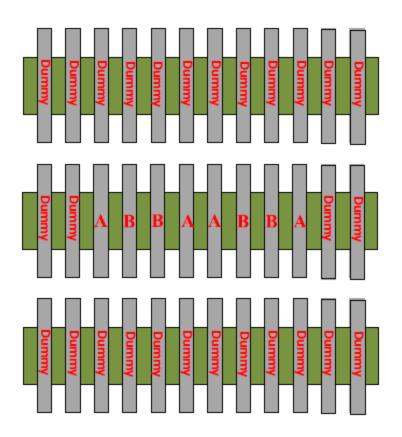

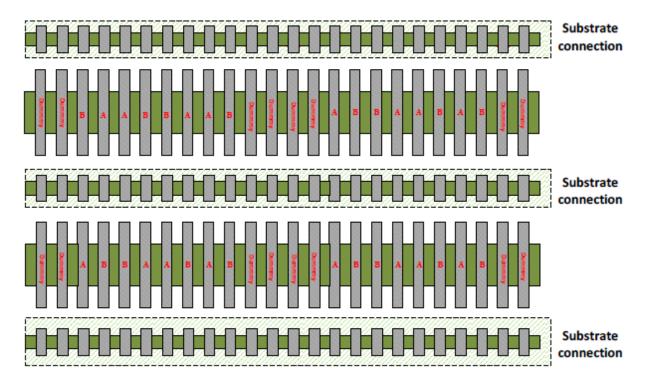

| Figure 36: 2-D cross-coupled arrays                                                            | 57    |

|------------------------------------------------------------------------------------------------|-------|

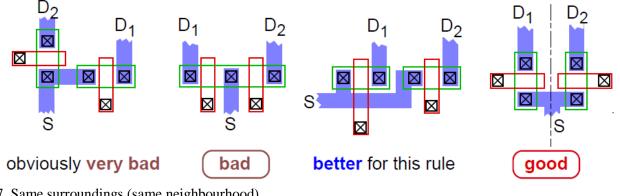

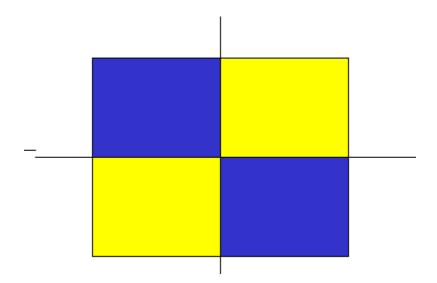

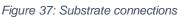

| Figure 37: Current flow and matching                                                           | 59    |

| Figure 38: common centroid CM array protected with dummies                                     | 60    |

| Figure 39: Substrate connections                                                               | 61    |

| Figure 40: Sometimes you are given fixed wiring layout                                         | 84    |

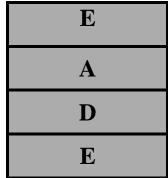

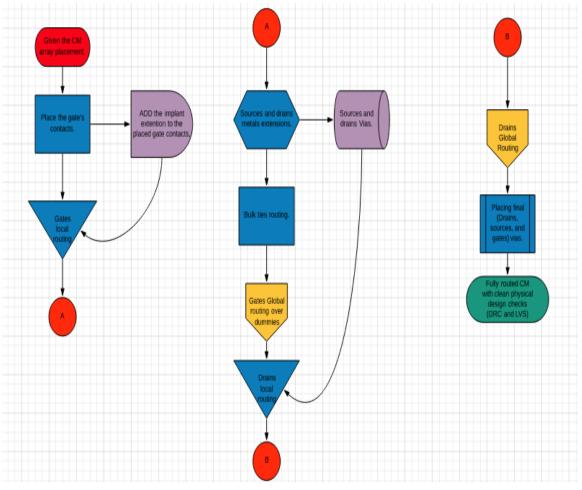

| Figure 41: ACML router flowchart                                                               | 86    |

| Figure 42: The default gate connections implemented in the p-cell, with undesired U-s routing. | 1 1 2 |

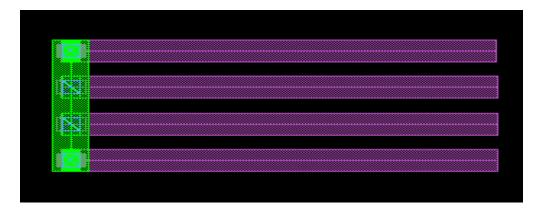

| Figure 43: Transistors with gate contacts option disabled                                      | 87    |

| Figure 44: Gates connections with metal 1 instead of poly                                      |       |

| Figure 45: NMOS transistors with the NIMP extension                                            |       |

| Figure 46: PMOS transistors with PIMP extension                                                |       |

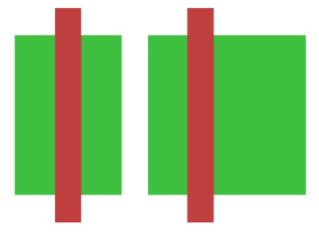

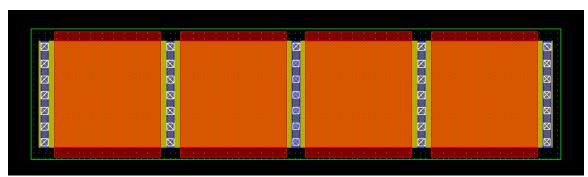

| Figure 47: CM array sources and drains extensions                                              | 91    |

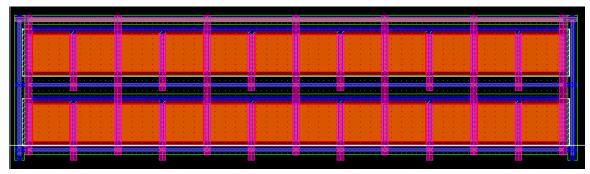

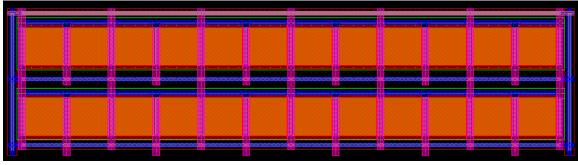

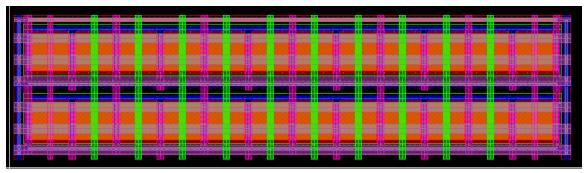

| Figure 48: NMOS array with its bulk connected to VSS                                           | 92    |

| Figure 49: PMOS array with its bulk connected to VDD                                           | 92    |

| Figure 50: gates global routing                                                                | 93    |

| Figure 51: Drains local routing                                                                | 94    |

| Figure 52: star connection using metal 3 and metal 4                                           | 95    |

| Figure 53: Before drains global routing                                                        | 96    |

| Figure 54: Drains global routes                                                                | 96    |

| Figure 55 : VIAS in Layout view                                                                | 98    |

| Figure 56 : VIAS between different metal layers                                                |       |

| Figure 57: Vias 100                                                                            |       |

| Figure 58: Fully routed CM                                                                     | 100   |

| Figure 59: Physical verification results                                                       | 101   |

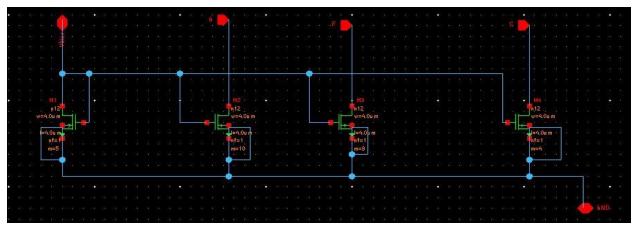

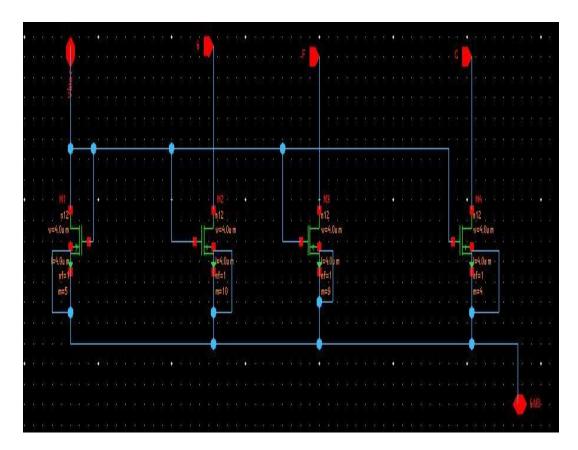

| Figure 60 : Given schematic of current mirror                                                  |       |

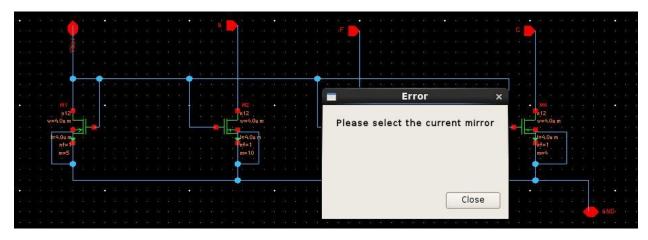

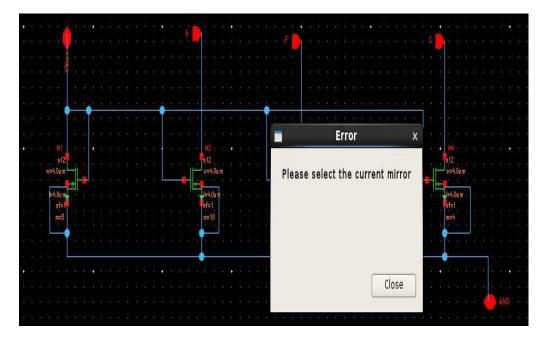

| Figure 61 : window appeared asking to select the transistors of the mirror                     | 104   |

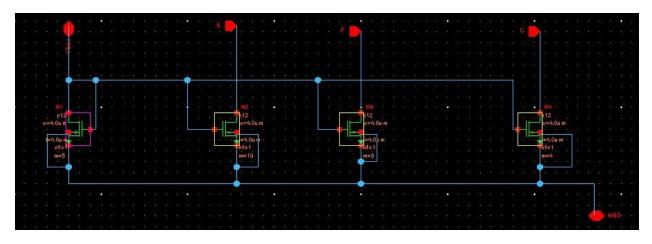

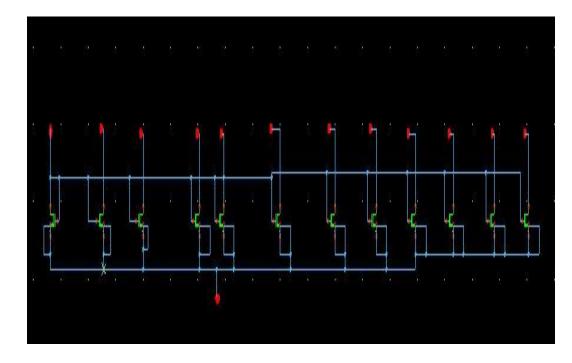

| Figure 62 : window after selecting the transistors of the mirror                               | 104   |

| Figure 63 : window shows all the available pairs for the user to select one from them          | 105   |

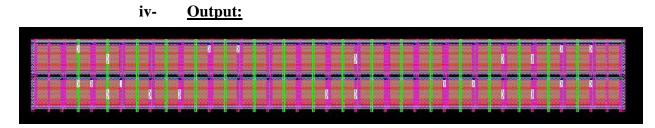

| Figure 64 : Generated layout if the user chose pair 1                                          | 105   |

| Figure 65 : matching pattern for this case                                                     | 106   |

| Figure 66 : the given schematic for case 2                                                     | 106   |

| Figure 67 : parameters of devices for case 2                                                   | 107   |

| Figure 68 : available pairs with their area for case 2                                         | 107   |

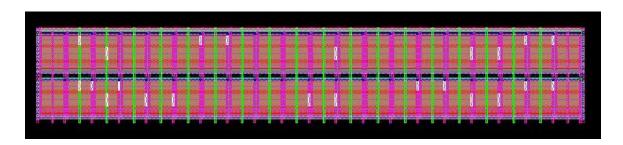

| Figure 69 : generated layout for case 2                                                        | 108   |

| Figure 70 : selected pattern for case 2                                                        | 108   |

| Figure 71: Layout: from specs to sign off                                                      | 110   |

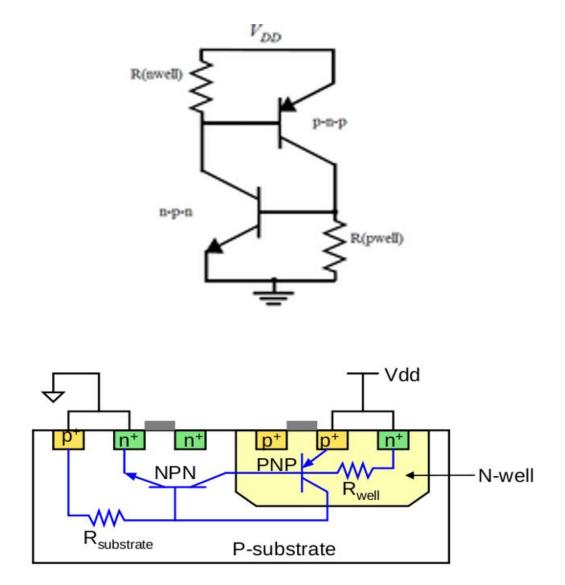

| Figure 72: Latchup                                                                             | 111   |

Chapter 1 Introduction

# List of Acronyms

| ADC  | Analog to Digital Converter             |

|------|-----------------------------------------|

| AMS  | Analog Mixed Signals                    |

| ASIC | Application-Specific Integrated Circuit |

| CAD  | Computer-Aided Design                   |

| СМ   | Current Mirrors                         |

| DP   | Differential Pair                       |

| DRC  | Design Rules Check                      |

| DM   | Design Manual                           |

| d    | Dummy                                   |

| ERC  | Electrical rules check                  |

| NMOS | n-Channel MOSFET                        |

| NIMP | N-Implant                               |

| NW   | N-Well                                  |

| PMOS | p-Channel MOSFET                        |

| PIMP | P-Implant                               |

| PW  | P-Well               |

|-----|----------------------|

| LVS | Layout vs. Schematic |

| LUP | Latch Up             |

| M#  | Metal #              |

Chapter 1 Introduction

Chapter 1 Introduction

# Chapter 1. Introduction

In this thesis, we are going to propose a technique to fully automate the layout of any current mirror with any specification (Width, Length, number of fingers and multipliers ......)

# 1.1. Motivation

During the past two decades, the electronics industry has grown very fast both in Size and in complexity. Designers began talking about chip design only 25 years Ago. At the beginning, the idea was to design chips to reduce the computer size.

Instead of room-sized computers, we have now ended up with PCs running at a Speed that back then was considered "impossible to imagine." The application of IC technology has exploded into many parts of our lives.

IC layout design was originally hand-drafted on special paper called Mylar.

This was a long and laborious task. The market demands and advances in technology brought about an immediate need to develop software and hardware

Solutions to improve the time-to-market of the chip designs and especially to automate the entire process. Accuracy of the final masks was also a driving force in the computerization of layout design.

The first platforms were custom built to ensure that graphics applications ran quickly and had sufficient capabilities. Companies such as CALMA (Data General) built mainframe-sized machines and developed specialized software for printed circuit board (PCB) and integrated circuit (IC) applications.

The disk size was huge by today's standards. The top-of-the-line computer had 220MB of disk space and only 0.5MB of DRAM was available at the time.

The price tag was around \$1 million U.S., and not everybody could afford to be involved in this kind of design. As the market and the chip sizes grew and more companies were involved in chip design, the hardware and software developers came up with faster, smaller, and cheaper solutions.

The biggest revolution in hardware was the development of the "engineering workstation," which ran a version of the UNIX platform. Workstations have developed over the years to incredible speed and complexity. They are used for all kinds of engineering design, so the prices are very affordable. HP, Sun, and IBM are only a handful of survivors in this field, Daisy being one that has disappeared from the market. Today there is tremendous pressure to go to even cheaper and more popular platforms, such as PCs with Linux and Windows NT platforms.

As the hardware platforms evolved, software development progressed at an even faster rate. Companies such as Mentor Graphics, Cadence, Compass, and Daisy gained larger and larger shares of the IC and PCB design tools market. For the PC platform, a company such as Tanner, with a product called L-Edit, is an example of how the software development market has grown for IC design. The direction for development of the software has really been toward more and more automation of the tasks that are labor intensive: for example, designs with hundreds of transistor blocks, where interconnection analysis is impossible to do by human eyes, or verification of a 256-MB memory chip.

#### Significant examples of automation include the following:

*Layout synthesis:* Layout can be created from "code" instead of the traditional methods of manually drawing the polygons.

*Layout migration*: Alternatively, layout can be "migrated" from one set of design rules to another using mapping and sophisticated compaction techniques.

*Layout verification:* These tools perform an increasing number of checks on the final layout before it goes to production. For example, minimum size rules are checked to ensure that the design is manufactural.

*Circuit synthesis:* Similar to layout synthesis, in this case schematics can be automatically generated from specialized "code" (i.e., VHDL or Verilog).

This has had a huge impact on layout design, as the sheer volume of circuitry produced by these circuit synthesis tools created a need for more layout automation such as place-and-route tools.

*Place-and-route:* Instance placement for literally millions of cells as well as optimizing the placement for minimum connectivity and maximum circuit performance.

Today, layout design is carried out in an environment that is ever changing.

The software tools and approaches, computing platforms, the companies providing these tools, the customers we serve, the applications that are being implemented, and the market pressures we face are all changing year by year.

These changes make this industry an interesting one in which to be involved. However, let's not forget that the fundamental concepts behind producing quality layout are based on physical and electrical properties that never change.

# **1.2.** Analog Layout Generation and Verification processes

The following figure shows a general layout design flow that is applicable for all design types. This procedure is straightforward and self-explanatory and could be applied to almost any engineering task. Of course we will concentrate on how it applies to layout design.

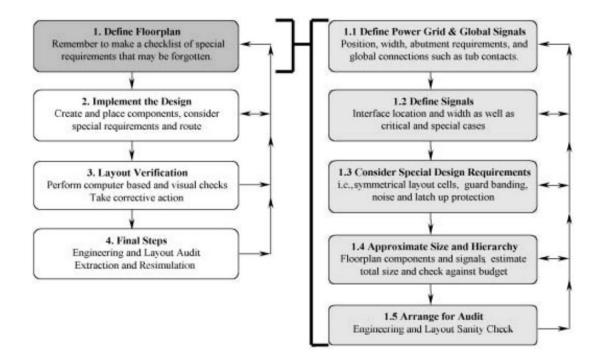

#### Figure 1: Layout design procedure

Step 1 is crucial for getting started on the right track. It is in this step that we collect and review our knowledge of layout design and apply it to the specific circuit design under consideration. The aim is to produce a strategy for attacking the design by documenting the general areas where all components and signals will go.

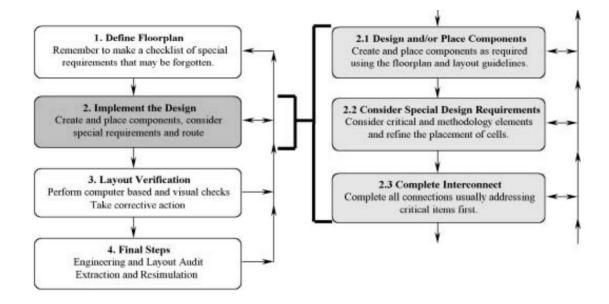

Step 2 is simply implementing the design: executing and possibly revising the floorplan based on the realities of implementation. One way to think of the design process is to "plan top down," then "implement bottom up." By this we mean that we first floorplan general areas and approaches with a top-level view. With this plan in place we implement the design by starting with the lowest level components first and fill the areas defined in the plan. The lower level design tasks are easier because the constraints imposed on them were defined in the top-level floorplan. As the general areas are completed, we adjust our plan for future work. With a sound floorplan, adjustments are minor and the completion of the design is easy.

Computer-based checks (DRC and LVS) form the bulk of step 3. These checks should be done in a certain order.

On top of the computer-based checks a visual inspection is recommended, as the automatic computer checks are only as good as the rules that are coded into them. Make a plot of your

design and look at it. Also, there are many aspects of most designs that cannot be checked by computer. An example of this is the degree of symmetry of a balanced layout. These visual checks should be part of the audit checklist as a reminder.

Step 4 is a final sanity and cross-check to confirm that all requirements have been met and none missed, along with a final extraction step.

Figure 2: Steps of floor planning

The first step, 1.1, is related to the planning of the layout of the power supplies and/or global signals. The power supply connectivity is typically called the power grid. Power supply resistance from the interface to all parts of the design must be considered. In this case special attention must be applied to the width of the supply lines and the grid or mesh of power lines through the design. Again the interface to other designs is important, especially in the case of a cell design where it may be desired to array it or have seamless abutment requirements to other cells. Let's not forget that tub and substrate contacts are typically connected from the power supplies, so a strategy to lay out these contacts must also be considered. Step 1.2 is to list all of the input and output signals. Each signal is assigned a position on the interface of the design to the neighboring designs. The interface is defined as the boundary of the design. In some cases certain signals will

have a specific or nondefault signal width assigned to them. Special considerations for signals may include clock signals, signal buses with multiple bits that need to be matched between them, critical path signals, and shielded signals. In Step 1.3 we have to deal with special design requirements such as layout symmetry, specific requirements for latch-up protection, or noise immunity. More examples of special design requirements might be that the design must be pitch matched (i.e., limited in size in one direction), must have a very specific critical path signal, or might be a nonstandard part of the design. Step 1.4 is very important to help finalize the size of the design and estimate the feasibility of meeting all of the design requirements within the area and schedule constraints. Using any previous knowledge about older designs of the same complexity and the process design rules, a layout designer can approximate the size of each component and the complete design. The number of different components to be implemented can be identified and the overall hierarchy or partitioning of the design can be completed. Areas for internal routing and signal connections should be allocated. The routing layer in each interconnect area should be identified. Extra signals or space should be reserved since we have only an educated estimate as to the size of the final design. At this point we should have a preliminary floorplan and implementation strategy. The floorplan should comprise a definition of the interface or boundary with all of the signal ports assigned to their proper locations. Signals with special requirements are identified, and the area impact of these special signals is included in the total area estimate. If it is a hierarchical design, subcomponents are also known with their respective interfaces defined. Spare space and spare signal lines are included in this plan. Step 1.5 is a sanity and cross-check to confirm that all requirements have been met and none missed. There are requirements related specifically to layout guidelines and styles for the process, but also circuit design requirements as well. The floorplan is a communication tool between the layout and circuit designer, as the circuit designer most likely had defined some specific requirements for his or her design and had assumed some kind of layout floorplan in modeling the design for its environment. It is very important to involve the circuit designer in the audit process. The layout audit also relates to the next level of integration for the piece that you designed. The "brick" that you have now floorplanned has to interface perfectly to all of its neighbors and their interfaces; otherwise, when put together it won't work exactly as planned. As an example, the top-level chip design has to fit within the context of the chip package, so a review of any floorplan is very important. The person responsible for integrating your design should audit this floorplan as well to review the requirements related to size of the design, the layout architecture or approach, and your designs interface, among other things. It is not uncommon for audits of really complicated floorplans to require two people: one to check the engineering requirements and another to check

the layout needs. The auditor(s) should be a person who is not directly involved in the design, but who has the expertise to evaluate and appreciate the floorplan quality, and to make constructive comments. To help the auditor perform a proper audit, ideally a checklist is used for each type of layout design. Refer to the addendum checklists for some examples.

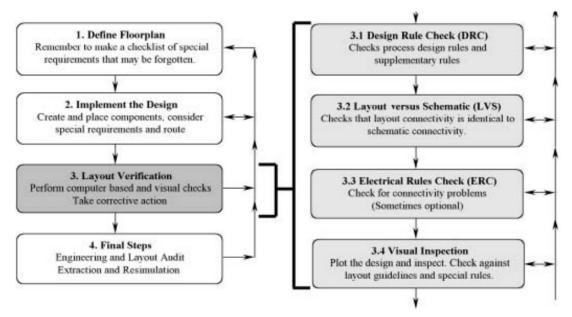

Figure 4: Layout verification steps

- Design Rule Check (DRC): The design rule verification step checks that all polygons and • layers from the layout database meet all of the manufacturing process rules. These design rules define the limits of a manufactural design. Width and space rules fall into this category. Meeting the manufacturing requirements is the absolute minimum rule set that must be checked and corrected. Because this is the first level of verification once the layout is implemented, typically many methodology, connectivity, and guideline rules are checked as well. We refer to these as a set of supplementary rules. An example would be an illegal use of layers (ESD layer in the logic area) or illegal devices or connections. Tip: A truly complete DRC verification approach would be to verify not only the design that you, as a designer, have implemented, but also your design placed within the context in which it is going to be used. If the specific components that will interface or be adjacent to your design are available, perform a DRC check with this interface cell included. If your cell is a general-purpose design, then a more intricate and exhaustive check should be performed, perhaps including all possible interface cells as well as different

- Layout versus Schematic (LVS): LVS verification is checking that the design is connected correctly. The schematic is the reference circuit and the layout is checked against it. In principle, the following is verified:

• Electrical connectivity of all signals, including input, output, and power signals to their corresponding devices.

• Device sizes: transistor width and length, resistor sizes, capacitor sizes.

• Identification of extra components and signals that have not been included in the schematic; floating nodes would be an example of this.

The last item overlaps into the items checked in the electrical rules check, which is described next.

- Electrical Rules Check (ERC): As noted in Figure 4 the ERC is sometimes an optional or seldom used as an independent verification step. Many of the issues are caught by the LVS check, and thus the ERC has become redundant. Electrical rules checked in this step are usually limited to errors in connectivity or device connection. Examples include the following:

- Unconnected, partly connected, or extra devices.

- Disabled transistors.

- Floating nodes.

- Short circuits.

•

• Special checks not checked elsewhere (i.e., antenna rules).

As a subset of the LVS check, an ERC generally executes more quickly and therefore is useful to accelerate debugging problems such as a VDD-to-VSS short circuit.

In the next section, and after giving a complete view of what an analog Layout design flow is, we are going to state the problems of the Layout process, that makes the need of automation mandatory.

### **1.3.** Problem statement

Unlike the digital domain, where Computer-Aided Design tools (CAD tools) are fairly

well developed and commercially available to the design community, and where automatic place

and route (APR) as used to perform the layout with significant sped up in the placing and routing processes, the story is quite different on the analog side.

In fact, physical design automation of analog IC design has seen significant improvement over the past decade, however, it has reached the rate of its digital counterpart. This shortfall is primarily rooted in the analog IC design problem itself, which is very much more complicated even for small problem sizes.

Although analog modules typically contain only a small number of devices compared to digital ones. Analog designs are characterized by a much richer and more complex set of design constraints that need to be considered simultaneously and which may span several domains (e.g., electrical, electro-thermal, electro-mechanical, technological, geometrical domain), this makes the effort needed to automate the analog physical design much more harder than the one needed to automate the digital flow.

Due to the special and necessary constraints imposed on analog layouts, such as:

- Large variation of MOS transistor sizes.

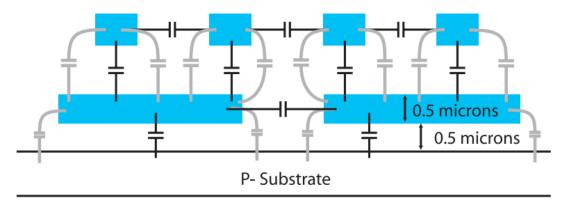

- High Sensitivity to parasitic capacitance. (Ignoring parasitics can kill the chip),

Figure 5: Capacitance is everywhere. Everything is talking to everything else.

• Crosstalk:

- Special device matching requirements for some circuits. (e.g. current mirrors, differential pairs... etc.)

- Symmetry requirements. (Essential to ease the flow of electrons, if the electron life is easy, the chip will perform properly).

- IR drops (In many cases, routing using the minimum width defined in the PDK may degrade the performance from the point of view of the voltage drop, in this case, thicker wires are required, this must be put into consideration).

- Current capability and electro migration.

- Temperature gradients.

The previous constraints maybe divided into four main categories:

(1) Technological constraints: that enable the fabrication and are derived from technology used.

(2) Electrical constraints: that ensure the desired electrical behavior of the design.

(3) Geometric constraints: that are introduced to reduce the overall complexity of the design process, and enhances the yield.

(4) Commercial constraints that arise from chip area or packaging requirements.

This constraint-related problem also makes algorithm and tool development for analog IC design much more difficult as the number of specific design algorithms needed may increase with each new constraint type. Considering today's conventional design algorithm development approach (one constraint type and one algorithm to handle it), its weakness becomes all too apparent when faced with new complex constraints affecting multiple design parameters simultaneously and vastly outnumbering simple constraints. This is one of the primary reasons why conventional analog design automation still lags behind its digital counterpart.

In this project's thesis, our driving constraints are:

- 1) Area: as we are making the layout of bias circuits, which are usually given a small area to fit in the floorplan.

- 2) Placement and routing matching: to ensure that all devices observe the same effect, and are etched in the same manner, and other issues that will be declared

Figure 6: An example for well-matched differential pair

in details in the fourth chapter.

- 3) Current capability and electro migration consideration.

- 4) Symmetry constraint:

Figure 7: Casually placed layout, poor matching.

Symmetry is a major concern in matching devices.

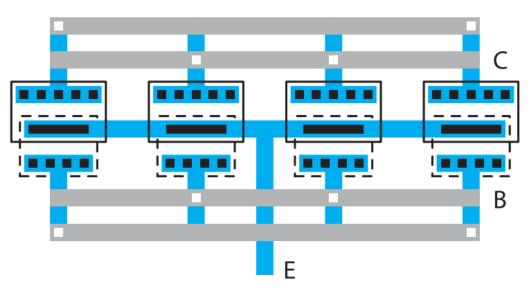

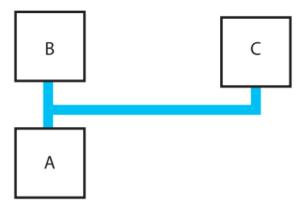

In Figure 3, the output from block A is correctly wired to blocks B and C. It's a fair layout. It will work.

However, block C has a much bigger parasitic on it because you have given it a longer wire. A nicer way to wire these blocks is to imagine a line of symmetry between the blocks, then place the blocks in mirror image on either side of the

Figure 8: Imaginary line of symmetry helps components match.

line.

5) Parasitic capacitances.

These solution approach for all these complex constraints will be described in the coming section.

## **1.4. Solution approach**

This tool tries to use all the constraints mentioned above and combine them to utilize the best solution for the layout (placement and routing).

The tool first takes the total number of devices & minimum spacing of devices from the previously defined PDK and uses these information to determine the best matching pattern for the desired block and then the placement of this patter, taking into consideration all the rules required for perfect matching, such as:

- Keeping devices in the same orientation.

- Placing the root component in the middle.

| dum          | my |  |  |  |  |

|--------------|----|--|--|--|--|

|              |    |  |  |  |  |

| real devices |    |  |  |  |  |

|              |    |  |  |  |  |

|              |    |  |  |  |  |

Figure 9: Real devices encased within a ring of dummy devices.

- Surrounding the devices with dummies to provide protection:

- Match the parasitics on wirings.

• Keeping everything in symmetry.

After achieving the best matching and placement requirements then comes routing phase. While routing the tool trying to preserve some very important constraints first the current capability of each route (make sure that each route can carry the current flowing through it over long periods of time without suffering electro-migration problems)

At the same time the tool is trying to keep the routing of devices a symmetric as possible so that each device can experience same effects from the point of view of parasitics.

The last concern the tool takes in consideration to keep the routing area as minimum as possible by making use of the area above the devices as the tool works for base band circuits that are not very sensitive to parasitics effects.

## 1.5. Organization

In the following chapters we will describe in details the work done and the final output of this work.

In chapter two there is the previous work done in this area and the differences between it and ours.

In chapter 3 we will give an overview of the tool, how to use it and what is the outputs and options available.

In chapter 4 we will talk about different matching techniques and explain in details our algorithm for common centroid matching.

In chapter 5 we will explain in details the routing technique we used and how it was done.

In chapter 6 we will show the results from the tool with explanation for how it works.

In chapter 7 there is a brief summary for this thesis and the future work that will be done.

# Chapter 2. **Background and Related work**

# 2.1. Introduction

Historically analog designers were almost mysterious and old-school as radio frequency (RF) designers. After acquiring years of experience manipulating the many parameters not present in digital designs, analog designers become fountains-of-knowledge in how to add the "secret sauce" to all the different sorts of analog circuits in use today,

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical, but they are not sure

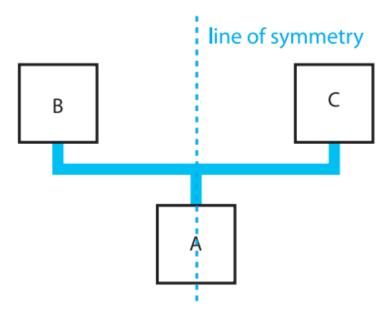

The reason is that there are many more circuit types, each with many more parameters to be optimized, than in the typical digital circuit. Advances have been made for specific circuit types in recent years, but much more needs to be done before analog can be said to have caught up with digital EDA. There are two techniques was developed, which have since been transferred to Cadence, namely "continuous design flow" and "bottom-up meets top-down" design flows.

A continuous layout design flow is a blind spot in today's traditional analog flows,

Figure 10: Layout automation solution approaches

The automation of ANALOG circuit design is likely to play a key role in the design process of mixed-signal integrated circuits (ICs) and application specified integrated circuits (ASICs.)

In the digital domain, computer-aided design (CAD) tools are fairly well developed and commercially available to the design community.

Unfortunately, the story is quite different on the analog side.

Today, analog circuits are still largely being handcrafted with only a SPICE-like simulation shell and an interactive layout environment as the supporting facilities. Due to the special and necessary constraints imposed on analog layouts (e.g., large variation of MOS transistor sizes, sensitivity to parasitic capacitance, crosstalk, device matching, symmetry requirements, voltage drops, current density, temperature gradients, piezoelectric effects, electro migration, etc.),

The analog layout design is intrinsically more difficult than its digital counterpart this is due to technology scaling, the device electrical properties worsen in analog circuits and the design window decreases. Electrical parameters caused by different layout topologies have already become necessary for high-performance circuits even at the circuit design stage. As a result, although analog circuits typically occupy only a small fraction of the total area of mixed-signal ICs, their designs have become the bottleneck, both in design effort and time, as well as test cost. Moreover, analog circuits are often responsible for the design errors and the expensive design iterations.

So far, several CAD tools have been developed to automate the generation of analog layouts. However, as some of these tools are developed for the system designers, the circuit designers tend to experience difficulties to integrate their design knowledge and experiences into the design flow. We will demonstrate a novel automated layout design

tool, named as automatic layout design aid for analog integrated circuits (ALADIN) also we will tackle many tools called LAYLA and AIDA. This tool (ALADIN) allows analog circuit experts to integrate their specific knowledge and experiences into the synthesis process to create high-quality layouts. The designers can construct layouts made of parameterizable modules in a technology and application-independent fashion. The placement and the routing of modules are performed automatically under the constraints tailored for applications.

these tools used to automate the generation of analog layouts have been developed. Usually, these tools apply a top down approach taking the already optimized circuit netlist as input and generating the layout for the circuit.

The use of procedural generators is one of the most mature layout automation techniques used for analog circuits. In these systems, specific software is written to support each unique circuit topology and the analog specific knowledge about the layout is coded into the software itself. Its major disadvantage is that they require a large coding effort for each new topology. Therefore, it is not a good choice for an environment requiring a large variety of circuit topologies.

Conway and Schrooten two famous scientists developed a template driven analog layout system. For a given module type, a template module layout is created once by an expert designer. To obtain real layout, the modules in the template are enlarged, compacted and then connected. Although this technique produces good quality layout in a reasonable amount of time, a template has to be created for each new type of circuit that limits the generality of this method. Moreover, the library of templates has to be updated for each new technology.

A variety of analog layout generation and some tools are reviewed next. First attempts for analog layout automation was known as procedural generation. Procedural module generation used parametric cell which is commonly known as pCell. The parametric cell concept is coding the entire layout of a circuit in a software tool. Hence, it is fully developed by the designer. A tool called ALSYN uses fast procedure algorithms.

However, this method lacks the flexibility to adapt to wide changes. Hence, the cost of making a new design is high and technology migration may need redesign.

The second type is template based. It uses a pre-defined template that has the relative position and interconnection of devices. A tool called IPRAIL, which stands for Intellectual Property Reuse-based Analog IC Layout, extracts the information from already made layout automatically for retargeting purposes. Layout retargeting means using an existing layout to generate a new layout. Hence, this method can be used for technology migration, update specifications, or optimizing the old design. A tool is introduced by Po-Hsun to generate a new layout by integrating existing design expertise.

The third type is optimization based. These approaches synthesize the layout by means optimization techniques based on some cost functions. This type is easier to implement compared to procedural and template-based approaches.

Now, let us consider commercial solutions. Virtuoso® Layout Suite Family made the creation and navigation in a complex design. This method manages multiple abstraction levels for device, cell, block, and chip levels. Moreover, it contains different level of assistance Basic design creation assisted correct-by-construction wire-editing functionalities to ensure real time process, Hierarchical designs intent for schematic editor. Synopsys'® Galaxy Custom Designer LE also offers a set of automation functionalities for layout generation. It has an automatic guard ring generator which creates guard rings in real-time and it is easily edited. Furthermore, user assisted applications as auto connect features, interactive bus routing with different via pattern choices align assist displays with interactive alignment, commands to specify locations to create bridges or a tunnel for routing, these frameworks adds several functionalities to speed-up layout design.

The gap between electrical and physical design needs to be closed by ensuring that the post layout performance is guaranteed in the presence of layout parasitic. Iterations between the physical design and the electrical simulation is ineffective as it is a time-

consuming process. The proposed solution is using a layout-induced effects in the circuit sizing phase to overlap electrical and physical design phases. Hence, parasitic-aware, layout-aware or layout-driven sizing should be made. Device parasitic effects are modelled by linear regression obtained by sampling the design space and with means of procedural generator it produces the layout for each point, where each solution is aware of its specific layout induced effect. Hence, the effects can be expected without actually generating the layout in real-time. Moreover, the parasitic effects are modelled in the circuit equations. Hence, a deterministic nonlinear optimization algorithm is used to determine the device sizes.

# 2.2. Prior work

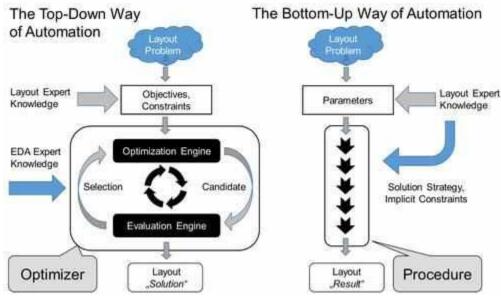

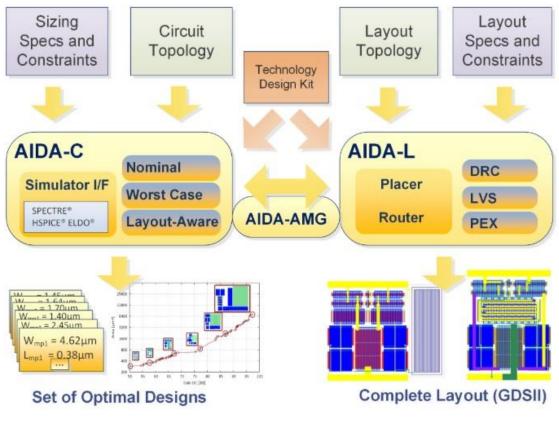

The Analog IC Design Automation (AIDA) framework implements an analog IC design flow from circuit-level specification to a physical layout description focusing on design optimizing and porting using highly efficient searching methods combined with accurate circuit-level simulation, layout design rules and parasitic extraction engines.

Figure 11: AIDA tool

AIDA assists expert analog IC designers by automating the most timeconsuming and repetitive tasks from the typical analog IC design flow. AIDA-C automates circuit sizing with high accuracy and within a reduced time frame. AIDA-L generates the complete layout for sized circuits, from device placement to detailed routing.

Analog and Mixed-Signal (AMS) systems are found in a wide range of applications, such as, communications, medical or multimedia applications. These extremely competitive markets force the analog designer to face the complex design challenges within strict and demanding timeframes. Today's analog design is supported by circuit simulators, layout editing environments and verification tools, however the design cycle for AMS ICs is still long and error-prone.

AIDA's framework targets the analog IC design automation while keeping the common design flow by involving the designer and his (her) knowledge and focusing on efficiently automating repetitive design tasks. Thus, facilitating design reuse and fast

response to specification changes of analog cells like VCO, LNA, voltage mixer, differential amplifiers, band gap voltage references, integrators, comparators, etc..

AIDA framework is composed by two main modules: AIDA-C and AIDA-L. AIDA also includes an intuitive GUI allowing the designer to manage and interact with the design automation process.

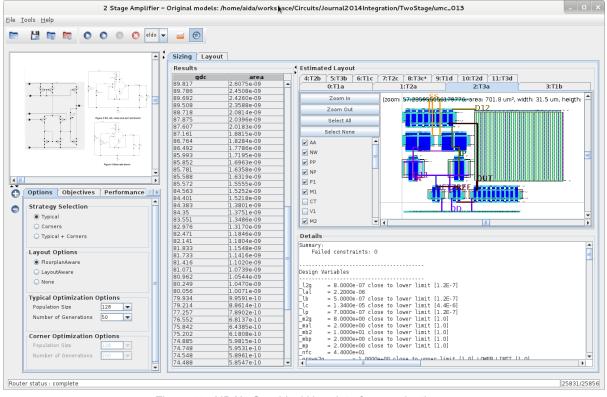

Figure 12: AIDA's Graphical User Interface navigating the sizing solution set and showing the corresponding floorplan and global routing.

The AIDA framework implements an automatic analog IC design flow from a circuitlevel specification to a physical layout description. The circuit-level synthesis is done by AIDA-C, and after the circuit-level design, AIDA-L takes the device sizes and the best floorplan, and generates the complete layout, which is then saved as a GDSII stream format.

AIDA-C is a circuit-level synthesizer supported by state-of-the-art multi-objective

optimization kernels, where the robustness of the solutions is attained by considering user-defined worst case corners, that account for process variations and(or) PVT corners. The circuit's performance is measured using Spectre®, Eldo® or HSPICE® electrical circuit simulators

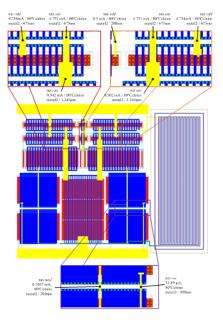

. AIDA-L considers sized circuit to generate the complete layout by placing and, routing the devices, while fulfilling the technology design rules by using built-in DRC and LVS procedures. The router takes into account the circuit's currents to mitigate electro migration and IR-drop effects, and a fast but accurate PEX procedure provides parasitic estimates to be used in AIDA-C layout-aware optimization.

The framework's technology independent module generator, AIDA-AMG, is capable of creating several, simple and complex, device layout styles, allowing AIDA-C floorplan-aware sizing approach to explore a much wider space of solutions leading to higher quality layouts.

# 2. **ALADIN:** A Layout Synthesis Tool for Analog Integrated Circuits

BASIC ARCHITECTURE AND SYNTHESIS FLOW IN ALADIN:

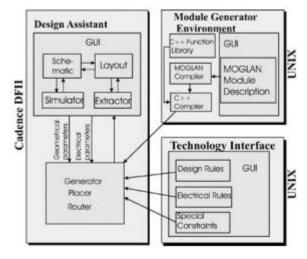

The block diagram of ALADIN is depicted in Fig. 2. The entire system consists of three major components.

1) Module Generator Environment: It allows circuit designers to write technology- and

application-independent parameterizable modules as complex as needed

2) Design Assistant: It is integrated into Cadence Design Framework II (DFII)

and can be easily ported to other commercial CAD software. It provides a graphical user interface (GUI) to help optimize an analog circuit from schematic to layout.

3) Technology Interface: It eases the input of description rules including the design rules, the electrical rules, and the special design constraints.

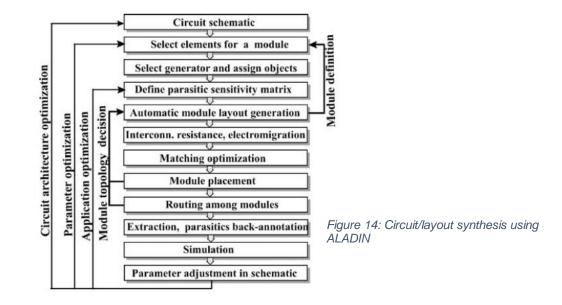

The circuit/layout synthesis using ALADIN is illustrated in Fig. 3. A simulated circuit is partitioned into several modules. The parasitic capacitance in the module

Figure 13: Block diagram in ALADIN

layout is controlled by a capacitance sensitivity matrix, and the electrical rules, such as electro migration, matching, etc., are considered during the module generation/

The module selection and the layout generation are repeated until all the modules of the circuit are defined.

In the next step, the placement of the modules is performed simultaneously with the global routing. During the placement and the global routing, an appropriate topology of each module is chosen from all possible alternatives available in the design library. The layout synthesis flow is completed by the detailed routing with an embedded layout compaction capability. After the layout generation, an extraction is performed and the extracted parasitic elements are automatically annotated back into the schematic. The entire circuit is then simulated with accurate parasitic estimation, and the optimization loop starts.

#### These feedback optimizations include three important Techniques:

1) the application optimization that redefines the electrical constraints, such as the capacitance sensitivity matrix, to update the detailed module generation and the routing process;

2) the parameter optimization that changes circuit parameters and performs the layout generation for the impacted part of the circuit; and 3) the circuit architecture optimization that changes the structure of the circuit and, thus, undergoes a major update of the layout generation.

# 3. LAYLA the Analog Layout Tool

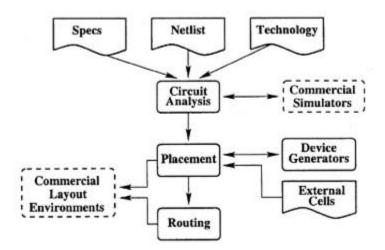

Fig. 4 gives an overview of a set of tools which have been developed to solve the analog circuit level layout generation problem. Together they provide an integrated framework, called LAYLA, for performance driven analog and mixed-signal layout design. Tools developed within the framework of this research are shown in straight lines, commercial tools that have been integrated in dashed lines.

We will pass upon all phases of the tool from circuit analysis reaching to routing and testability

The input of the tool set consists of three files:

1. Netlist file: The netlist describing the circuit for which the layout has to be designed this can be a device level netlist, or an architecture of higher levels blocks.

2. Specification file: A file with the specifications for the circuit.

3. Technology file: A file describing the process technology.

Figure 15: Software Architecture of LAYLA

#### **<u>Circuit Analysis</u>**

Before the actual layout process can be started, a number of numerical simulations has to be run to determine the necessary electrical information about the circuit. A circuit analysis program is used to automate this process.

The program interfaces is a commercial simulator. It generates a number of input files that runs the simulations and docs the post -processing of the simulator output. The most important task of the circuit analyzer is to extract the Sensitivities of the circuit performance characteristics with respect to all layout parasitics. The concept of sensitivities and how they are used to calculate performance degradation

#### **Device Generation**

A library of procedural device generators is used to create the layout tor basic devices (transistors, capacitors and resistors). The generators can be called in interface mode and in layout mode.

In interface mode they generate a list of possible layout variants for a device, based on its electrical parameters. Only the information necessary for the placement tool is generated:

the bounding box for the device and the terminal geometry.

After placement, the device generators are called again in layout mode to generate the complete layout for one selected variant. Special features have been added to the device generators, in order to make them suitable for use in a mixed-signal context.

#### **Placement**

The task of the placement tool in to select an optimal position, orientation and implementation for each device in the circuit, the freedom in placing these devices is used to control the layout-induced performance degradation within the margins imposed by the designer's specifications.

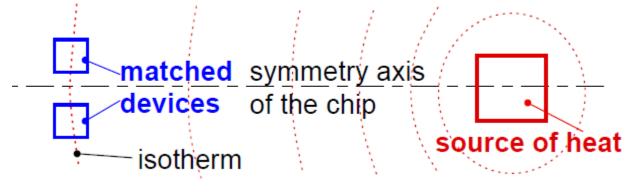

During each iteration of a simulated annealing optimization algorithm, the layout-induced performance degradation is calculated from the geometrical properties of the intermediate solution. The cost-function is designed to control performance degradation due to interconnect parasitics, mismatch and thermal effects.

#### **Routing**

The main task of the performance driven router is to route the circuit such that the performance degradation caused by the interconnect parasitic remains within the specification margins imposed by the designer

For a given set of circuit specifications, several valid routing solutions, can be found. Among these, the routing algorithm selects the solution that additionally maximizes the yield and the testability of the resulting layout. Initially, the circuit is routed with a cost function designed to enforce all performance constraints. After all nets have been routed, the layout parasitics are extracted and the performance of tile circuit is verified. In a second phase, nets are pipped up and rerouted to optimize the yield and the testability of the layout

The following table 2.1 shows analog layout aware sizing tools

| Table 2.4 Con        | nparison between sta                                | Table 2.4 Comparison between state-of-the-art works on layout-aware sizing with special emphasis to layout-related data included in-loop | ayout-aware                  | sizing     | with specia      | al emphasi       | is to layout-rela | ted data inclu | ded in-loop                                                                                       |

|----------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|------------------|------------------|-------------------|----------------|---------------------------------------------------------------------------------------------------|

|                      | Layout Generator                                    |                                                                                                                                          | Layout-related data included | ted data   | included         |                  |                   |                |                                                                                                   |

|                      |                                                     |                                                                                                                                          |                              | Parasitics | tics             |                  |                   |                |                                                                                                   |

| Work                 | Placer                                              | Router                                                                                                                                   | Geometric                    | Bulk       | Intra-<br>device | Inter-<br>device | Interconnect      | Resistances    | Observations                                                                                      |

| Vancor. [99]         | Procedural generator                                | or                                                                                                                                       | >                            | ×          | >                | ×                | `                 | >              | 1/2-D analytical-<br>geometrical modeling of<br>the critical nets; geometr<br>data with equations |

| Pradhan [94]         | Procedural generator (design space<br>sampled only) | or (design space                                                                                                                         | >                            | 5          | >                | ×                | ×                 | ×              | Analytical models for bu device and interconnect                                                  |

| Liao [96]            | Template-based/<br>user-assisted                    | Channel router                                                                                                                           | >                            | ×          | >                | >                | >                 | >              | Analytical models for ar<br>and interconnect                                                      |

| Youssef [97]         | Device-level procedural generator                   | dural generator                                                                                                                          | >                            | >          | >                | ×                | ×                 | ×              | Modeling of the stress<br>effects of the devices                                                  |

| Ranjan [95]          | Procedural generator (design space<br>sampled only) | or (design space                                                                                                                         | >                            | ×          | >                | >                | >                 | >              | Area and interconnect<br>using external extractor                                                 |

| Habal [103]          | Enumeration of<br>all possible<br>floorplans        | Exhaustive setup<br>for Cadence Chip<br>Assembly Router®                                                                                 | >                            | >          | >                | >                | >                 | >              | Complete extraction usir<br>Cadence Assura®                                                       |

| Lopez [100,<br>101]  | Coded<br>slicing-tree                               | Template-based                                                                                                                           | >                            | ×          | >                | >                |                   | ×              | 3-D analytical-geometric                                                                          |

| Berkol [102]         | Layout description script                           | script                                                                                                                                   | >                            | >          | >                | >                | >                 | >              | Complete extraction usin external extractor                                                       |

| This work,<br>AIDA-L | Template-based<br>Placer with<br>multiple B*-trees  | Automatic<br>electromigration-<br>aware WT and<br>global routing<br>in-loop                                                              | `                            | >          | >                | `                | `                 | `              | 2.5-D modeling of the devices and routing that operates over non-detail routing                   |

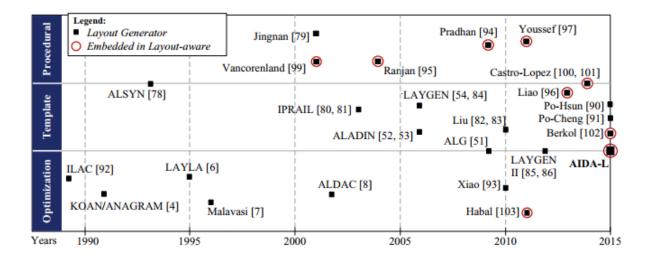

The following diagram shows a Chronological representation of analog layout generators.

Figure 16: Chronological representation of analog layout generators

# **Conclusion:**

A flexible module generator environment is developed, which allows designers to develop and maintain technology and application-independent module generators for relatively complex sub circuits.

A two-stage placement technique is proposed to dramatically improve the placement accuracy without compromising the computation efficiency compared to the one-stage placement. The analog module routing consists of the global routing and the detailed routing. The minimum-Steiner tree based global routing is integrated into the placement procedure to improve reliability and routability of the searched placement solutions. The final layout is completed by a compaction-based constructive detailed router. The benefit of ALADIN is demonstrated by applying it to designing a number of circuits. Our technical analyses and experimental results have confirmed its competition over some existing automation tools and expert handcrafted layouts.

## Chapter 3. **Tool Overview**

## **3.1 Intro and Features**

- 3.2 User Guide

- i- <u>Step One</u>

- ii- <u>Step Two</u>

- iii- <u>Step 3</u>

- iv- <u>Output</u>

## **3.1. Intro and features**

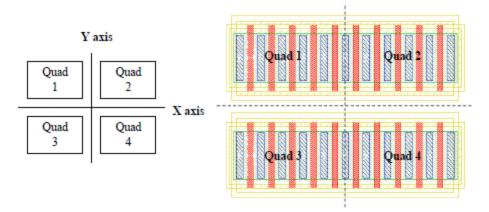

ACML tool aims at automating the whole flow of creating a full current mirror layout (clean LVS and DRC Verification checks) guided by the user preferences to decide between wasted area and parasitics.

ACML is technology independent, it is optimized for small minimum feature length ( $\lambda$ ) currently used like 7nm and 5nm. The layouts generated are of industrial quality, they are approved by experienced layout engineers inside the industry.

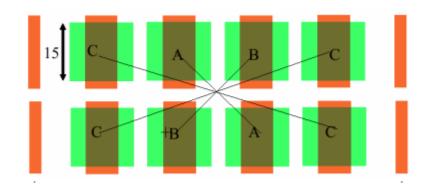

#### Features of Pattern Generator (Placement)

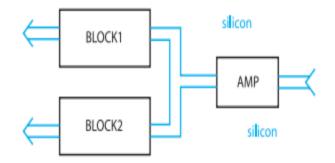

1- Shared Source

The user is given an option between sharing sources or not. This depends on the project requirements if the area is more important and we want to minimize parasitics then we choose to source share. However, if the area requirement is slightly relaxed and requirement on stresses being equal on all devices is more important, then the user may disable source sharing.

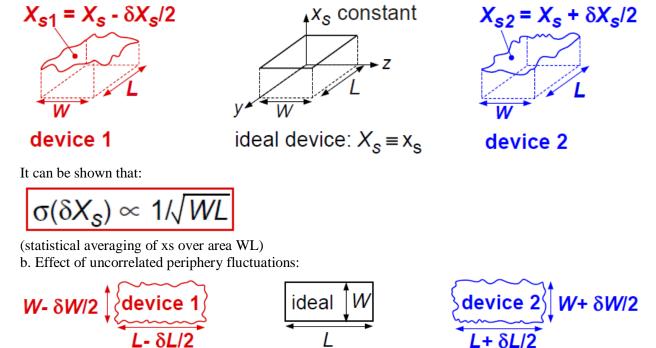

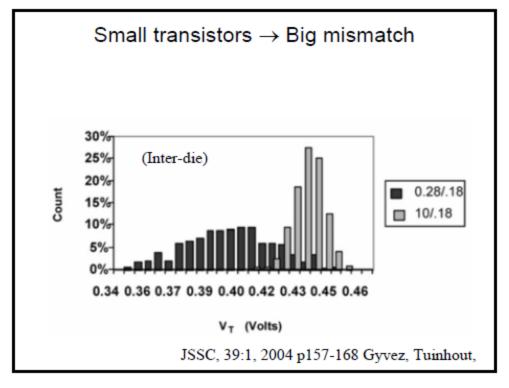

#### 2- Width Division

Odd number of units represents a challenge for the quality of matching, 2 solutions are offered by ACML. First solution is to divide the width of the unit and thus doubling the number of all units and getting rid of odd numbers. This solution optimizes the use of area as it avoids the use of dummies. However it has other drawbacks, if units were already of small width, minimum width of the technology may be hit, also small units match worse because random mismatches are more significant (refer to matching section).Second solution is to get rid of those odd number of units by adding dummies. However this solution has another drawback as there will be a wasted area.

#### 3- Choosing the convenient pair

ACML tool doesn't include floorplanning, however, it makes this process easier for the user. It provides a list of all possible pairs with their actual lengths and widths. These pairs are arranged according to their aspect ratio and this list states if routing will require any excess space for each pair.

#### 4- Good aspect ratio

Sometimes if the total is a prime number, the only possible pairs have very bad aspect ratios, ACML solves this problem by adding one dummy device to get a total that has many factors, and thus many possible pairs with decent aspect ratios.

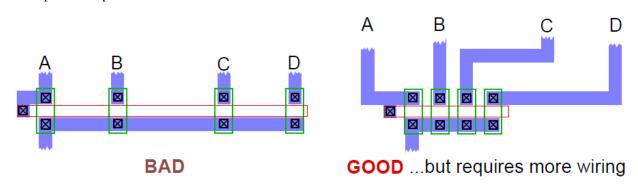

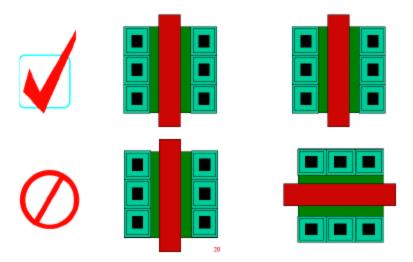

#### 5- Minimize the number of Devices on the same row

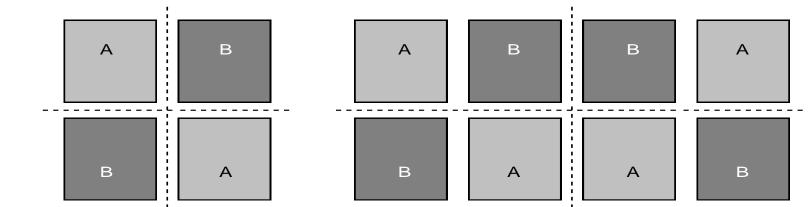

Devices are arranged inside the pattern taking into consideration that we need to minimize the number of different devices in the same row for better routability.

Example:

| Table 1: I | BAD for | routability | matching | pattern | example |

|------------|---------|-------------|----------|---------|---------|

|------------|---------|-------------|----------|---------|---------|

| F | В | D | Е | C | G | No: 5 |

|---|---|---|---|---|---|-------|

| F | F | С | В | D | G | No: 5 |

| В | Е | А | А | C | G | No: 5 |

| G | С | А | А | Е | В | No: 5 |

| G | D | В | С | F | F | No: 5 |

| G | С | Е | D | В | F | No: 5 |

Table 2: good for routability matching pattern example

| В | F | В | F | F | В | No: 2 |

|---|---|---|---|---|---|-------|

| G | С | G | С | С | G | No: 2 |

| D | Ε | А | А | Ε | D | No: 3 |

| D | Ε | А | А | Ε | D | No: 3 |

| G | С | С | G | С | G | No: 2 |

| В | F | F | В | F | В | No: 2 |

#### 6- Similar number of Devices between all rows

Sometimes number of different devices in a certain row is very large compared to the rest of rows, this causes waste of routes as the number of

routes placed on each row is determined by the largest number (maximum in all rows).

ACML tries to avoid this problem by making the number of different devices in all rows similar to each other.

Example:

| Е | Е | E | E | Е | F | No:2 |

|---|---|---|---|---|---|------|

| D | С | В | В | С | D | No:3 |

| А | А | А | А | А | А | No:1 |

| А | А | А | А | А | А | No:1 |

| D | С | В | В | C | D | No:3 |

| F | Е | Е | Е | Е | Е | No:2 |

Table 3: Matching pattern example 3

There is a waste in the routes in row 3 and row 4

Table 4: Matching pattern example 4

1

| Е | C | Е | Е | C | F | No:3 |

|---|---|---|---|---|---|------|

| D | Е | А | А | Е | D | No:3 |

| В | А | А | А | А | В | No:2 |

| В | А | А | А | А | В | No:2 |

| D | Е | А | А | Е | D | No:3 |

| F | С | Е | Е | С | Е | No:3 |

7- Putting the diode connected device as the reference

ACML's matching pattern puts into consideration that the diode connected device must be placed in the center of the pattern, as it is the reference device. The centroid of all devices must coincide with the centroid of this device.

#### Features of Router:

1- Area of routes is within the area of the mirror

We route all the route we need over the transistors and bulk connection se we don't take any extra area and this minimize the area needed for a current mirror and this decrease its area in the whole ship which give the designers a larger space to put other circuits

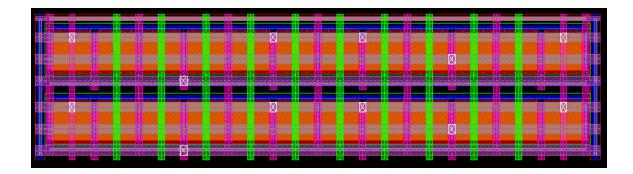

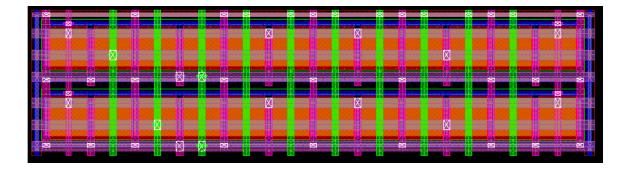

2- Routes are matched

We route equal number of routes over the transistors so all of them see the same resistance and capacitance so we don't affect the matching of the transistors and the extra rails are all connected together and also connected to the VSS in case Nmos and VDD in case of PMOS

3- Metal routes are convenient to the current flowing in them

To prevent electro migration we calculate each route width after knowing the current passes through it in order to be reliable and no current problems occurs.

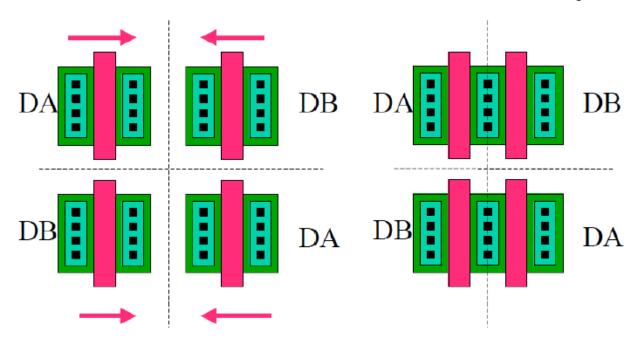

4- Minimal Gate resistance

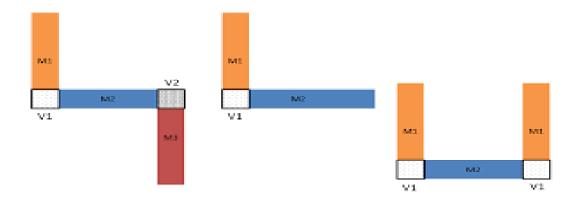

The tool we are working in it (synopsis tool) can place the transistor with all the gates connected together by polysilicon but from the training we took at silicon vision under the supervision of Eng. Fady we know that it is not good to connect between gates by poly as this puts a lot of resistance and capacitance on the gate as polysilicon has high resistance and capacitance per unit area

So to avoid this disadvantage and to make our product aligned with the industry we place the transistor without the default gate connection and we will make this connection to each finger alone then connect all the gates together with metal 1 so now the poly is not used to connect all gates

5- Clean LVS and DRC Verification

Our mirror passes the layout versus schematic test successfully and also

basses all DRC rules.

## 3.2. USER GUIDE

## i- <u>Step One</u>

Selection of required current mirror

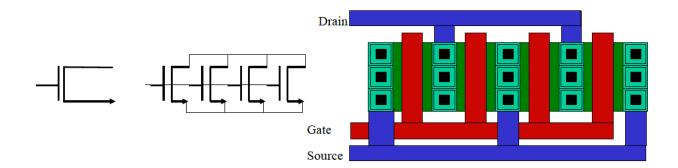

Figure 17: CM schematic Before Selection

Figure 18: Tool's GUI interaction with user

Figure 19: Tool's GUI response for user selection

| After   | selection,        | а            | dialog | box | appears |

|---------|-------------------|--------------|--------|-----|---------|

|         | Current Mirro     | or Generator | ×      |     |         |

| Techno  | ogy Parameters:   |              |        |     |         |

|         | Minimum Width:    | 0.16u        |        |     |         |

|         | Device Width:     | 4.0u         |        |     |         |

|         | Device Length:    | 4.0u         |        |     |         |

|         | Ties Width:       | 0.5u         |        |     |         |

|         | Gate Width:       | 0.02u        |        |     |         |

| 1       | Diffusion Length: | 0.5u         |        |     |         |

| Min     | imum Metal DRC:   | 0.16u        |        |     |         |

| Minimu  | m Diffusion DRC:  | 0.2u         |        |     |         |

| Nu      | mber of Devices:  | 4            |        |     |         |

| Pattern | Parameters :      |              |        |     |         |

| Sol     | urce Share        |              |        |     |         |

|         | lth Divide        |              |        |     |         |

Figure 20: Inputs for GUI

This dialog box lets the user provide the inputs required for the pattern generator

First category of inputs, are the technology dependents inputs which include:

-Minimum width

- Ties width

-Gate width

-Diffusion length

-Minimum DRC between metal rails

-Minimum DRC between diffusion areas

Another category of inputs are inputs that depend on the current mirror selected which are:

-Finger width

-Finger length

-Number of devices

And the last input is passed automatically to the pattern generator which is the number of units for each device (number of fingers \* number of multipliers)

Last category of inputs is the features inputs which are:

-Source sharing is applied or not

-Width division is allowed or not (Dummies are allowed or not): not allowing width division implies the use of dummies

#### iii- <u>Step Three</u>

| currents:                              |                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current of Device 1:                   | [1                                                                                                                                                                                                                                                                                                                                                                                                         |

| Current of Device 2:                   | 2                                                                                                                                                                                                                                                                                                                                                                                                          |

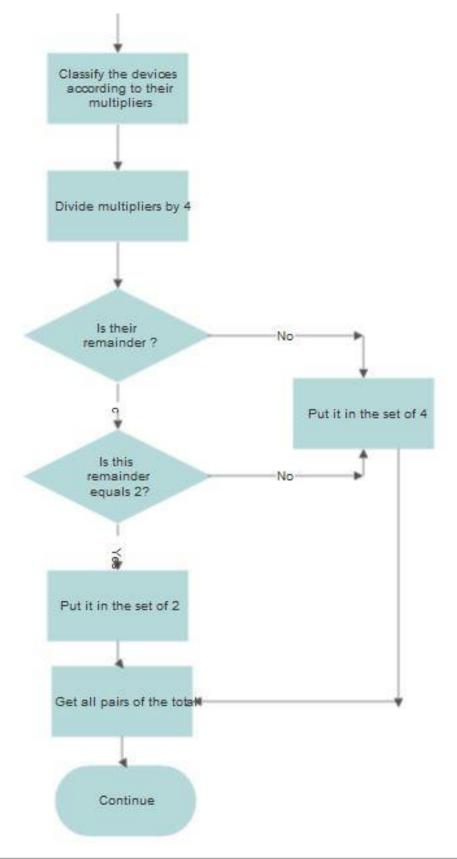

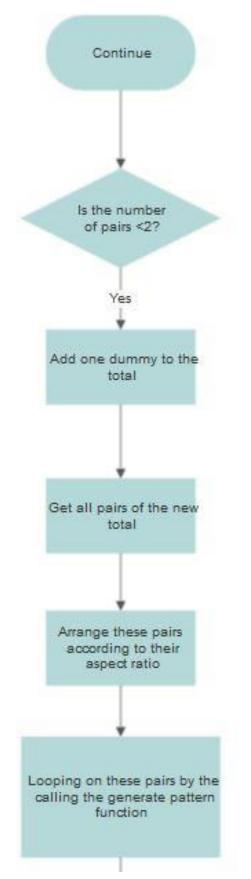

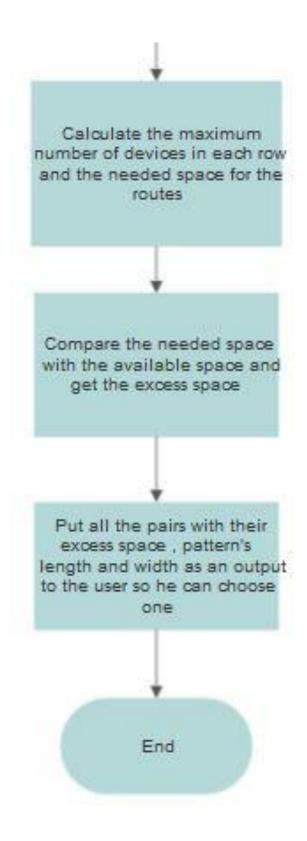

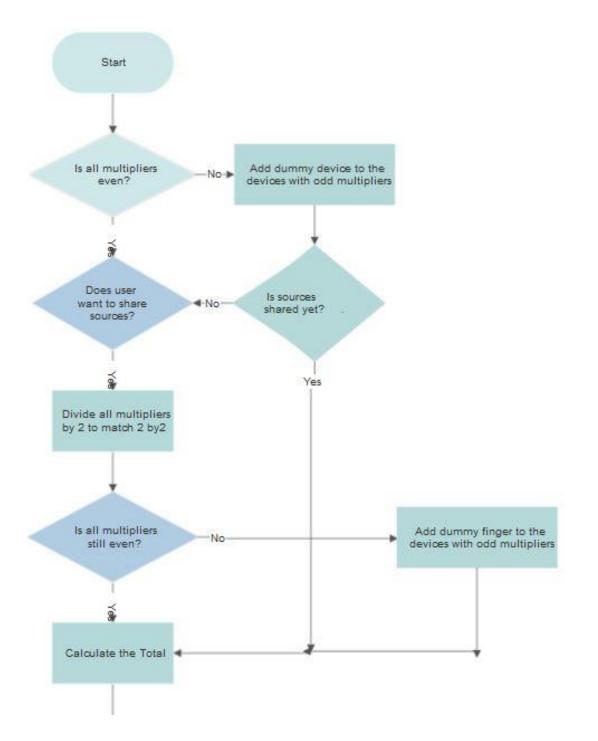

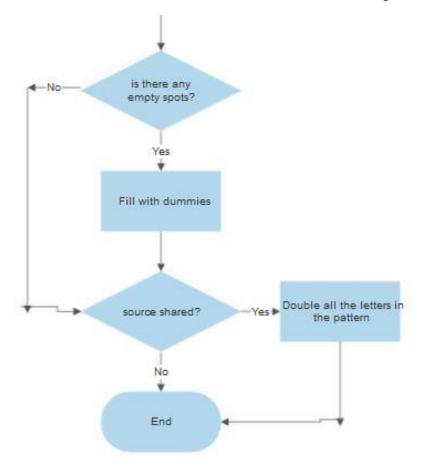

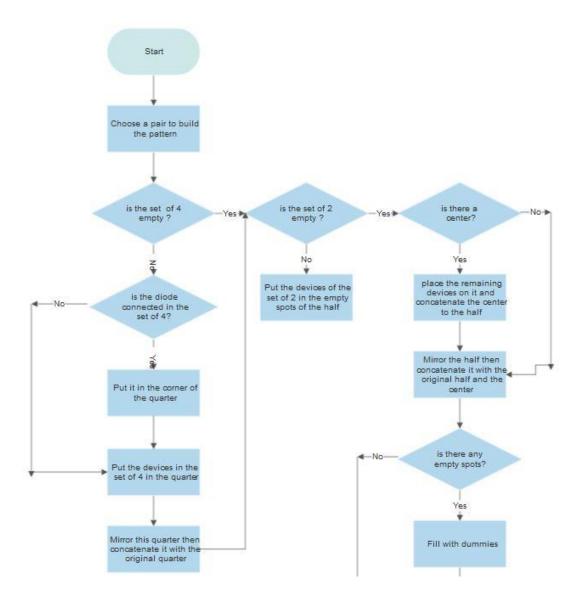

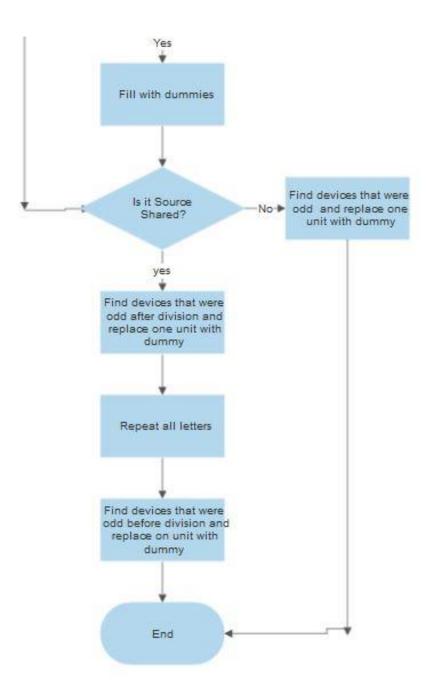

| Current of Device 3:                   | 3                                                                                                                                                                                                                                                                                                                                                                                                          |