#### **Project Team**

Belal Mohamed Ibrahim Fawzy Saleh Ramadan Saleh Othman Tarek Mohamed Sayed Hussein Tarek Khaled Farouk Abdelshafi Khaled Hassan Sayed Hassan Abdelrahman Ahmed Saad Hassan

Supervised by

## Dr. Hassan Mostafa

Sponsored by

## **Siemens EDA**

A Graduation Project Thesis In Partial Fulfillment of the Requirements for the Degree of Bachelor of Science Electronics and Electrical Communications Engineering Faculty of Engineering, Cairo University Giza, Egypt July 2022

# Table of contents

| Chapter 1: Introduction                           |    |

|---------------------------------------------------|----|

| 1.1 Motivation                                    | 12 |

| 1.2 DRAM Background and DDR5                      | 12 |

| 1.2.1 DRAM Basics                                 | 12 |

| 1.2.2 DDR5 Standard                               | 15 |

| 1.3 HIGH COMPLEXITY AND THE NEED FOR VERIFICATION | 16 |

| 1.4 Thesis scope                                  | 17 |

| 1.5 Thesis organization                           | 17 |

| Chapter 2: Design                                 |    |

| 2.1 Overview                                      |    |

| 2.1.1 Basic Features                              |    |

| 2.1.2 Optional Features                           | 19 |

| 2.1.3 Excluded Features                           | 19 |

| 2.2 Scope of Our Design                           | 19 |

| 2.3 Inputs and Outputs of Top Module              | 20 |

| 2.4 Operation of Controller                       | 22 |

| 2.5 Design in Detail                              | 23 |

| 2.5.1. Command_Decoder                            | 23 |

| 2.5.2 Command_Address_FIFO                        | 28 |

| 2.5.3 Write_Data_FIFO                             | 29 |

| 2.5.4 Calculation of Depth of FIFOs               |    |

| 2.5.5 Counters                                    | 31 |

| 2.5.6 Command_FSM                                 |    |

| 2.5.7 Initialization_FSM                          | 46 |

| 2.5.8 Self Refresh_FSM                            | 51 |

| 2.6 Design Enhancement                            | 56 |

| 2.6.1 Read_FSM                                    | 57 |

| 2.6.2 Write_FSM                                   | 60 |

| 2.6.3 Selection Decoder                           | 64 |

| Chapter 3: Introduction to Cocotb                 | 67 |

| 3.1 Introduction                                  | 67 |

| 3.2 Background                                                    | 67 |

|-------------------------------------------------------------------|----|

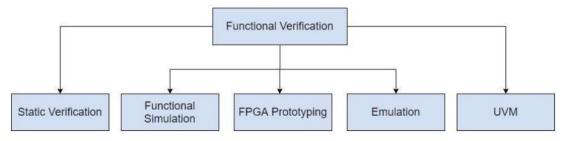

| 3.2.1 Functional Verification                                     | 68 |

| 3.2.2 Switching to Python                                         | 69 |

| 3.3 Design Verification using Cocotb                              | 69 |

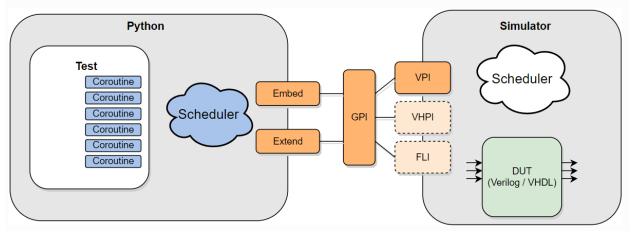

| 3.3.1 Architecture of Cocotb                                      | 70 |

| 3.3.2 Design Methodology                                          | 70 |

| 3.3.3 Cosimulation                                                | 71 |

| 3.4 Cocotb Coverage                                               | 71 |

| 3.4.1 Functional Coverage in SystemVerilog                        | 71 |

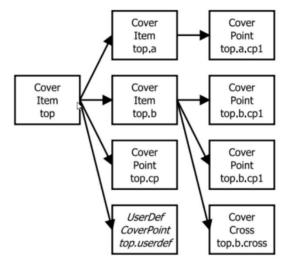

| 3.4.2 Functional Coverage with Cocotb-coverage                    | 72 |

| 3.4.3 Constrained Random Verification Features in SystemVerilog   | 73 |

| 3.4.4 Constrained Random Verification Features in cocotb-coverage | 73 |

| 3.5 Code Coverage                                                 | 74 |

| 3.5.1 Statement coverage/ Line coverage                           | 75 |

| 3.5.2 Block/ Segment coverage                                     | 75 |

| 3.5.3 Conditional coverage                                        | 75 |

| 3.5.4 Branch coverage                                             | 75 |

| 3.5.5. Toggle coverage                                            | 75 |

| 3.5.6. Path coverage                                              | 75 |

| Chapter 4: Block Level Verification                               | 76 |

| 4.1 Goals and Overview                                            | 76 |

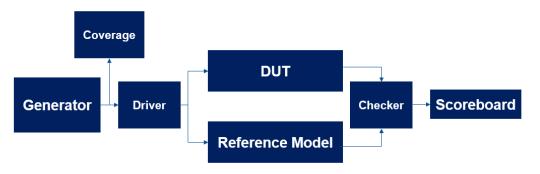

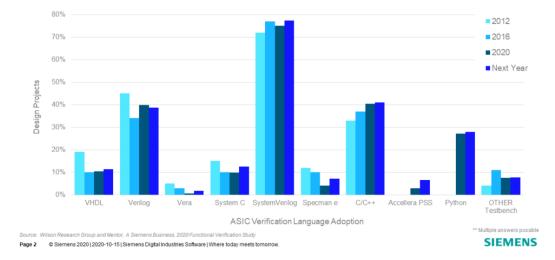

| 4.2 Block Level Testbench Architecture                            | 76 |

| 4.3 Command Decoder Verification Plan                             | 76 |

| 4.3.1 Functional Coverage Plan                                    | 76 |

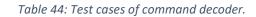

| 4.3.2 Test Cases                                                  | 77 |

| 4.3.3 Reported Bugs                                               | 80 |

| 4.3.4 Functional Coverage Results                                 | 83 |

| 4.3.5 Code Coverage Results                                       | 84 |

| 4.4 Command Finite State Machine                                  | 84 |

| 4.4.1 Functional Coverage Plan                                    | 84 |

| 4.4.2 Test Cases                                                  | 85 |

| 4.4.3 Reported Bugs                                               | 94 |

| 4.4.4 Functional Coverage Results                                 |    |

| 4.4.5 Code Coverage Results                   |  |

|-----------------------------------------------|--|

| 4.5 Self_Refresh Finite State Machine         |  |

| 4.5.1 Functional Coverage Plan                |  |

| 4.5.2 Test Cases                              |  |

| 4.5.3 Reported Bugs                           |  |

| 4.5.4 Functional Coverage Results             |  |

| 4.5.6 Code Coverage Results                   |  |

| 4.6 Initialization Finite State Machine       |  |

| 4.6.1 Functional Coverage Plan                |  |

| 4.6.2 Test Cases                              |  |

| 4.6.3 Reported Bugs                           |  |

| 4.6.4 Functional Coverage Results             |  |

| 4.6.5 Code Coverage Results                   |  |

| 4.7 Counters                                  |  |

| 4.7.1 Functional Coverage Plan                |  |

| 4.7.2 Test Cases                              |  |

| 4.7.3 Reported Bugs                           |  |

| 4.7.4 Functional Coverage Results             |  |

| 4.7.5 Code Coverage Results                   |  |

| Chapter 5: UVM VS COCOTB                      |  |

| 5.1 Introduction                              |  |

| 5.1.1 UVM verification                        |  |

| 5.1.2 UVM verification environment components |  |

| 5.2 Verification Plan                         |  |

| 5.2.1 Testing scenarios:                      |  |

| 5.3 Results from UVM verification             |  |

| 5.4 Results from COCOTB verification          |  |

| 5.5 History of verification methods:          |  |

| 5.6 Tradeoffs between using UVM and COCOTB:   |  |

| Chapter 6: Top Level Verification             |  |

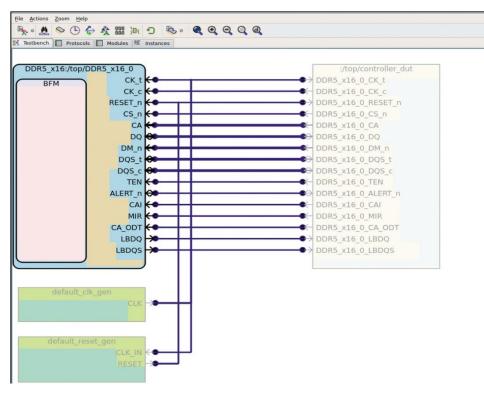

| 6.1 Verification Environment                  |  |

| 6.2 Functional Coverage Plan:                 |  |

| 6.3 Reported Bugs:                            |  |

|                                               |  |

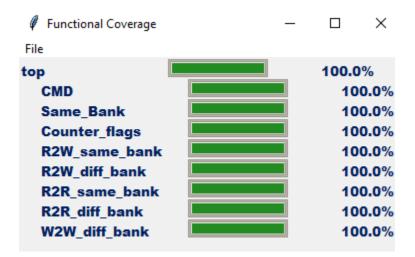

| 6.4 Functional coverage results:         | 121 |

|------------------------------------------|-----|

| 6.5 Code coverage results:               |     |

| 6.6 Final Results                        |     |

| 6.6.1 Initialization Sequence            | 122 |

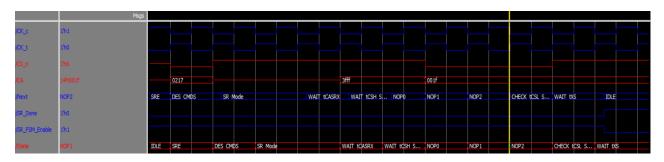

| 6.6.2 Self-Refresh Sequence              |     |

| 6.6.3 Single Read after Write            |     |

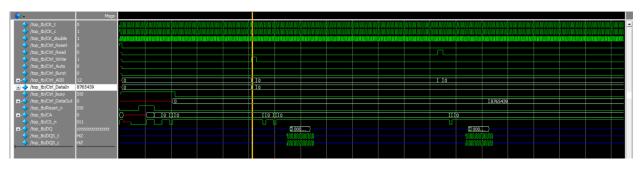

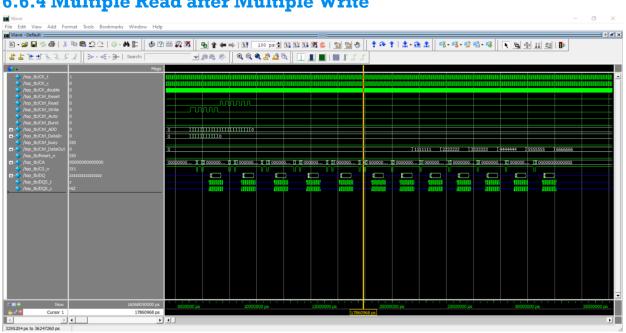

| 6.6.4 Multiple Read after Multiple Write | 123 |

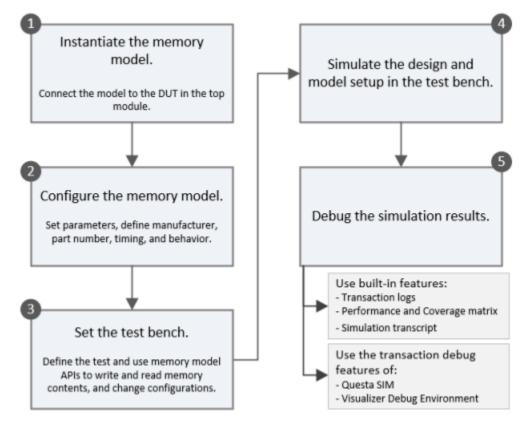

| 6.7 QUESTA VERIFICATION IP               | 124 |

| 6.7.1 Overview                           | 124 |

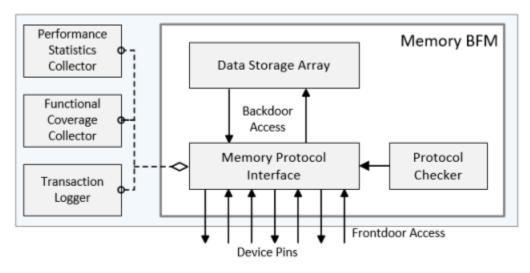

| 6.7.2 Memory Model Components            | 125 |

| 6.7.3 Configurations                     | 126 |

| Chapter 7: Conclusions and Future Work   | 129 |

| 7.1 Conclusion                           | 129 |

| 7.2 Future Work                          | 129 |

| REFERENCES                               | 130 |

# List of figures

| Figure 1: DRAM Architecture.                                                           | 12 |

|----------------------------------------------------------------------------------------|----|

| Figure 2 : Bandwidth Evolution of DRAM Standards.                                      | 14 |

| Figure 3: Comparison of DDR4 and DDR5 Key Parameters                                   | 16 |

| Figure 4: Big Picture of Design.                                                       |    |

| Figure 5 : Inputs and Outputs of Top Module                                            | 20 |

| Figure 6: Address Mapping.                                                             | 21 |

| Figure 7: Block Diagram of Top Module.                                                 | 23 |

| Figure 8: Block Diagram of Command Decoder                                             | 23 |

| Figure 9: Block Diagram of Command_Address_FIFO                                        | 28 |

| Figure 10: Block Diagram of Write_Data_FIFO                                            |    |

| Figure 11: Block Diagram of Counters.                                                  |    |

| Figure 12: Block Diagram of Command_FSM                                                | 34 |

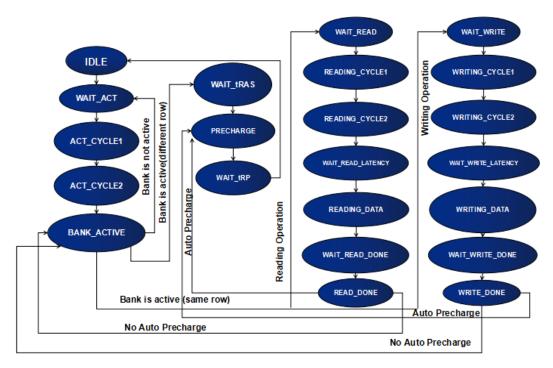

| Figure 13: Simplified State Diagram, JEDEC Reference                                   |    |

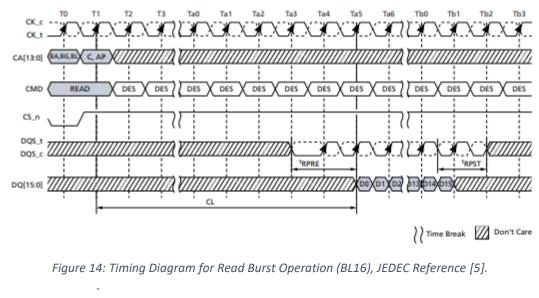

| Figure 14: Timing Diagram for Read Burst Operation (BL16), JEDEC Reference.            |    |

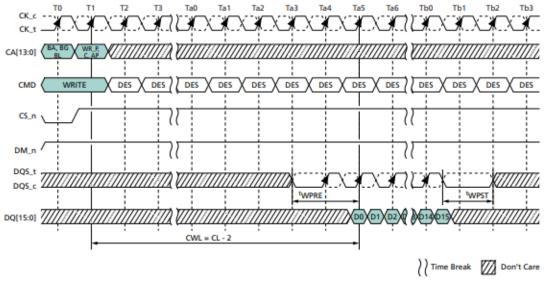

| Figure 15: Timing Diagram for Write Burst Operation (BL16), JEDEC Reference.           |    |

| Figure 16: Command_FSM                                                                 |    |

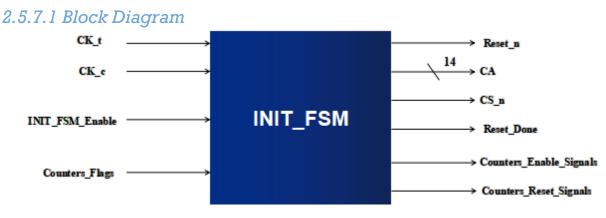

| Figure 17: Block Diagram of Initialization_FSM                                         | 46 |

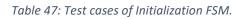

| Figure 18: Reset and Initialization Sequence at Power-on Ramping, JEDEC Reference      |    |

| Figure 19: Initialization _FSM                                                         |    |

| Figure 20: Block Diagram of Self-Refresh _FSM                                          | 51 |

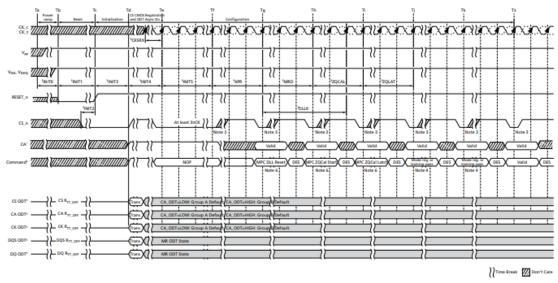

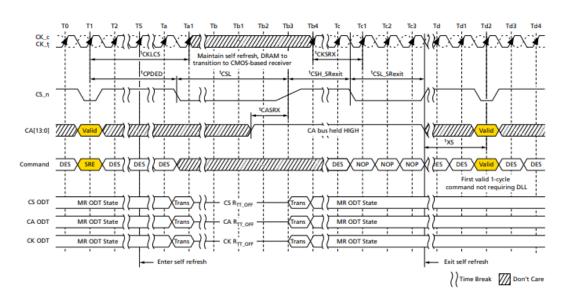

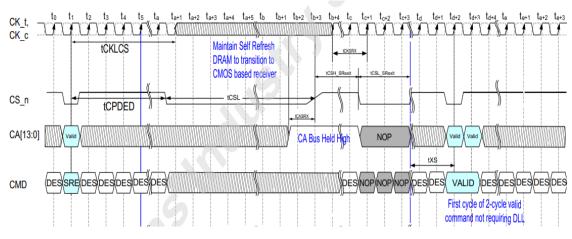

| Figure 21: Self-Refresh Entry/Exit Timing with One-Cycle Exit Command, JEDEC Reference |    |

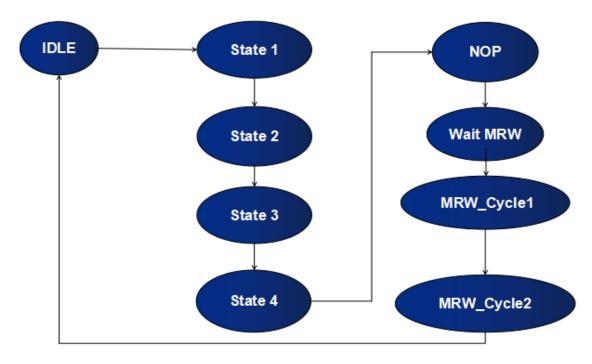

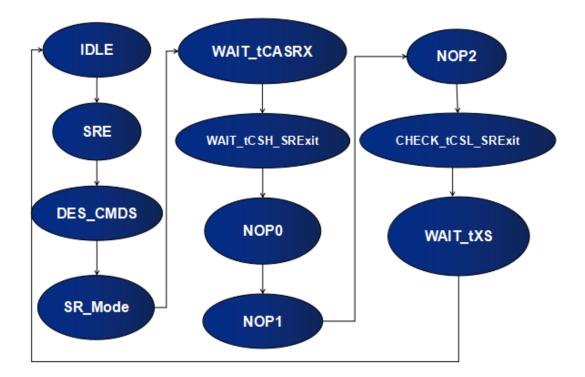

| Figure 22: Self-Refresh _FSM                                                           | 53 |

| Figure 23: Clock Generator isn't synthesizable                                         |    |

| Figure 24: Problem of ambiguous clock triggering                                       |    |

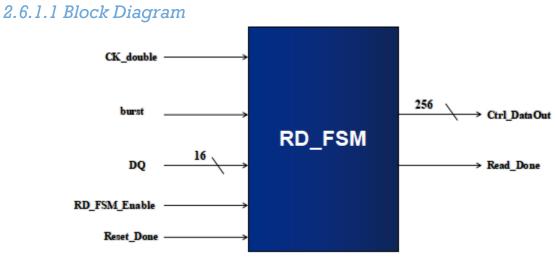

| Figure 25: Block Diagram of Read_FSM                                                   |    |

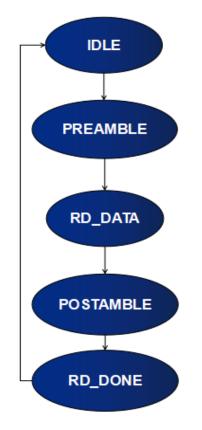

| Figure 26: Read_FSM                                                                    | 58 |

| Figure 27: Block Diagram of Write_FSM                                                  | 60 |

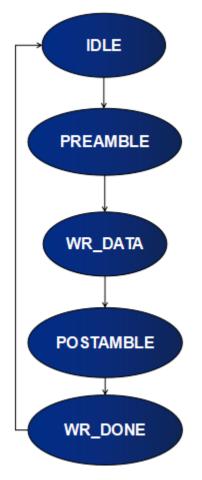

| Figure 28: Write_FSM                                                                   | 61 |

| Figure 29: Multiple Driven Problem                                                     | 63 |

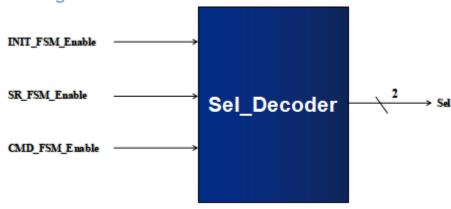

| Figure 30: Block Diagram of Selection_Decoder                                          | 64 |

| Figure 31: Some Problems of Synthesis.                                                 | 66 |

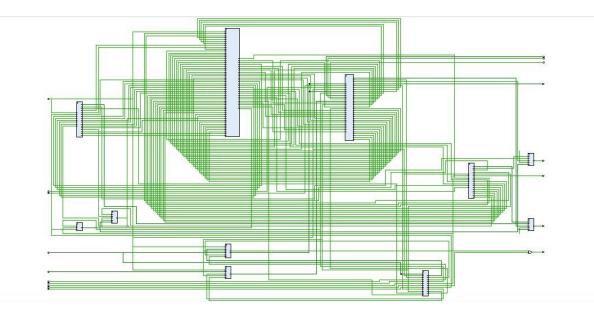

| Figure 32: Schematic from Synthesis Tool (Vivado).                                     | 66 |

| Figure 33: Types of Functional Verification                                            | 68 |

| Figure 34:Architecture of Cocotb                                                       | 70 |

| Figure 35: An example of the coverage tree structure                                   | 72 |

| Figure 36: Block Level Verification Environment.                                       | 76 |

| Figure 37: Command decoder coverage section written in python.                         | 77 |

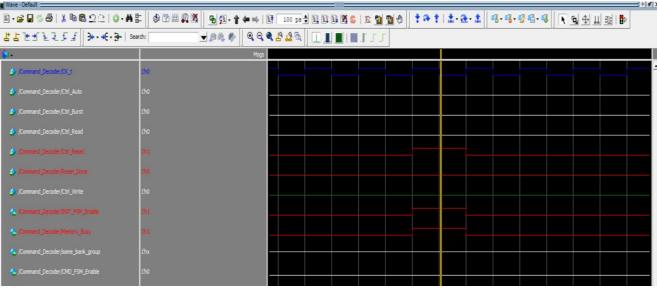

| Figure 38: Initialization FSM Enable is asserted high for only one cycle.              | 81 |

| Figure 39: Initialization FSM Enable after modification                                | 82 |

| Figure 40: Command Decoder Test Summary from Questasim.                                | 82 |

| Figure 41: Command decoder Functional Coverage XML Report                              |    |

| Figure 42: Command decoder Functional Coverage from Coverage Viewer.                   | 83 |

| Figure 43: Command decoder Code Coverage Summary from Questasim.                       | 84 |

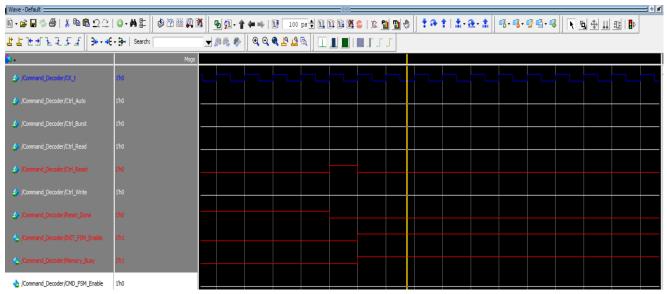

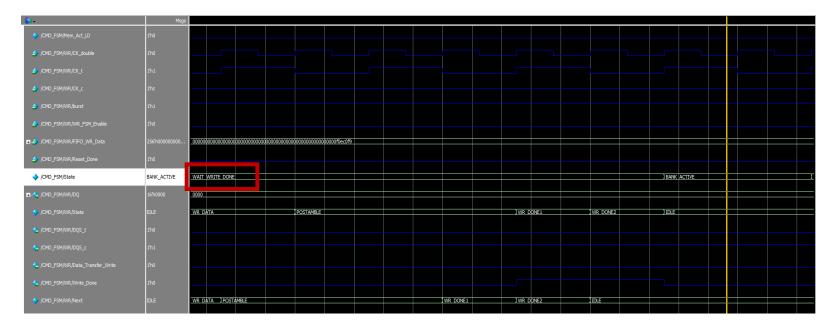

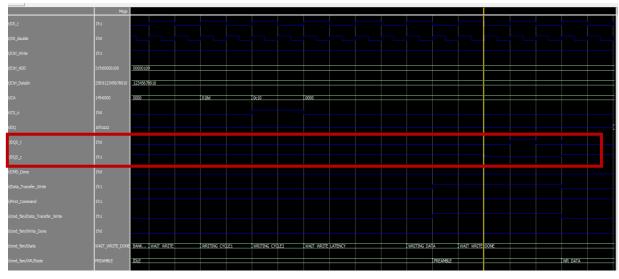

| Figure 44: Single write operation stuck at wait write done state           | 94  |

|----------------------------------------------------------------------------|-----|

| Figure 45: Single write operation after modifying CMD FSM                  | 95  |

| Figure 46: DQS, DQT preambles aren't working properly                      | 96  |

| Figure 47: DQS, DQT preambles are working properly after modification      | 96  |

| Figure 48: CMD FSM gets stuck at wait_tRP state                            | 97  |

| Figure 49: CMD FSM works properly after modification.                      |     |

| Figure 50: Command FSM Functional Coverage from Coverage Viewer            | 98  |

| Figure 51: Command FSM Code Coverage Summary from Questasim.               | 98  |

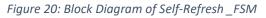

| Figure 52: Self_Refresh sequence as specified in JESD79-5                  |     |

| Figure 53: implemented Self_Refresh waveform.                              | 100 |

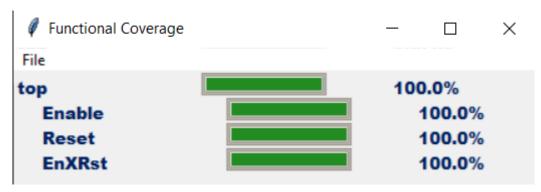

| Figure 54: Self-Refresh FSM Functional Coverage XML Report                 | 100 |

| Figure 55: Self-Refresh FSM Functional Coverage from Coverage Viewer       | 101 |

| Figure 56: Self-Refresh FSM Code Coverage Summary from Questasim.          | 101 |

| Figure 57: Initialization sequence as specified in JESD79-5                |     |

| Figure 58: implemented initialization waveform                             | 103 |

| Figure 59: Initialization FSM Functional Coverage XML Report               | 103 |

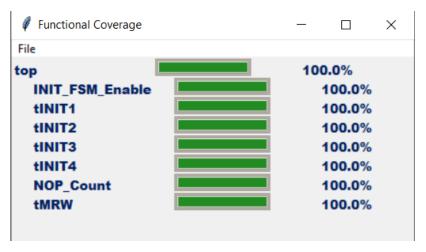

| Figure 60: Initialization FSM Functional Coverage from Coverage Viewer.    | 103 |

| Figure 61: Initialization FSM Code Coverage Summary from Questasim.        | 104 |

| Figure 62: Counter Flag is asserted High for only one Clock Cycle.         | 105 |

| Figure 63: Counters Functional Coverage XML Report                         | 105 |

| Figure 64: Counters Functional Coverage from Coverage Viewer               | 106 |

| Figure 65: Counters Code Coverage Summary from Questasim.                  | 106 |

| Figure 66: Counters Test Summary from Questasim                            | 106 |

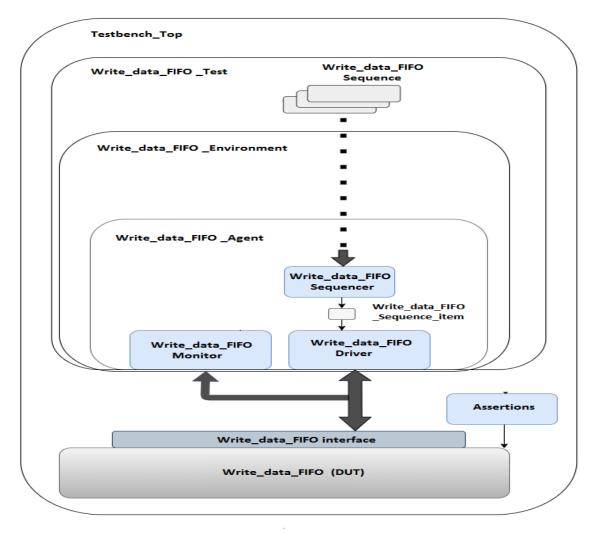

| Figure 67: UVM environment for WR_Data_FIFO block                          |     |

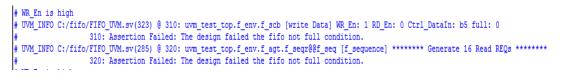

| Figure 68: 1st example of error from simulation                            | 109 |

| Figure 69: 2nd example of error from simulation                            | 109 |

| Figure 70: UVM Report Summary and Coverage                                 | 109 |

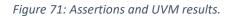

| Figure 71: Assertions and UVM results                                      | 110 |

| Figure 72: The assertions coverage.                                        | 110 |

| Figure 73: Result of errors from COCOTB                                    | 111 |

| Figure 74: COCOTB verification results                                     | 112 |

| Figure 75: COCOTB Functional coverage report                               | 112 |

| Figure 76: COCOTB Code coverage report                                     | 113 |

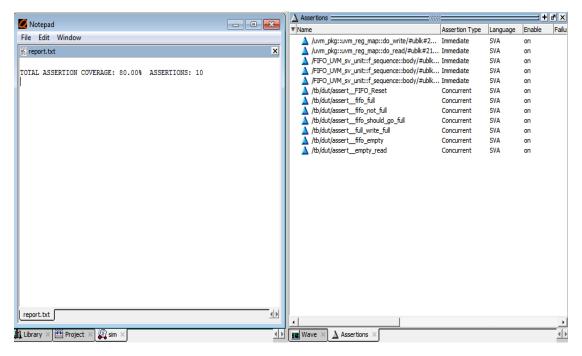

| Figure 77: Constrained-random test progress over time vs. directed testing | 114 |

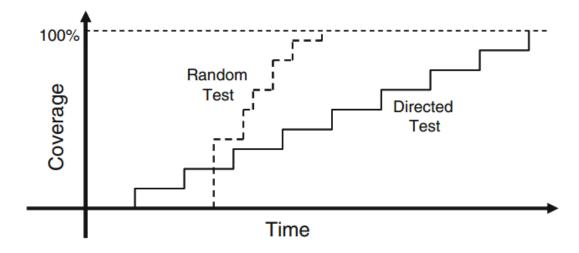

| Figure 78: Programming languages Complexity.                               | 115 |

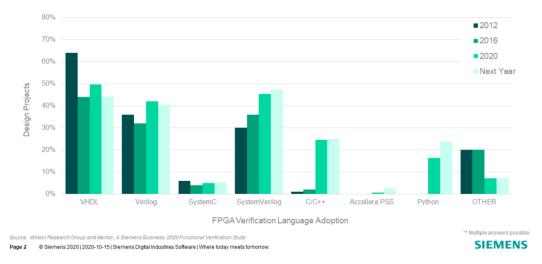

| Figure 79: FPGA verification language adoption next twelve months          | 116 |

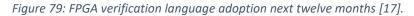

| Figure 80: ASIC/IC verification language adoption next twelve months       | 116 |

| Figure 81 : Verification Environment of Top-Level Verification             | 117 |

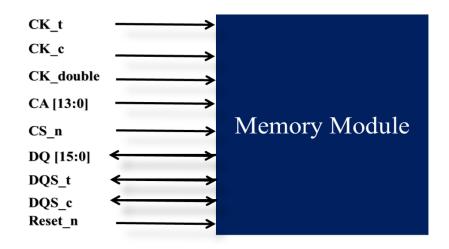

| Figure 82: Block Diagram of Memory Module                                  | 118 |

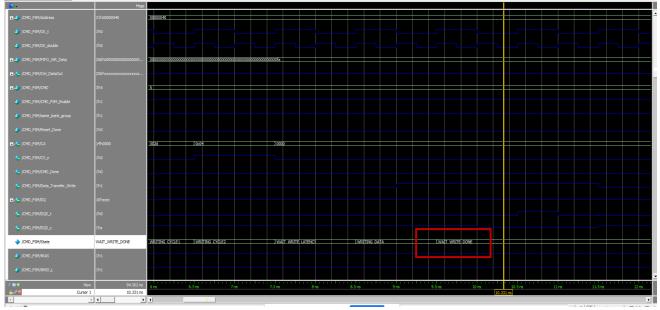

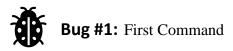

| Figure 83:Top Module is stuck at WAIT_ACT state                            | 119 |

| Figure 84: Read words with length less than burst length                   | 120 |

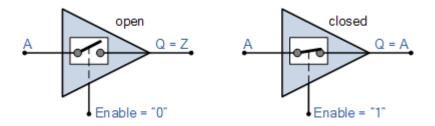

| Figure 85: Tri-state Buffer                                                | 121 |

| Figure 86:Functional Coverage Report of Top Level                          | 121 |

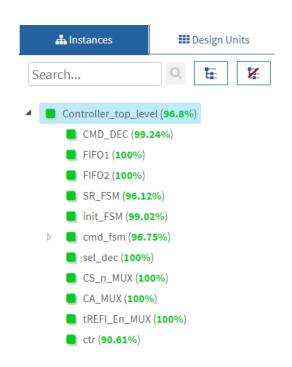

| Figure 87:Code Coverage Report of Top Level                                | 122 |

| Figure 88:Waveform of Initialization Sequence from Top Level | 122 |

|--------------------------------------------------------------|-----|

| Figure 89:Waveform of Self-Refresh Sequence from Top Level   | 123 |

| Figure 90: Waveform of Single Read after Write               | 123 |

| Figure 91: Waveform of Multiple Read after Multiple Write    | 123 |

| Figure 92: Questa Memory Model Flow                          | 124 |

| Figure 93:Memory Model Components                            | 125 |

| Figure 94: Test bench using QVIP Configurator                |     |

| Figure 95 :Memory Model Configurations                       |     |

|                                                              |     |

# List of tables

| Table 1: Inputs of Top Module                                   |      |

|-----------------------------------------------------------------|------|

| Table 2: Outputs of Top Module                                  | .21  |

| Table 3: Inputs of Command Decoder                              | .23  |

| Table 4: Outputs of Command Decoder                             |      |

| Table 5: Description of Processor Commands                      |      |

| Table 6: Decoding of Processor Commands                         | . 25 |

| Table 7: Description of Enable Signals of Finite State Machines | .26  |

| Table 8: Description of Enable Signals of FIFOs                 | . 27 |

| Table 9: Inputs of Command_Address_FIFO                         | . 28 |

| Table 10: Outputs of Command_Address_FIFO                       | . 28 |

| Table 11: Inputs of Write_Data_FIFO                             | . 29 |

| Table 12: Outputs of Write_Data_FIFO                            | . 30 |

| Table 13: Initialization Timing Parameters                      | .31  |

| Table 14: Activate Timing Parameters                            | . 32 |

| Table 15: Precharge Timing Parameters                           | . 32 |

| Table 16: Reading Timing Parameters                             |      |

| Table 17: Writing Timing Parameters                             | . 32 |

| Table 18: Self-Refresh Timing Parameters                        |      |

| Table 19: Inputs of Command_FSM                                 |      |

| Table 20: Outputs of Command_FSM                                |      |

| Table 21: Scenarios of Back-to-Back Operations                  |      |

| Table 22:Storage of Activate Rows                               |      |

| Table 23: Description of each state in Command_FSM              |      |

| Table 24: Outputs of each state in Command_FSM                  |      |

| Table 25: Inputs of Initialization_FSM                          |      |

| Table 26: Outputs of Initialization_FSM                         |      |

| Table 27: Description of each state in Initialization_FSM       |      |

| Table 28: Outputs of each state in Initialization_FSM           |      |

| Table 29: Inputs of Self Refresh_FSM                            |      |

| Table 30: Outputs of Self Refresh_FSM                           |      |

| Table 31: Description of each state in Self Refresh_FSM         |      |

| Table 32: Outputs of each state in Self Refresh_FSM             |      |

| Table 33: Inputs of Read_FSM                                    |      |

| Table 34: Outputs of Read_FSM                                   |      |

| Table 35: Description of each state in Read_FSM                 |      |

| Table 36: Outputs of each state in Read_FSM                     |      |

| Table 37: Inputs of Write_FSM                                   |      |

| Table 38: Outputs of Write_FSM                                  |      |

| Table 39: Description of each state in Write_FSM                |      |

| Table 40: Outputs of each state in Write_FSM                    |      |

| Table 41: Inputs of Selection Decoder                           |      |

| Table 42: Outputs of Selection Decoder                          |      |

| Table 43: Operation of Selection Decoder                        | .64  |

| Table 44: Test cases of command decoder          | 77  |

|--------------------------------------------------|-----|

| Table 45: Test cases of command FSM.             | 85  |

| Table 46: Test cases of Self_Refresh FSM         | 99  |

| Table 47: Test cases of Initialization FSM.      |     |

| Table 48: Test cases of counters                 | 104 |

| Table 49: Description of Memory Model Components | 125 |

## List of Abbreviation

SDRAM: Synchronous Dynamic Random Access Memory **DDRx**: Double Data rate xth generation SoC: System on Chip MPSoC: Multi-Processor System on Chip **DIMM:** Dual Inline Memory Module ACT: Activate Command **PRE**: Precharge Command RD: Read Command RDA: Read Command with Auto-Precharge **WR**: Write Command WRA: Write Command with Auto-Precharge NOP: No Operation Command PREpb: Precharge bank Command PREsb: Precharge same bank Command PREab: Precharge all banks Command REFsb: same-bank Refresh **CRC**: Cyclic Redundancy Check **MP**SM: Maximum Power Saving Mode Cocotb: Co-routine Co-simulation test-bench UVM: Universal Verification Methodology FIFO: First-In First-Out FSM: Finite State Machine HDL: Hardware Description Language **RTL**: Register Transfer Level IC: Integrated Circuit **FPGA**: Field Programmable Gate Array **EDA**: Electronic Design Automation **DUT**: Design Under Test **GUI**: Graphical User Interface **VPI**: Verilog Procedural Interface VHDLPI: VHDL Procedural Interface **API**: Application Programming Interface **IP**: Intellectual Property QVIP: Questa Verification IP

## **Chapter 1: Introduction**

#### **1.1 MOTIVATION**

Currently, we see a strong need to memory-dominated Applications such as Big Data, IoT, Cloud-Data Centers, Machine Learning etc...., Thus Dynamic Random-Access Memories (DRAMs) play a large role in compute platforms. Over the last years, the number of DRAM standards specified by the JEDEC Solid State Technology Association has been growing rapidly. The most recent DRAM standard is DDR5, which was released in mid-2020, because of the large number of new features, system designers are either challenged to adopt the new standard or they can move on with well-established standards like DDR4.If DDR5 is a potential candidate for a specific application, a further challenge is the configuration of the DDR5 subsystem, which is the configuration of the DDR5 subsystem, which features a lot of parameter choices. Fast and accurate simulation models are mandatory to explore the new features and compare different configurations.

#### **1.2 DRAM BACKGROUND AND DDR5**

In this section we introduce the basic terminology of DRAM devices and their controllers and give an overview on the new features of the DDR5 standard.

#### 1.2.1 DRAM Basics

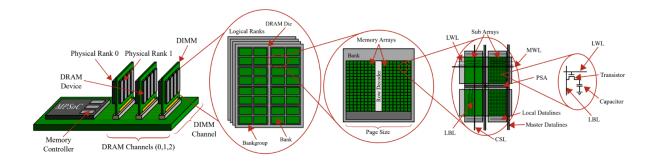

As shown in Figure 1, DRAM can be organized in a multi-hierarchical fashion of DIMMs, channels, physical ranks, devices, logical ranks, bank groups, banks, memory arrays, sub arrays, rows, and columns. Several DRAM channels can be connected to the Multi-Processor System on Chip (MPSoC). These channels are completely in-dependent of each other and have separate command/address and data buses. A channel can be composed of one or multiple physical ranks, which are sharing the data and command/address bus. A Dual Inline Memory Module (DIMM) is a small PCB that accommodates several DRAM devices, which work completely synchronously. One single device is called ×161 if it has an I/O data width of 16 bit. A DIMM is assembled for

instance out of four  $\times 16$  devices in order to have a total I/O data width n = 64 bit (called  $\times 64$ ). While the I/O data width is usually very limited, inside the DRAM a lot of data can be fetched or stored in parallel. However, the time between consecutive internal data accesses is very long due to the optimization for storage density, while the interface can be operated on much higher frequencies. To align this mismatch DRAM uses a so-called prefetching technique. For read large chunks of data are concurrently fetched to the interface and then transferred in one burst to the relpronunciation: by-sixteen quester, for a write the process is reversed. In addition, data is transferred at the doubled interface frequency (double data rate, short DDR). Current devices such as DDR4 use an 8n prefetch architecture, where n is the I/O data width, 8 the Burst Length (BL) and 8n the number of bits for an internal data transfer. That means with each DRAM access the total amount of data received or delivered is  $BL \cdot n = 8 \cdot 64$  bit = 512 bit = 64 B, which is the usual cache line size in today's computing systems. In combination with interface frequencies up to 1600 MHz or pin transfer rates up to 3200 MT/s (mega transfers per second) DDR4 reaches a maximum bandwidth of 25.6 GB/s per channel. Each device itself can consist of several 3D-stacked logical ranks, which can form several bank groups that include several banks. The concept of bank groups was introduced with DDR5 and DDR4 in order to reduce the bank switching times to support a seamless burst behavior at high data rates and therefore a high bandwidth. All banks in a whole channel can be used concurrently (so called bank parallelism). However, there are some constraints due to the shared buses. Each bank usually consists of 212 to 218 rows, and each row can usually store 512B to 2KB of data in its columns. A memory controller is composed of a front end and a back end. The front end performs arbitration and scheduling of incoming read and write requests, whereas the task of the back end is to translate these incoming requests into a sequence of DRAM commands, which have to be orchestrated with respect to the current state of the device. To access data in a row of a certain bank, an activate (ACT) command must be issued by the controller before any column access, i.e., read (RD) or write (WR) commands, can be executed. The ACT command opens an entire row of the memory array, which is transferred into the bank's row buffer [2]. It acts like a small cache that stores the most recently accessed row of the bank. The latency of a memory access to a bank largely varies depending on the state of this row buffer. If a memory access targets the same row as the currently cached row in the buffer (called row hit), it results in a low latency and low energy memory access.

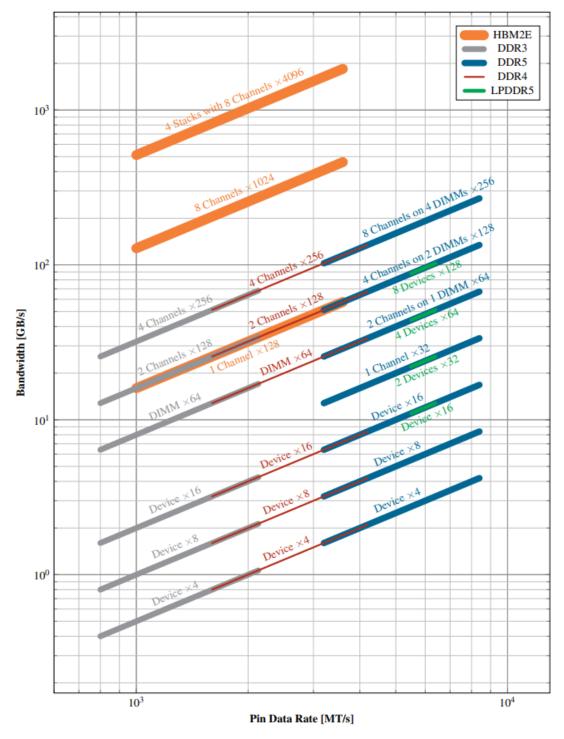

Figure 2 : Bandwidth Evolution of DRAM Standards [1].

Whereas, if a memory access targets a different row as the current row in the buffer (called row miss), it results in a higher latency and energy consumption. If a certain row in a bank is active it must first be precharged (PRE) before another row can be activated. In addition to the normal RD and WR commands, there exist read and write commands with an integrated auto-precharge (RDA,

WRA). If auto-precharge is selected, the row being accessed will be precharged automatically at the end of the read or write access. Because a DRAM cell uses a capacitor with leakage effects for data storage, it usually has to be refreshed every 64ms to retain the data stored in it. Modern DRAMs are equipped with an all-bank refresh (REFab) command to perform this operation automatically on all banks of a rank in parallel. However, a prerequisite is that all banks are in a precharged state. This can be achieved by issuing a special all-bank precharge (PREab) command in advance. In addition to the commands, each DRAM standard defines a set of timing dependencies, which are temporal constraints that must be satisfied between issued commands. For example, between two ACT commands to the same bank the timing dependency tRC (row cycle time) must be satisfied. Timing dependencies can also exist on other hierarchies of the DRAM, e.g., between commands to the same bank group, to the same logical/physical rank or to different logical/physical ranks. The selection of a DRAM subsystem usually has three main dimensions: bandwidth, latency, and capacity. Bandwidth is the amount of data that can be transferred between DRAM and a computational unit within a given time. As shown in Figure 2, the maximum theoretical DRAM bandwidth is limited to the number of data pins times the interface pin data rate (number of accesses per time per pin). Latency is the time that it takes to complete an access. In fact, latency helps bandwidth, but not vice versa [4]. For instance, lower DRAM latency results in more accesses per time, and therefore higher bandwidth, whereas increasing the number of data pins increases the bandwidth without decreasing latency. In realistic scenarios, the full theoretical bandwidth is never reached due to many timing dependencies, interference between different requests, and refresh. The actual achieved bandwidth for a specific application is called sustainable bandwidth.

#### 1.2.2 DDR5 Standard

With the development of a new DRAM standard generation there are always several key parameters that should be enhanced, e.g., bandwidth, power consumption, and device capacity. Figure 3 shows a comparison between key parameters of the new DDR5 standard and its predecessor DDR4. In the following we will also describe the most important differences in more detail. For a higher bandwidth DDR5 raises the maximum pin data rate to 8400 MT/s compared to 3200 MT/s for DDR4. Because the frequency of internal data accesses stays more or less the same as a result of the capacity- and cost optimized architecture, the prefetch was incremented from 8n to 16n. When using the same 64-bit-wide data bus for one channel as all previous DDR generations, this would result in 128 B of transferred data per access. However, since the usual cache line size of modern processors is only 64 B, the data bus of each DDR5 DIMM is split up into two independent channels of 32-bit width. That way only 64 B of data are transferred per access. Theoretical transfer rates then reach a maximum of 33.6 GB/s per channel and 67.2 GB/s per DIMM compared to 25.6 GB/s per channel/DIMM for DDR4, as shown in Figure 2. At the same time supply voltages are reduced from 1.2 V to 1.1 V for an improved power consumption. The maximum number of banks per device increases from 16 to 32 distributed over 8 instead of 4 bank groups, the total capacity of a single device from 16 Gb to 64 Gb. In addition, up to 16 instead of 8 devices can now be stacked in a three-dimensional fashion (logical ranks)<sup>3</sup>. This enables stack capacities of up to 512 Gb (max.  $16 \times 32$  Gb or  $8 \times 64$  Gb because of limited address bits). One

problem that always arises with higher device capacities is the increased refresh overhead, because each cell still has to be refreshed approximately every 64 ms, as a consequence, either the controller has to issue refresh commands more frequently or the individual refresh cycles take a longer time. Since all banks of a rank cannot be accessed during an all-bank refresh, it can lead to significant performance drops. To overcome this problem, DDR5 introduces same-bank refresh (REFsb) and associated same-bank precharge (PREsb) commands as an alternative to all-bank refresh (REFab) and all-bank precharge (PREab) commands. When issuing them, only one bank in each bank group of the target rank is refreshed and inaccessible, while all other banks can still process incoming read and write requests. Most modern DRAM controllers use advanced reordering techniques for an improved performance so they can try to hide the same-bank refresh by sending requests to other banks in the meantime. Finally, DDR5 devices implement an on-die error correction to improve the data integrity[2].

| ITEMS             | DDR4                | DDR5                        |

|-------------------|---------------------|-----------------------------|

| Frequency         | 1600~3200Mbps       | 3200~8400Mbps               |

| Density           | 2Gb, 4Gb, 8Gb, 16Gb | 8Gb, 16Gb, 24Gb, 32Gb, 64Gb |

| On die ECC        | Νο                  | Yes                         |

| Bank              | 16banks             | 32banks                     |

| VDD/VDDQ          | 1.2V                | 1.1V                        |

| VPP               | 2.5V 1.8V           |                             |

| BL                | 8                   | 16                          |

| DFE               | No                  | Yes                         |

| Same bank refresh | No                  | Yes                         |

Figure 3: Comparison of DDR4 and DDR5 Key Parameters [3].

#### **1.3 HIGH COMPLEXITY AND THE NEED FOR VERIFICATION**

With advanced and complex features, there is a need for meticulous verification. Memories have a vast set of configurations that allow them to operate at various data rates with different densities. Further, these can be combined with a vast set of features such as Self-Refresh, Auto Refresh, Cyclic Redundancy Check (CRC), Post Package Repair, Maximum Power Saving Mode (MPSM), training across different settings of latencies and speeds. The permutation and combinations of these variables can grow exponentially across different memory vendors as each of these memory

vendors offer 100s of part numbers. As you can imagine, it can easily become a daunting experience for verification engineers to verify a memory subsystem.

DDR5 DIMMs adds more challenges. For example, in order to achieve higher power efficiency, voltage is reduced from 1.2V to 1.1V which brings additional complexity for DIMM vendors around noise immunity. Higher speeds raise data integrity concerns which need precise training results. This creates the need for careful verification, as modeling of real-world scenarios and visualization of those scenarios going into wire level toggling would consume a lot of time.

Measuring verification progress through functional coverage is equally important as the verification of design features. Also, performance analysis is extremely important for memories. These add a few extra cycles in the verification flow.

#### **1.4 THESIS SCOPE**

1.Design of DDR5 SDRAM Memory Controller based on JEDEC79-5 Standard.

2.Verification of DDR5 SDRAM Memory Controller using Python Language especially CoCotb library (new trend method in verification).

#### **1.5 THESIS ORGANIZATION**

The structure of the thesis is as follows:

- Chapter 2: This Chapter discusses the design of DDR5 SDRAM Memory Controller.

- Chapter 3: This Chapter presents an introduction to Cocotb and discusses The Verification Methodology.

- Chapter 4: This chapter outlines the results of Block level verification phase.

- Chapter 5: A Comparison between UVM Verification and A Cocotb Verification is discussed in this chapter.

- Chapter 6: This chapter outlines the results of Top-level verification phase.

- Chapter 7: The chapter consists of the conclusions and details possible future work

## **Chapter 2: Design**

#### **2.1 OVERVIEW**

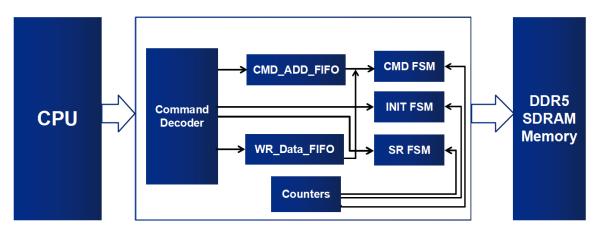

In this chapter, we will discuss design of **DDR5 SDRAM Controller**. Our design will interface with CPU and DDR5 SDRAM Memory as shown in Figure 4:

Figure 4: Big Picture of Design.

to interface with CPU, we followed **Native Interface** and to interface with DDR5 SDRAM Memory we followed **JEDEC79-5 Standard**. For DDR5 SDRAM Memory, we chose **x16** Configuration with **3.2GHZ** input clock frequency. This choice will affect the values of timing parameters as we will illustrate. Not all the features of DDR5 SDRAM Memory in JEDEC79-5 Standard are scoped in our project. To choose features that will be implemented in our design, we divided features into three sections:

#### 2.1.1 Basic Features

- Initialization

- Activation

- > Precharge

- ➢ Reading

- ➤ Writing

- Auto Precharge

- > Burst

- Self-Refreshing

Mode Register Operations

#### 2.1.2 Optional Features

- On-Die ECC (Check Memory Error)

- DDR5 ECC Transparency and Error Scrub

- CRC (Check Bus Error)

- Write Pattern Command

- > Refreshing

- Power Down Mode

#### 2.1.3 Excluded Features

All modes related to testing, training modes such as ZQ Calibration, Read Training, Change Clock Frequency, etc.

#### **2.2 SCOPE OF OUR DESIGN**

As a first step in design, we started our design by **basic features** mentioned above in section 2.1.1 and after we verify these operations, we will extend our project based on available time with other optional features of DDR5. There are also some modes we mentioned in section 2.1.3 we excluded them as there are related if we completed our design as a product and we need to test it in hardware so we excluded them from our design as we will not reach in our project to fabrication. To implement basic features these are the memory commands that will be used:

- Activate (ACT)

- Precharge (PREpb)

- ➢ Read (RD)

- Read w/Auto Precharge (RDA)

- ➢ Write (WR)

- Write w/Auto Precharge (WRA)

- Mode Register Write (MRW)

- Self\_Refresh Entry (SRE)

- > NOP

➢ Deselect (DES)

#### 2.3 INPUTS AND OUTPUTS OF TOP MODULE

After we chose features that will be implemented, we could determine inputs and outputs of our design from Native interface and JEDEC79-5 standard as shown in Figure 5:

*Figure 5 : Inputs and Outputs of Top Module.*

The description of each input is shown in Table 1, and also description of each output is shown in Table 2:

| Table | 1: | Inputs | of | Тор | Module | [4] |

|-------|----|--------|----|-----|--------|-----|

|-------|----|--------|----|-----|--------|-----|

| Signal     | Description                                                                                                                                                 |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CK_t, CK_c | Differential clock of DDR5 SDRAM, all address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c. |  |  |

| Ctrl_Reset | Control signal from CPU to controller to issue the initialization sequence to memory. It's active high reset                                                |  |  |

| Ctrl_Read  | Read request (active high).                                                                                                                                 |  |  |

| Ctrl_Write | Write request (active high).                                                                                                                                |  |  |

| Ctrl_Burst | When 1 defines alternate read/write burst mode (BC8) and when 0 defines default BL16 mode.                                                                  |  |  |

| Ctrl_Auto          | When asserted high along with Ctrl_Read or Ctrl_Write, causes the command to be issued as read with auto-precharge and write with auto-precharge, respectively.                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ctrl_ADD[30:0]     | Address that data will be read from memory or written in memory.                                                                                                                                    |

| Ctrl_DataIn[255:0] | Data that will be written in memory during writing operation.                                                                                                                                       |

| CK_double          | Clock that has double frequency of SDRAM clock, DQS signals will be<br>generated with positive edge of this clock, also data from memory will<br>be sampled also on the positive edge of this clock |

#### Table 2: Outputs of Top Module [5]

| Signal              | Description                                                                                                                                                                                               |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset_n             | Active low asynchronous reset: reset is active when reset_n is low, and inactive when reset_n is high. reset_n must be high during normal operation and takes some values during initialization sequence. |

| CS_n                | Chip Select: all commands are masked when CS_n is registered high.<br>For one cycle commands (CS_n=0), for two cycle commands (CS_n=0<br>for first cycle, CS_n=1 for second cycle).                       |

| CA[13:0]            | Command/Address Inputs: CA signals provide the command and address inputs according to the command truth table in JEDEC79-5 standard section 4.1 Table 241.                                               |

| DQ[15:0]            | Data Input/Output: Bi-directional data bus                                                                                                                                                                |

| DQS_t,DQS_c         | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. DDR5 SDRAM supports differential data strobe only and does not support single-ended.      |

| Ctrl_DataOut[255:0] | Data will be delivered from memory to CPU.                                                                                                                                                                |

| Ctrl_Busy           | Control signal is sent to CPU to tell it to stop sending reading or<br>writing requests as FIFO of commands became full or when there is<br>initialization or self refresh for memory.                    |

## ♦ Assumptions & Notes

1. We assume that Physical address that comes from CPU (Ctrl\_ADD) will be 31 bit and address mapping will be one to one mapping as shown in Figure 6:

|    | Row | Column | Bank | В | ank Group |

|----|-----|--------|------|---|-----------|

| 30 | 1   | 3      | 4    | 2 | 0         |

Figure 6: Address Mapping [5].

2. According to Native Interface data bus (Ctrl\_DataIn, Ctrl\_DataOut) is eight times the width of the SDRAM device data bus (DQ) but for simplicity we made data bus (Ctrl\_DataIn, Ctrl\_DataOut) is 16 times the width of the SDRAM device data bus (DQ) as default BL.

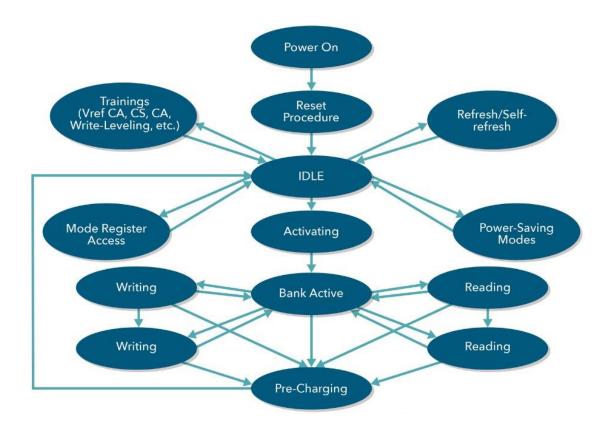

#### **2.4 OPERATION OF CONTROLLER**

To know blocks and detailed block diagram of our design, we could get this by defining operation of our design. We can summarize operation of memory controller in five points as follow [7]:

1. Memory controller is responsible for **queuing** requests from CPU like read and write requests and also responsible for scheduling these requests to choose which request will be executed.

2. It's responsible for **decoding** these requests into **memory commands** and issue these commands to memory keeping **timing constraints** between these commands according to period of clock of SDRAM.

3. In case of read request, it's responsible for getting data from memory to CPU and vice versa in write request.

4. As we talk about dynamic memory so it will need refresh every certain time, memory controller is responsible for issuing **self-refresh sequence** to memory.

5. Memory controller is also responsible for issuing **initialization sequence** to memory.

From red highlighted keywords we can know which blocks that we need in our design to achieve operation of DDR5 SDRAM Controller:

Queuing: Command\_Address\_FIFO, Write\_Data\_FIFO

**Decoding:** Command\_Decoder

Memory Commands: Command\_FSM

**Timing Constraints:** Counters

Self-Refresh Sequence: Self Refresh\_FSM

**Initialization Sequence:** Initialization\_FSM

So, block diagram of our design will be as shown in Figure 7 [8]:

Figure 7: Block Diagram of Top Module.

#### **2.5 DESIGN IN DETAIL**

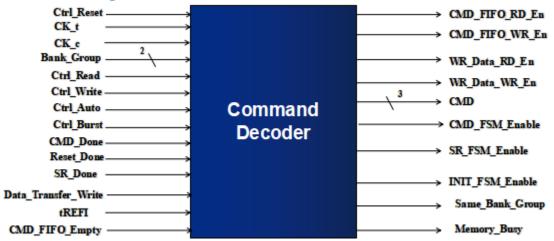

#### 2.5.1. Command\_Decoder

#### 2.5.1.1. Block Diagram

Figure 8: Block Diagram of Command Decoder.

#### 2.5.1.2. List of Inputs and Outputs

Table 3: Inputs of Command Decoder

| Signal          | Description                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ctrl_Reset      | Control signal from CPU to controller to issue the initialization sequence to the SDRAM. It's active high reset                                  |

| CK_t, CK_c      | Differential clock of DDR5 SDRAM, all address and control input signals<br>are sampled on the crossing of the positive edge of CK_t and negative |

| Bank_Group[1:0] | edge of CK_c<br>Bank group address, it is Ctrl_ADD[1:0]                                                                                          |

| Ctrl_Read       | Read request (active high)                                                                                                                       |

| Ctrl_Write      | Write request (active high)                                                                                                                      |

| Ctrl_Burst          | When 1 defines alternate read/write burst mode (BC8 ) and when 0 defines default BL16 mode                                                                     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ctrl_Auto           | When asserted high along with Ctrl_Read or Ctrl_Write, causes the command to be issued as read with auto-precharge and write with auto-precharge, respectively |

| CMD_Done            | When 1 defines that command has been executed                                                                                                                  |

| Reset_Done          | When 1 defines that initialization sequence has been executed                                                                                                  |

| SR_Done             | When 1 defines that self-refresh sequence has been executed                                                                                                    |

| Data_Transfer_Write | Input signal from command FSM, when 1 defines that we need to set<br>WR_Data_RD_En high to write data from WR_Data_FIFO to memory                              |

| tREFI               | Flag signal of self-refresh counter to issue the self-refresh sequence to memory                                                                               |

| CMD_FIFO_Empty      | Empty flag of Command_Address FIFO                                                                                                                             |

#### Table 4: Outputs of Command Decoder

| Signal          | Description                                                    |

|-----------------|----------------------------------------------------------------|

| CMD_FIFO_RD_En  | Active high read enable of Command_Address_FIFO                |

| CMD_FIFO_WR_En  | Active high write enable of Command_Address_FIFO               |

| WR_Data_RD_En   | Active high read enable of Write_Data_FIFO                     |

| WR_Data_WR_En   | Active high write enable of Write_Data_FIFO                    |

| CMD[2:0]        | Defines type of command (read/write) that will be executed     |

|                 | by Command_FSM.                                                |

| CMD_FSM_Enable  | Active high enable of Command_FSM                              |

| INIT_FSM_Enable | Active high enable of Initialization_FSM                       |

| SR_FSM_Enable   | Active high enable of Self Refresh_FSM                         |

| Same_Bank_Group | When 1 defines that bank group address of current command      |

| Same_bank_Group | is the same as address of previous command                     |

|                 | When 1 indicates that memory in initialization or self-refresh |

| Memory_Busy     | sequence. When 0 indicates that memory in normal operation     |

|                 | (reading or writing)                                           |

#### 2.5.1.3 Operation

Command Decoder is the brain of our design, we can say it's the controller of our controller so it will be responsible for four points as follow:

#### A. Decode Processor Commands:

Command Decoder decodes processor commands based on control signals from CPU (Ctrl\_Read, Ctrl\_Write, Ctrl\_Burst, Ctrl\_Auto) and sets signal CMD with code equivalent to the decoded command, the description of each processor command and it's equivalent code are shown in Table 5:

| Command                   | Description                                               | CMD |

|---------------------------|-----------------------------------------------------------|-----|

| Read                      | Read operation with default BL16 mode                     | 000 |

| Write                     | Write operation with default BL16 mode                    | 001 |

| Read_With_AutoPrecharge   | Read operation with autoprecharge with default BL16 mode  | 010 |

| Write_With_AutoPrecharge  | Write operation with autoprecharge with default BL16 mode | 011 |

| Read_Burst                | Read operation with BC8 mode                              | 100 |

| Write_Burst               | Write operation with BC8 mode                             | 101 |

| Read_Burst_AutoPrecharge  | Read operation with autoprecharge with BC8 mode           | 110 |

| Write_Burst_AutoPrecharge | Write operation with autoprecharge with BC8 mode          | 111 |

#### Table 5: Description of Processor Commands

The decoded command based on control signals from CPU is shown in Table 6:

#### Table 6: Decoding of Processor Commands

| Decoded Command           | Ctrl_Read | Ctrl_Write | Ctrl_Burst | Ctrl_Auto |

|---------------------------|-----------|------------|------------|-----------|

| Read                      | 1         | 0          | 0          | 0         |

| Write                     | 0         | 1          | 0          | 0         |

| Read_With_AutoPrecharge   | 1         | 0          | 0          | 1         |

| Write_With_AutoPrecharge  | 0         | 1          | 0          | 1         |

| Read_Burst                | 1         | 0          | 1          | 0         |

| Write_Burst               | 0         | 1          | 1          | 0         |

| Read_Burst_AutoPrecharge  | 1         | 0          | 1          | 1         |

| Write_Burst_AutoPrecharge | 0         | 1          | 1          | 1         |

#### ♦ Assumption & Notes:

As we saw that we have four control signals so we have 16 combinations of values, we showed only in Table 6 eight of them but the last eight combination will have Ctrl\_Read=1 and Ctrl\_Write=1 and this is an error from CPU and unintentional but our design deals with this error by decoding this case as read command as a default command but don't store this command in Command\_Address\_FIFO.

#### **B.** Detect Same Bank Group:

Bank\_Group signal represents bank group address; Command Decoder compares this address with address of previous command and set Same\_Bank\_Group signal high if they are equal. We need Same\_Bank\_Group signal in our design as the value of timing parameters between memory commands depends on if the two commands have the same bank group address or not.

#### C. Enable FSM:

As we made three separate FSMs (Command, Initialization, Self-Refresh), so we made three enable signals (CMD\_FSM\_Enable, INIT\_FSM\_Enable, SR\_FSM\_Enable) to choose only one FSM to work and disable the other two FSMs during working of the selected FSM. There is also signal called Memory\_Busy must be set high during working of INIT\_FSM or SR\_FSM. We can say that we have three operations Initialization, Self-Refresh and Normal Operation (reading and writing), so we should set priority for executing these operations. Priority of enabling them will be in this order: Initialization - Self Refresh - Normal. The description of each enable signal is shown in Table 7:

| Signal          | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT_FSM_Enable | Command Decoder should set this signal high when comes from CPU<br>Ctrl_Reset signal then set it low to disable INIT_FSM after Reset_Done<br>becomes high noting that Reset_Done will be input from INIT_FSM that is<br>raised high when initialization sequence finishes. When INIT_FSM_Enable<br>becomes high, Memory_Busy signal is raised high                     |

| SR_FSM_Enable   | Command Decoder should set this signal high when comes from self-refresh<br>counter tREFI signal, then set it low to disable SR_FSM after SR_Done<br>becomes high noting that SR_Done will be input from SR_FSM that is<br>raised high when self-refresh sequence finishes. When SR_FSM_Enable<br>becomes high,Memory_Busy signal is raised high                       |

| CMD_FSM_Enable  | Command Decoder should set this signal high when reading enable of<br>Command_Address_FIFO becomes high then set it low to disable<br>CMD_FSM after Memory_Busy comes high or CMD_Done becomes high<br>noting that CMD_Done will be input from CMD_FSM that is raised high<br>when command finishes. When CMD_FSM_Enable becomes<br>high,Memory_Busy signal is set low |

Table 7: Description of Enable Signals of Finite State Machines

**D. Read &Write Enable Signals for FIFOs:**

Command decoder here will be responsible for driving values of enable signals of FIFOs. The description of each enable signal is shown in Table 8:

| Table 8: Description of Enable Signals of FIFOs |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| CMD_FIFO_RD_En                                  | Command Decoder will set this enable signal high when<br>Command_Address_FIFO is not empty and there isn't initialization or<br>self-refresh process running (i.e., Memory_Busy=0) and pervious<br>command has been executed. Command Decoder will set this signal low<br>in the next cycle of setting it high.                                                                                                                                                                                                                          |  |

| CMD_FIFO_WR_En                                  | Command Decoder will set this signal high when comes from CPU read or<br>write request, so Command Decoder will decode this request to command<br>and set this enable signal high to store this command in<br>Command_Address_FIFO and to handle error that we said before comes<br>read and write request in the same time, Command Decoder will ignore<br>this by not storing this command by disable this write enable signal in this<br>case. Command Decoder will also set this signal low in the next cycle of<br>setting it high. |  |

|                                                 | We defined signal called Data_Write_Transfer comes from<br>Command_FSM as output of WRITING_DATA state to indicate that we                                                                                                                                                                                                                                                                                                                                                                                                               |  |

need activate WR\_Data\_RD\_En to store this data in memory so Command Decoder will set read enable of Write\_Data\_FIFO high when this signal is

Command Decoder will act also as CMD FIFO WR En signal but this time, it will set this signal high when the request is write to store data that

comes with write request in Write\_Data\_FIFO and also will set it low in

raised high and set it low when this signal is lowered low.

6 515 0

#### **Assumption & Notes** ∻

WR\_Data\_RD\_En

WR Data WR En

Command Decoder set these enable signals low in the next cycle of setting it high to avoid unwanted read or write operation from FIFO, this thing isn't applied on WR Data RD En signal as we don't want to disable reading from Write Data FIFO in next cycle, we need read from it more than one cycle as memory takes data from controller with width of DQ bus(16 bit) and can't take 256 bit in one cycle. So, Write\_Data\_Transfer signal will be responsible for setting this enable signal low when transfer data from controller to memory finishes.

the next cycle of setting it high.

# 2.5.2 Command\_Address\_FIFO 2.5.2.1 Block Diagram $CMD_FIFO_Reset \longrightarrow CK_t \longrightarrow CK_t \longrightarrow CK_t \longrightarrow CMD_ADD_FIFO \longrightarrow CMD_FIFO_FULL \longrightarrow CMD_FIFO_FULL \longrightarrow CMD_FIFO_Empty$ $CMD_FIFO_RD_En \longrightarrow CMD_FIFO_WR_En \longrightarrow CMD_$

Figure 9: Block Diagram of Command\_Address\_FIFO.

## 2.5.2.2 List of Inputs & Outputs

Table 9: Inputs of Command\_Address\_FIFO.

| Signal         | Description                                                                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD_FIFO_Reset | Active high reset signal for FIFO, it's raised high when initialization sequence finishes.                                                                  |

| CK_t,Ck_c      | Differential clock of DDR5 SDRAM, all address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c. |

| CMD[2:0]       | Decoded Command comes from Command Decoder.                                                                                                                 |

| Ctrl_ADD[30:0] | Address that data will be read from memory or written in memory.                                                                                            |

| CMD_FIFO_RD_En | Read enable signal of FIFO comes from Command Decoder.                                                                                                      |

| CMD_FIFO_WR_En | write enable signal of FIFO comes from Command Decoder.                                                                                                     |

Table 10: Outputs of Command\_Address\_FIFO

| Signal         | Description                                                      |

|----------------|------------------------------------------------------------------|

| FIFO OUT[33:0] | Output of FIFO that contains information stored in FIFO (CMD and |

| FIF0 001[33.0] | Ctrl_ADD concatenated)                                           |

| CMD_FIFO_FULL  | Flag when 1 defines that FIFO is full.                           |

| CMD_FIFO_Empty | Flag when 1 defines that FIFO is empty.                          |

#### 2.5.2.3. Operation

Command decoder receives from CPU command every clock cycle but to execute the command by memory it needs more than one clock cycle as speed of CPU differs from speed of memory. Memory also does internal operations and features (i.e., self-refresh, Initialization, etc.), so memory can't always handle processor commands only. So, to avoid ignoring commands or drop of commands from CPU, we will store these commands and their related addresses from CPU in

storage then after we finish command, we will take the next from storage to execute it and so on. We followed a simple policy First Come First Serve (FIFO) in scheduling and selecting which command will be executed. There are other polices that can achieve high performance than this policy but they will be more complex in implementation.

#### ♦ Assumption & Notes

FIFO\_OUT [33:31] represents CMD and FIFO\_OUT [30:0] represents Ctrl\_ADD.

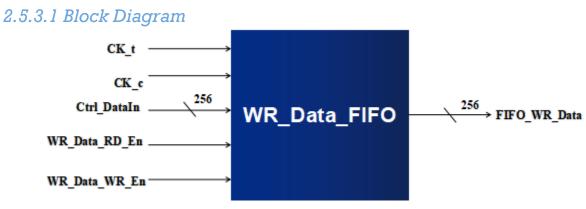

## 2.5.3 Write\_Data\_FIFO

Figure 10: Block Diagram of Write\_Data\_FIFO

#### 2.5.3.2 List of Inputs & Outputs

Table 11: Inputs of Write\_Data\_FIFO

| Signal                                                                                               | Description                                                                                                                                               |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t,CK_c                                                                                            | Differential clock of DDR5 SDRAM,all address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c |

| Ctrl_DataIn[255:0]       Data comes from CPU that will be written in memory during writing operation |                                                                                                                                                           |

| WR_Data_RD_En Read enable signal of FIFO comes from Command Decoder                                  |                                                                                                                                                           |

| WR_Data_WR_En Write enable signal of FIFO comes from Command Decoder                                 |                                                                                                                                                           |

Table 12: Outputs of Write\_Data\_FIFO

|   | Signal              | Description                                                            |

|---|---------------------|------------------------------------------------------------------------|

| Ī | FIFO WR Data[255:0] | Output of FIFO that contains data stored in FIFO to store it in memory |

#### 2.5.3.3 Operation

As we discussed before why we need FIFO and answered this question that we need it to store information that comes from CPU to used it later ,in Command\_Address\_FIFO we store command and address.It's still data need to be stored when write request comes then we made Write\_Data\_FIFO and here comes question why we used two FIFOs instead of only one and we can answer this question that we need to read data from controller to store it in memory in time differs from time of reading command and address so we will need two read enables so we made better a seperate FIFO for data

#### 2.5.4 Calculation of Depth of FIFOs

FIFO depth calculation is a critical phase in the design which needs to consider the worst case in all aspects and to do some assumptions [6]:

#### ♦ Assumptions

- 1. Burst length (No. of data items to be transferred) = 120

- 2. Write frequency (Processor frequency) = 3.2 GHz

- 3. Reading frequency (Memory frequency) = 3.2 GHz

- 4. Command execution in 30 cycles (worst case)

#### ♦ Calculations:

- Time required to write one data =  $\frac{1}{3.2GHz}$  = 0.3125ns

- > Time required to read one data (execute command) =  $30*\frac{1}{3.2GHz} = 9.375$ ns

- > Time required to write all the data in the burst = 120\*0.3125 = 37.5 ms

- Number of data items can be read in a duration of  $37.5ns = \frac{37.5ns}{9.375ns} = 4$

- > The remaining no. of information to be stored in the FIFO = 120 4 = 116

Then, the **minimum depth of the FIFO in our case should be equal 116.** In our code for simplicity we used depth=16 but in practical we should use depth as we mentioned.

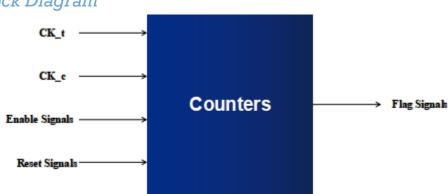

#### 2.5.5 Counters

2.5.5.1 Block Diagram

Figure 11: Block Diagram of Counters.

#### 2.5.5.2 Operation

There are timing parameters in our design, then we used this block that contains some counters to count these parameters. Each Counter has Enable to enable counting when we enter certain state and want to count some parameters, after we reached value of timing parameter that we count it, counter outputs a flag indicates that counting has finished and after finishing counting, reset input to counter is raised high to reset counter.

#### 2.5.5.3 List of Timing Parameters

Table 13: Initialization Timing Parameters [5]

| Timing Parameter                                                    | Symbol | Value             |

|---------------------------------------------------------------------|--------|-------------------|

| Minimum reset_n low time after completion<br>of voltage Ramp        | tINIT1 | 200 µs            |

| Minimum cs_n low time before reset_n high                           | tINIT2 | 10 ns             |

| Minimum cs_n low time after reset_n high                            | tINIT3 | 4 ms              |

| Minimum time for dram to register exit on cs_n with cmos            | tINIT4 | 2 μs              |

| Minimum cycles required after cs_n high                             | tINIT5 | 3 nCK             |

| Minimum time from exit reset to first valid configuration command   | tXPR   | 2 μs              |

| Minimum delay from MRR or MRW<br>command to any other valid command | tMRD   | max (14ns, 16nCK) |

| ZQ Calibration Time                                                 | tZQCAL | 1 µs              |

| ZQ Calibration Latch Time                                           | tZQLAT | max(30ns,8nCK)    |

| Timing Parameter                                       | Symbol | Value          |

|--------------------------------------------------------|--------|----------------|

| ACT to Precharge<br>command delay                      | tRAS   | 32 ns          |

| ACT to ACT Command delay to same bank group            | tRRD_L | Max(8nCK, 5ns) |

| ACT to ACT Command<br>delay to different bank<br>group | tRRD_S | 8nCK           |

Table 14: Activate Timing Parameters [5].

Table 15: Precharge Timing Parameters [5].

| Timing Parameter | Symbol | Value     |

|------------------|--------|-----------|

| Precharge delay  | tRP    | 13.750 ns |

#### Table 16: Reading Timing Parameters [5].

| Timing Parameter                          | Symbol         | Value             |

|-------------------------------------------|----------------|-------------------|

| Minimum Read to Read                      |                |                   |

| command delay for same                    | tCCD_L_slr     | Max(8nCK, 5ns)    |

| bank group                                |                |                   |

| Minimum Read to Read<br>command delay for | tCCD S slr     | 8 nCK             |

| different bank group                      | 100D_5_51      | 0 IICIX           |

| Minimum Read to Write                     |                |                   |

| command delay for same                    | tCCD_L_RTW_slr | 20 ns             |

| bank group                                |                |                   |

| Minimum Read to Write                     |                |                   |

| command delay for                         | tCCD_S_RTW_slr | 15 ns             |

| different bank group                      |                |                   |

| Internal Read command                     |                |                   |

| to Precharge command                      | tRTP           | Max(12nCK, 7.5ns) |

| delay                                     |                |                   |

Table 17: Writing Timing Parameters [5].

| Timing Parameter                                                    | Symbol        | Value            |

|---------------------------------------------------------------------|---------------|------------------|

| Minimum Write to Write<br>command delay for same<br>bank group      | tCCD_L_WR_slr | Max(32nCK, 20ns) |

| Minimum Write to Write<br>command delay for<br>different bank group | tCCD_S_WR_slr | 8 nCK            |

| Minimum Write to Read<br>command delay for same<br>bank group      | tCCD_L_WTR_slr | 20 ns |

|--------------------------------------------------------------------|----------------|-------|

| Minimum Write to Read<br>command delay for<br>different bank group | tCCD_S_WTR_slr | 15 ns |

Table 18: Self-Refresh Timing Parameters [5].

| Timing Parameter                                                  | Symbol      | Value  |

|-------------------------------------------------------------------|-------------|--------|

| Command pass disable delay                                        | tCPDED      | 5 ns   |

| Self-Refresh CS_n low<br>Pulse width                              | tCSL        | 10 ns  |

| Self-Refresh exit CS_n<br>high                                    | tCASRX      | 0      |

| Self-Refresh exit CS_n<br>High Pulse width                        | tCSH_SRExit | 13 ns  |

| Self-Refresh exit CS_n<br>Low Pulse width                         | tCSL_SRExit | 3 nCK  |

| Exit Self-Refresh to next<br>valid command NOT<br>requiring a DLL | tXS         | 2µs    |

| Time interval between<br>two selfrefresh<br>operations            | tREFI       | 3.9 µs |

#### ♦ Assumption &Notes

**1.** These values of timing parameters are listed in JEDEC79-5 standard in section 3.3.1 Table 11, Table 329, Table 20, Table 467, Table 520, Table 481 and Table 525.

2. Our counters count in unit of clock cycles, so we needed to convert these values of timing parameters to form of multiple of clock cycles by dividing value of timing parameter /clock period

**3.** Enable and reset signals comes from FSMs blocks.

4. Outputs of these counters will be mainly inputs to FSMs blocks.

5. As we discussed before that each counter for timing parameter has reset, enable and flag that indicated counting has finished. Naming that we use here for reset signal of timing parameter counter is named by name of timing parameter and "Reset" word attached to it(for

ex: tINIT1\_Reset) ,the same thing for enable signal but "En" word is attached to it(for ex:tINIT1\_En) and for flag has name as the name of timing parameter(for ex:tINIT1).

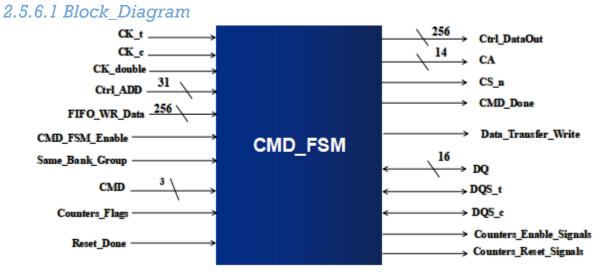

#### 2.5.6 Command\_FSM

Figure 12: Block Diagram of Command\_FSM

#### 2.5.6.2 List of Inputs and Outputs

Table 19: Inputs of Command\_FSM

| Signal                                                                          | Description                                                                                                                                                                                          |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                                                                      | Differential clock of DDR5 SDRAM, all address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK c.                                          |

| CK_double                                                                       | Clock that has double frequency of SDRAM clock, DQS signals will be<br>generated with positive edge of this clock, also data from memory will be<br>sampled also on the positive edge of this clock. |

| Ctrl_ADD[31:0] Address that data will be read from memory or written in memory. |                                                                                                                                                                                                      |

| <b>FIFO_WR_Data[15:0]</b> Output of write_data_FIFO.                            |                                                                                                                                                                                                      |

| CMD_FSM_Enable                                                                  | Enable signal of Command_FSM comes from Command Decoder.                                                                                                                                             |

| Same_Bank_Group Flag signal comes from Command Decoder.                         |                                                                                                                                                                                                      |

| CMD[2:0]         Decoded commend comes from Command Decoder.                    |                                                                                                                                                                                                      |

| Counter_Flags                                                                   | Activate parameters, Percharge parameters, Read Parameters-Write parameters.                                                                                                                         |

Table 20: Outputs of Command\_FSM

| Signal              | Description                                                                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ctrl_DataOut[255:0] | Data will be delivered from memory to CPU                                                                                                              |

| CA[13:0]            | Command/Address Inputs: CA signals provide the command and address<br>inputs according to the Command Truth Table in standard section 4.1<br>Table 241 |

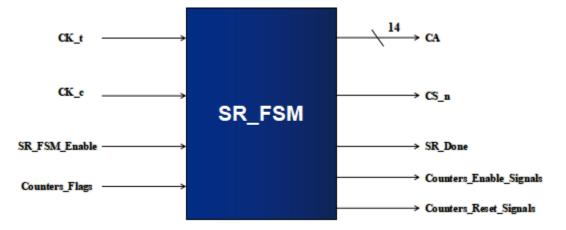

| CS_n                                             | Chip Select: all commands are masked when cs_n is registered high. for<br>one cycle commands (cs_n=0), for two cycle commands (cs_n=0 for first<br>cycle,cs_n=1 for second cycle).                   |  |  |