# SOFTWARE DEFINED RADIO (SDR)-RF IMPLEMENTATION WITH THE DIGITAL IMPLEMENTATION

By Chaymaa Ossama Mohamed Heba Magdy El-Gohary Heba Mahmoud Yassin Khadija Khalid Ali Mahetab Ossama Mohamed Yara Hossam El-Deen Mahmoud

**Under the Supervision of** Associate Prof. Hassan Mostafa Eng. Sherif Hosney

A Graduation Project Report Submitted to The Faculty of Engineering at Cairo University In Partial Fulfillment of the Requirements for The Degree of Bachelor of Science in Electronics and Communications Engineering

JULY 15, 2018 FACULTY OF ENGINEERING, CAIRO UNIVERSITY CAIRO, EGYPT

## **Table of Contents:**

| LIST OF SYMBOLS AND ABBREVIATIONS              | XII     |

|------------------------------------------------|---------|

| ACKNOWLEDGEMENT                                | VIV     |

|                                                | <u></u> |

| ABSTRACT                                       | XX      |

| <u>CHAPTER 1:</u> INTRODUCTION                 | 1       |

| 1.1. ORGANIZATION OF THE THESIS                | 1       |

| 1.2. SOFTWARE DEFINED RADIO (SDR)              | 2       |

| 1.2.1. INTRODUCTION                            | 2       |

| 1.2.2. Communication System                    |         |

| 1.2.3. SDR DEFINITION                          | 4       |

| 1.2.4. SDR Advantages                          | 5       |

| 1.2.5. SDR IMPLEMENTATION                      | 6       |

| 1.3. FIELD PROGRAMMABLE GATE ARRAY (FPGA)      | 6       |

| 1.3.1. FPGA CONFIGURATION                      | 7       |

| 1.3.2. Types of configuration                  |         |

| 1.3.2.1. Full/Fixed Reconfiguration            |         |

| 1.3.2.2. Static partial reconfiguration        |         |

| 1.3.2.3. Dynamic partial reconfiguration (DPR) | 9       |

| 1.4. DYNAMIC PARTIAL RECONFIGURATION (DPR)     | 9       |

| 1.4.1. ADVANTAGES OF DPR                       |         |

| 1.4.2. DPR MODES                               |         |

| 1.4.2.1. External Mode                         |         |

| 1.4.2.2. Internal Mode                         |         |

| 1.4.3. DPR FLOW                                |         |

| 1.5. PROGRESS OF THE PREVIOUS YEARS            |         |

| 1.5.1. INTERNSHIP SUMMER 2014                  |         |

| 1.5.2. GRADUATION PROJECT 2015                 |         |

| 1.5.3. GRADUATION PROJECT 2016                 |         |

| 1.5.4. GRADUATION PROJECT 2017                 |         |

| <u>CHA</u> | <u> PTER 2:</u> | SEPARATION                   |  |

|------------|-----------------|------------------------------|--|

| 2.1.       | TRANSMIT        | ITER AND RECEIVER SEPARATION |  |

| 2.2.       | OVERVIEV        | N                            |  |

| 2.3.       | DIRECT M        | IEMORY ACCESS (DMA)          |  |

| 2.3.1.     | THE DM.         | A FUNCTIONS                  |  |

| 2.3.2.     | DMAC            |                              |  |

| 2.4.       | INPUT INT       | 'ERFACE                      |  |

| 2.5.       | DATA SPLI       | ITTER                        |  |

| 2.6.       | WIFI STAN       | NDARD IP BLOCK               |  |

| 2.6.1.     | WIFI TRA        | ANSMITTER                    |  |

| 2.6.1.     | 1. Data So      | crambler                     |  |

| 2.6.1.     | 2. Convol       | lutional Encoder             |  |

| 2.6.1.     | 3. Punctur      | ring                         |  |

| 2.6.1.     | 4. Interlea     | aver                         |  |

| 2.6.1.     | 5. Modula       | ation Mapper                 |  |

| 2.6.1.     | 6. IFFT N       | Modulation                   |  |

| 2.6.1.     | 7. Preamb       | ble                          |  |

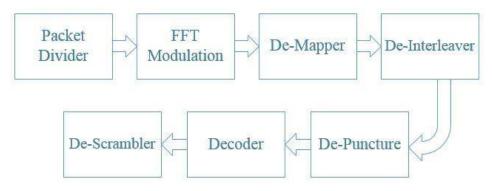

| 2.6.2      | WIFI REC        | CEIVER                       |  |

| 2.6.2      | 1. Packet       | t Divider                    |  |

| 2.6.2      | 2. FFT me       | odulation                    |  |

| 2.6.2      | 3. De-Maj       | pper                         |  |

| 2.6.2      | 4. De-Inte      | erleaver                     |  |

| 2.6.2      | 5. De-Pun       | ncture                       |  |

| 2.6.2      | 6. Viterbi      | i decoder                    |  |

| 2.6.2      | 7. De-Scr       | ambler                       |  |

| 2.7.       | FIRST IN F      | FIRST OUT MEMORY (FIFO)      |  |

| 2.7.1      | Introdu         | JCTION                       |  |

| 2.7.2.     | FIFO'S R        | RULE                         |  |

| 2.8.       | AXI INTER       | RFACE                        |  |

| 2.8.1.     | AXI4 TY         | PES                          |  |

| 2.8.2.     | AXI4-LI         | ТЕ                           |  |

| CHAPTER 3: INTERFACING                                                       |        |

|------------------------------------------------------------------------------|--------|

| USRP AND GNU RADIO INTERFACE                                                 |        |

| 3.1. USRP                                                                    |        |

| 3.1.1. USRP HARDWARE                                                         |        |

| 3.1.2. USRP BENEFITS                                                         |        |

| 3.1.3. USRP HARDWARE DRIVER (UHD)                                            |        |

| 3.1.4. USRP USED IN OUR PROJECT                                              |        |

| 3.2. GNU RADIO                                                               | 51     |

| 3.2.1. INTRODUCTION                                                          | 51     |

| 3.2.2. DEFINITION                                                            | 51     |

| 3.2.3. WHAT EXACTLY DOES GNU RADIO DO?                                       |        |

| 3.2.4. GNU RADIO LIVE SDR ENVIRONMENT                                        | 54     |

| 3.2.5. INSTALLING GRC                                                        |        |

| 3.2.6. USING GRC                                                             | 55     |

| 3.2.6.1. GRC Architecture                                                    | 55     |

| 3.2.6.2. Graphical signal processing development                             | 55     |

| 3.2.6.3. Using Python to write powerful signal processing and radio applicat | ions58 |

| 3.2.6.4. The C++ domain: Extending GNU Radio                                 |        |

| 3.2.7. EXAMPLE USED IN OUR PROJECT                                           |        |

| 3.2.7.1. Basic block diagram                                                 |        |

| 3.2.7.2. Experiment set up and plan                                          | 60     |

| <u>CHAPTER 4:</u> <u>ZYNQ ZC702 EVALUATION BOARD</u>                         | 61     |

| 4.1. ZYNQ 7000 FAMILY OVERVIEW                                               | 61     |

| <b>4.2.</b> INTRODUCTION TO ZC702                                            |        |

| 4.3. LOOK-UP TABLE (LUT)                                                     |        |

| 4.4. CLB OVERVIEW                                                            |        |

| 4.5. VIVADO DESIGN SUITE OVERVIEW                                            |        |

| 4.6. SDK OVERVIEW                                                            | 65     |

| CHAPTER 5: LINUX IMAGE                               |         |

|------------------------------------------------------|---------|

| USRP AND ZYNQ BOARD INTERFACE USING LINUX IMAGE      | 66      |

| USAT AND ETHQ BOARD INTERFACE USENO LENCA EMAGE      | <u></u> |

| 5.1. XILINX ZYNQ LINUX KERNEL                        |         |

| 5.1.1. XILINX ZYNQ LINUX SUPPORT                     |         |

| 5.1.2. USING A PRE-BUILT IMAGE/RELEASE               |         |

| 5.1.3. KERNEL DETAILS                                |         |

| 5.1.3.1. The Board Support Package (BSP)             |         |

| 5.1.3.2. Device Tree                                 |         |

| 5.1.3.3. Device tree basics                          |         |

| 5.2. YOCTO PROJECT                                   |         |

| 5.2.1. INTRODUCING THE YOCTO PROJECT                 |         |

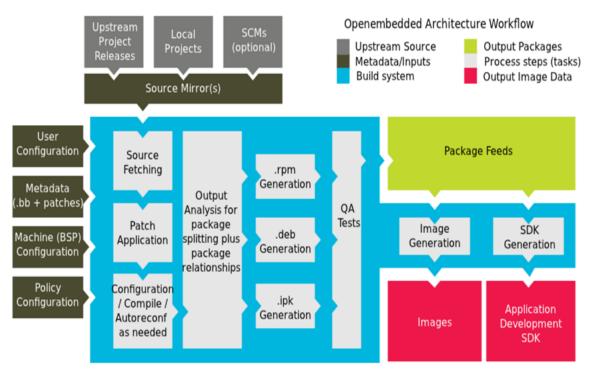

| 5.2.2. THE OPENEMBEDDED BUILD SYSTEM WORKFLOW        |         |

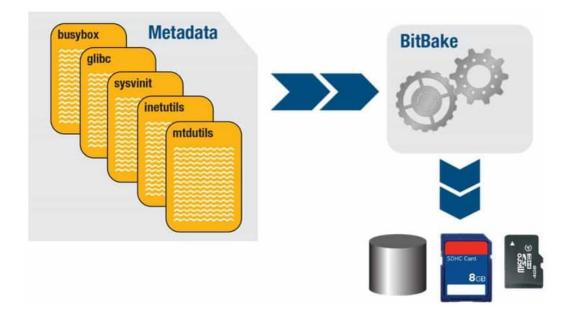

| 5.2.3. BITBAKE                                       | 71      |

| 5.2.4. OPENEMBEDDED-CORE                             |         |

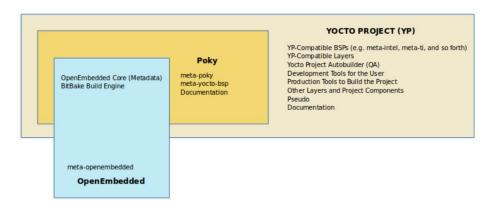

| 5.2.5. Року                                          |         |

| 5.2.6. METADATA SET                                  | 74      |

| 5.2.7. BOARD SUPPORT PACKAGES                        | 74      |

| 5.2.8. CUSTOMIZING THE BUILD FOR SPECIFIC HARDWARE   |         |

| 5.2.8.1. Meta-Xilinx                                 |         |

| 5.2.8.2. Meta-Xilinx-Tools                           |         |

| 5.2.8.3. Meta-SDR                                    | 77      |

| 5.2.9. Нов                                           | 77      |

| 5.2.10. OPEN SOURCE LICENSE COMPLIANCE               | 77      |

| 5.2.11. EGLIBC                                       | 77      |

| 5.2.12. Application Development Toolkit              |         |

| 5.2.13. Other tools under the Yocto Project umbrella |         |

| 5.3. CREATING LINUX IMAGE                            |         |

| 5.3.1. PREPARE AND BOOT HARDWARE                     |         |

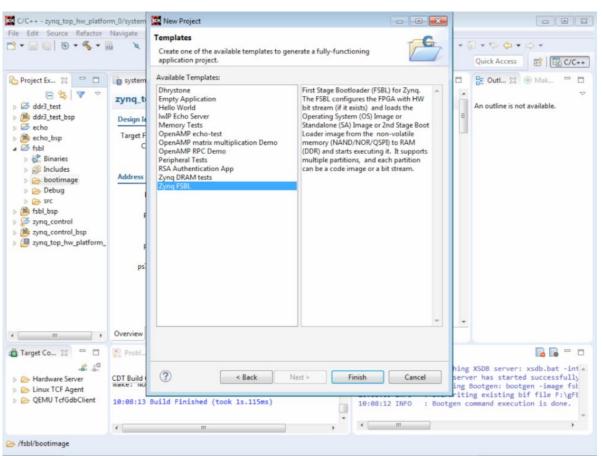

| 5.3.1.1. FSBL Method                                 |         |

## RUNNING LINUX AND BARE-METAL SYSTEM ON BOTH ZYNQ SOC PROCESSORS.......83

| 6.1.   | INTRODUCTION                                  | 83  |

|--------|-----------------------------------------------|-----|

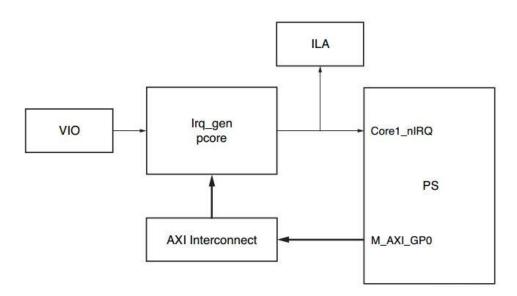

| 6.2.   | REFERENCE DESIGN                              | 83  |

| 6.2.1. | HARDWARE                                      | 86  |

| 6.2.2. | Address map                                   | 87  |

| 6.2.3. | SOFTWARE                                      | 87  |

| 6.2.4. | FSBL                                          | 87  |

| 6.2.5. | LINUX                                         | 88  |

| 6.2.6. | LINUX APPLICATIONS                            | 88  |

| 6.2.7. | BARE-METAL APPLICATION CODE                   | 89  |

| 6.2.8. | CPU1 APPLICATIONS                             | 90  |

| 6.2.9. | DESIGN FILES                                  | 91  |

| 6.2.10 | ). GENERATING HARDWARE                        | 91  |

| 6.2.11 | I. GENERATING APPLICATIONS                    | 92  |

| 6.2.11 | 1.1. Configuring SDK                          | 92  |

| 6.2.11 | 1.2. Creating Bare-Metal Application for CPU1 | 93  |

| 6.2.11 | .3. Creating Linux Application RWMEM          | 95  |

| 6.2.11 | .4. Creating Linux Application Soft UART      | 95  |

| 6.2.11 | 1.5. Creating Linux Kernel                    | 96  |

| 6.2.11 | 1.6. Creating Linux Device Tree               | 96  |

| 6.2.11 | 1.7. Creating U-Boot                          | 96  |

| 6.2.11 | 1.8. Acquiring Root File System               | 97  |

| 6.2.11 | 1.9. Generating Boot File                     | 97  |

| 6.2.12 | 2. COPYING FILES TO SD CARD                   | 98  |

| 6.2.12 | 2.1. Running the Design                       | 98  |

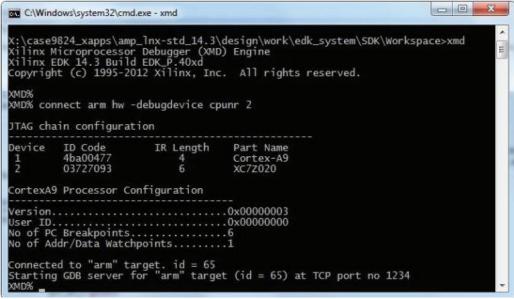

| 6.2.13 | 3. DEBUGGING THE DESIGN                       | 101 |

| 6.3.   | WIFI TRANSMITTER AND RECEIVER SYSTEM DESIGNS  | 103 |

| 6.3.1. | HARDWARE                                      | 104 |

| 6.3.2. | SOFTWARE                                      | 104 |

| 6.3.3. | FSBL                                          | 105 |

| 6.3.4. | LINUX                                         | 105 |

| 6.3.5. LINUX APPLICATIONS                                 |            |

|-----------------------------------------------------------|------------|

| 6.3.6. BARE-METAL APPLICATION CODE                        |            |

| 6.3.7. CPU1 APPLICATIONS                                  |            |

| 6.3.8. DESIGN FILES                                       |            |

| 6.3.9. GENERATING APPLICATIONS                            |            |

| 6.3.9.1. Configuring SDK                                  |            |

| 6.3.9.2. Creating Custom FSBL Application                 |            |

| 6.3.9.3. Creating Bare-Metal Application for CPU1         |            |

| 6.3.9.4. Creating Linux Application RWMEM                 |            |

| 6.3.9.5. Creating Linux Application Soft UART             |            |

| 6.3.10. Creating Linux Kernel                             |            |

| 6.3.11. CREATING LINUX DEVICE TREE                        |            |

| 6.3.11.1. Creating U-Boot                                 |            |

| 6.3.11.2. Acquiring Root File System                      |            |

| 6.3.11.3. Generating Boot File                            |            |

| 6.3.12. Copying Files to SD Card                          |            |

| 6.3.13. RUNNING THE DESIGN                                |            |

|                                                           |            |

| CHAPTER 7: CONCLUSION & FUTURE WORK                       |            |

|                                                           |            |

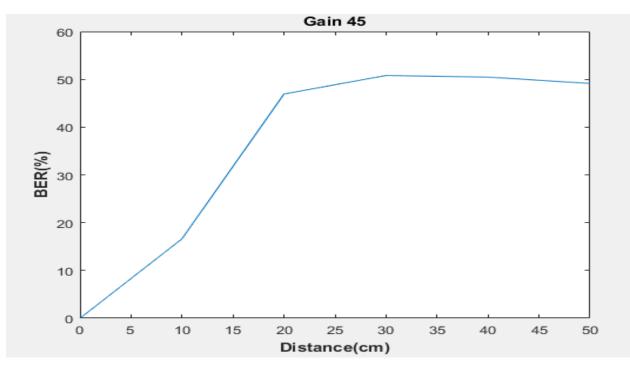

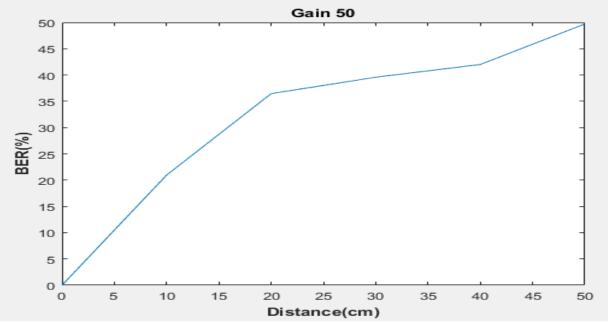

| 7.1. RESULTS SUMMARY                                      |            |

| 7.2. REAL-TIME TESTING RESULTS                            |            |

| 7.3. CONCLUSION                                           |            |

| 7.4. FUTURE WORK                                          |            |

| 7.4.1. INTERFACING USING ETHERNET                         |            |

| 7.4.2. COMMUNICATION                                      |            |

| 7.4.2.1. Channel Estimation                               |            |

| 7.4.2.2. Separating new systems                           |            |

| 7.4.3. Electronics                                        |            |

| 7.4.3.1. DPR between communication standards              |            |

| 7.4.3.2. Synchronization between transmitter and receiver |            |

| 7.4.4. RF                                                 |            |

|                                                           |            |

| REFERENCES                                                | <u>119</u> |

| APPENDIX A: USING THE FPGA INSIDE THE USRP |  |

|--------------------------------------------|--|

|                                            |  |

| APPENDIX B: ALTERNATIVE USRP SERIES        |  |

|                                            |  |

| APPENDIX C: PARTITIONING OF SD CARD        |  |

## **Table of Figures:**

| Figure 1-1. Simple communication system                                          |   |

|----------------------------------------------------------------------------------|---|

| Figure 1-2 SDR approach                                                          | 5 |

| Figure 1-3 FPGA blocks                                                           | 6 |

| Figure 1-4 FPGA layers                                                           | 7 |

| Figure 2-1 Illustration of AXI DMA use                                           |   |

| Figure 2-2 DMA block diagram                                                     |   |

| Figure 2-3 AXI DMA IP block                                                      |   |

| Figure 2-4 AXI DMA signals' functions                                            |   |

| Figure 2-5 cntd' DMA signals' functions                                          |   |

| Figure 2-6 DMAC system viewpoint                                                 |   |

| Figure 2-7 Difference problem of the system clock from the system I/P & O/P rate |   |

| Figure 2-8 the cycles illustrating the example                                   |   |

| Figure 2-9 Input Interface hardware                                              |   |

| Figure 2-10 Input interface IP block                                             |   |

| Figure 2-11 Data splitter IP block                                               |   |

| Figure 2-12 WIFI transmitter functional blocks                                   |   |

| Figure 2-13 Data scrambler block diagram                                         |   |

| Figure 2-14 PPDU frame format                                                    |   |

| Figure 2-15 Convolutional Encoder                                                |   |

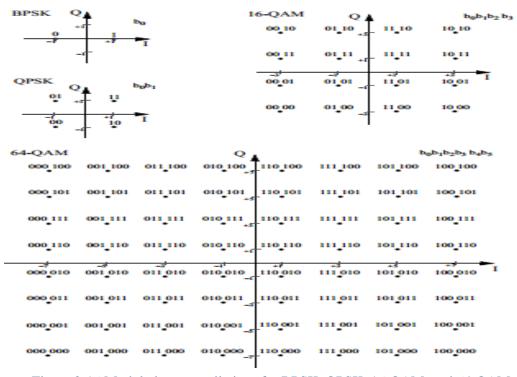

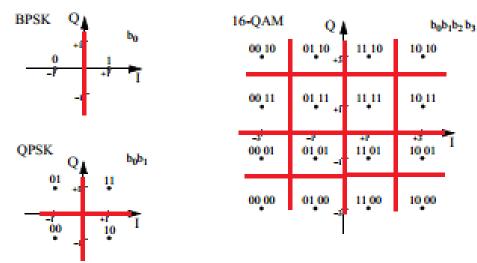

| Figure 2-16 Modulation constellations for BPSK, QPSK, 16-QAM, and 64-QAM         |   |

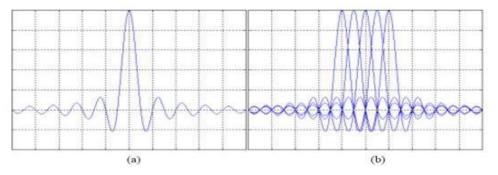

| Figure 2-17 (a) Spectrum of a single subcarrier of the OFDM signal,              |   |

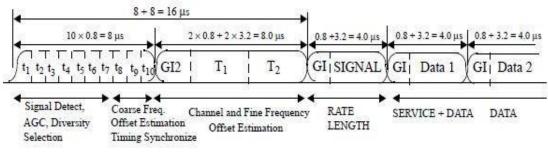

| Figure 2-18 OFDM training structure                                              |   |

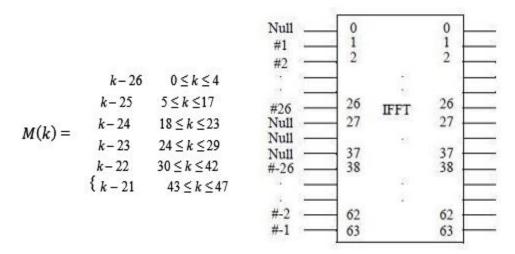

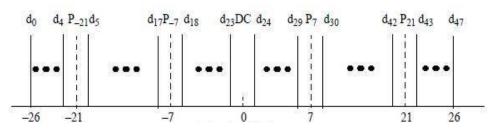

| Figure 2-19 frequency offset index function & inputs and outputs of the IFFT     |   |

| Figure 2-20 Final 64 sub-carrier mapping                                         |   |

| Figure 2-21 WIFI receiver full chain blocks                                      |   |

| Figure 2-22 Decision regions in the de-mapper                                    |   |

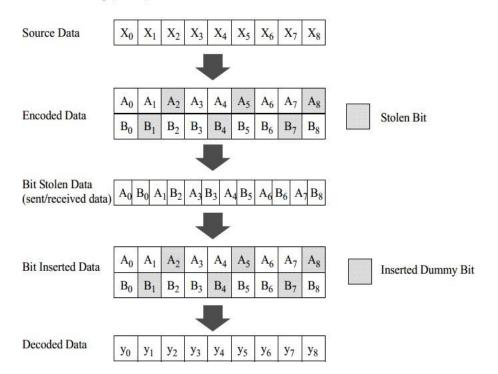

| Figure 2-23 De-puncture 3/4 rate procedure                                       |   |

| Figure 2-24 De-puncture 2/3 rate procedure                                       |   |

| Figure 2-25 Simple Architecture of using FIFO                                    |   |

| Figure 2-26 Dummy FIFO                                                           |   |

| Figure 2-27 Channel Architecture of Reads                |     |

|----------------------------------------------------------|-----|

| Figure 2-28 Channel Architecture of writes               | 44  |

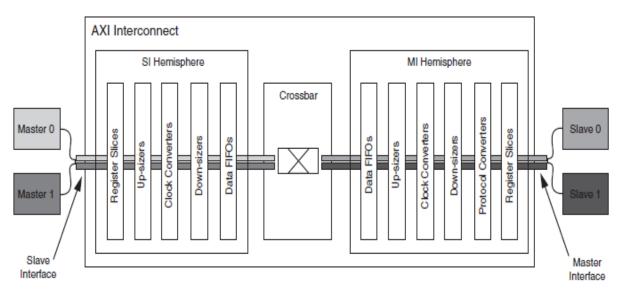

| Figure 2-29 Top level AXI interconnect                   |     |

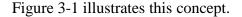

| Figure 3-1 UHD Components                                |     |

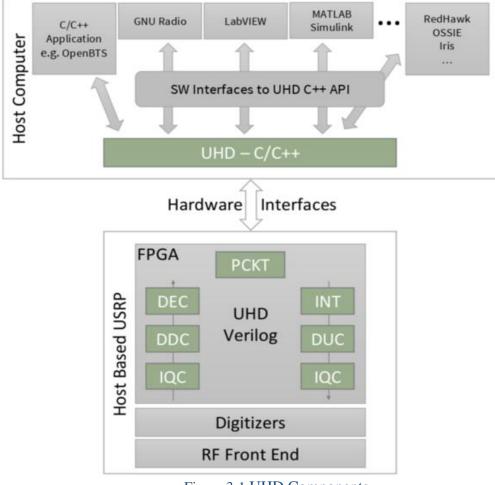

| Figure 3-2 Center Frequency fine tuning                  | 49  |

| Figure 3-3 B200 USRP                                     | 49  |

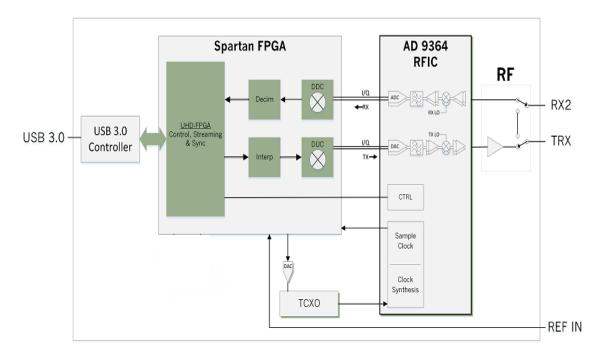

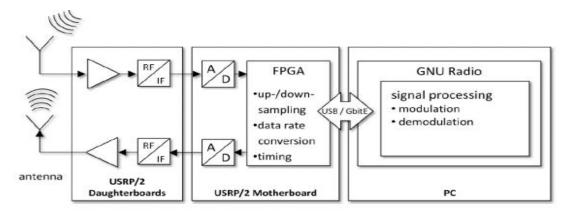

| Figure 3-4 The USRP block diagram                        | 50  |

| Figure 3-5 Software defined Radio Block Diagram          | 51  |

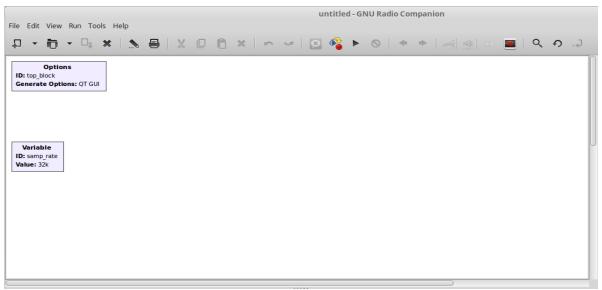

| Figure 3-6 GNU Radio graphical user interface            | 53  |

| Figure 3-7 GRC Architecture for Transmitter and Receiver | 55  |

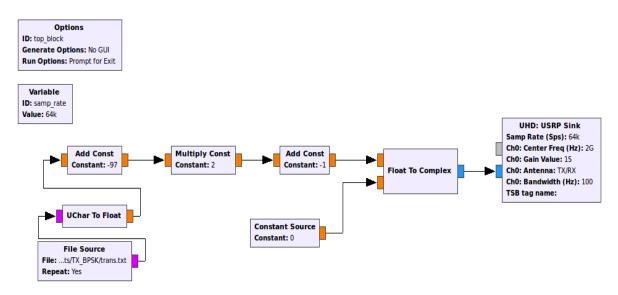

| Figure 3-8 GNU Radio BPSK transmitter flow graph         | 56  |

| Figure 3-9 GNU Radio BPSK receiver flow graph            | 57  |

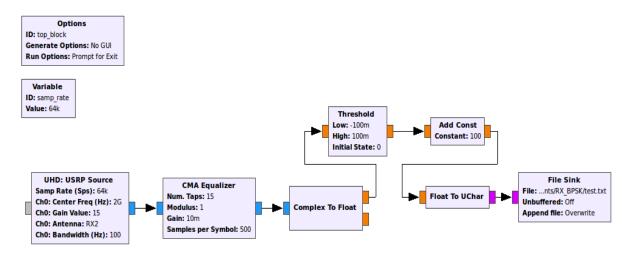

| Figure 3-10 Modified FM Receiver                         | 58  |

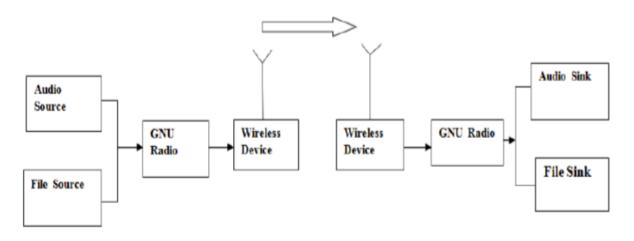

| Figure 3-11 Block diagram                                | 59  |

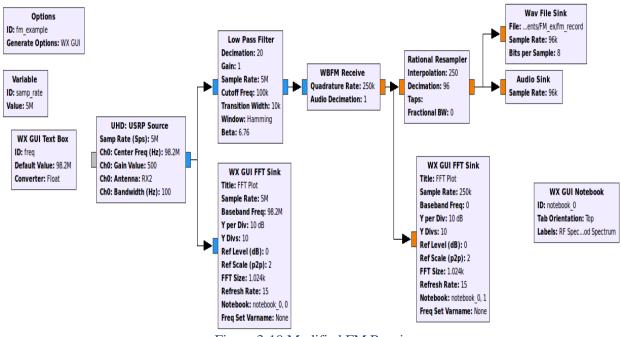

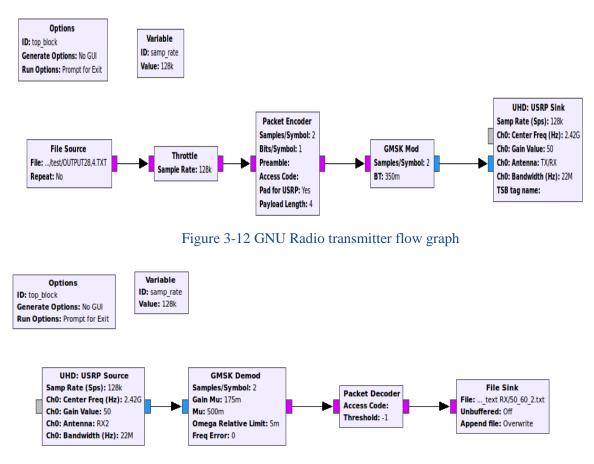

| Figure 3-12 GNU Radio transmitter flow graph             | 60  |

| Figure 3-13 GNU Radio Receiver flow graph                | 60  |

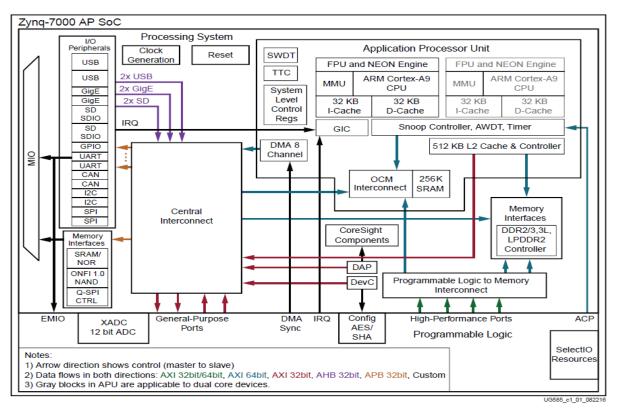

| Figure 4-1 Zynq-7000 AP SoC Block Diagram                | 62  |

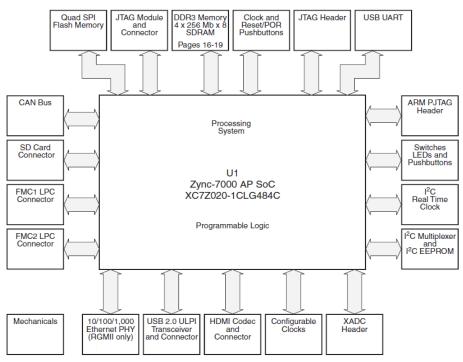

| Figure 4-2 ZC702 Board Block Diagram                     | 63  |

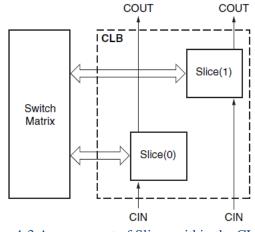

| Figure 4-3 Arrangement of Slices within the CLB          | 64  |

| Figure 4-4 ZYNQ board important resources                | 64  |

| Figure 5-1 Interfacing between PC and USRP               | 66  |

| Figure 5-2 OpenEmbedded Build System Workflow            |     |

| Figure 5-3 processing on metadata in BitBake             |     |

| Figure 5-4 Yocto project's components                    | 73  |

| Figure 5-5 Creating FSBL                                 | 79  |

| Figure 5-6 ZYNQ FSBL project                             | 80  |

| Figure 6-1 PL block diagram                              | 86  |

| Figure 6-2 IREQ_GEN control register                     | 87  |

| Figure 6-3 set NO stdin or stdout                        |     |

| Figure 6-4 CPU1 BSP add USE_AMP                          |     |

| Figure 6-5 Consol Output                                 | 100 |

| Figure 6-6 Connect XMD to CPU1                          | . 102 |

|---------------------------------------------------------|-------|

| Figure 6-7 CPU1 debug configuration                     | . 102 |

| Figure 6-8 CPU1 remote debug configuration              | . 103 |

| Figure 7-1 Transmitter and Receiver hardware full chain | . 113 |

| Figure 7-2 BER ratio for 45 gain and 128K sampling rate | . 114 |

| Figure 7-3 BER ratio for 50 gain and 128K sampling rate | . 115 |

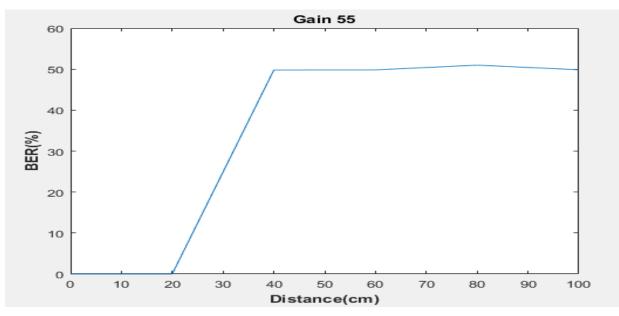

| Figure 7-4 BER ratio for 55 gain and 128K sampling rate | . 115 |

| Figure 7-5 The missing byte                             | . 116 |

| Figure 7-6 Project's prototype                          | . 117 |

## List of Symbols and Abbreviations

| 1G     | first generation                               |

|--------|------------------------------------------------|

| 2G     | second-generation                              |

| 3GPP   | 3 <sup>rd</sup> generation partnership project |

| ACP    | Accelerator Coherency Port                     |

| ADC    | Analog to Digital Converter                    |

| ADT    | Application Development Tool                   |

| AMP    | Asymmetric Multi-Processing                    |

| AMBA   | Advanced Microcontroller Bus Architecture      |

| AP SoC | All Programmable SoC                           |

| API    | Application Programmable Interface             |

| ARM    | Advanced RISC Machines                         |

| ASIC   | Application Specific Integrated Circuit        |

| AXI    | Advanced Extensible Interface                  |

| BIF    | Boot Image Format                              |

| BPSK   | Binary Phase Shift Keying                      |

| BSP    | Board support package                          |

| CLBs   | Configurable Logic Blocks                      |

| СР     | cyclic prefix                                  |

| CPU    | Central Processing Unit                        |

| CR      | Cognitive Radio                          |

|---------|------------------------------------------|

| CRC     | Cyclic Redundancy Check                  |

| DAC     | Digital to Analog Converter              |

| DCM     | Digital Clock Management                 |

| DCP     | Design Check Point                       |

| DDR     | Double Data Rate                         |

| Deb     | Debian                                   |

| DMA     | Direct Memory Access                     |

| DMAC    | Direct Memory Access Controller          |

| DPC     | Dirty Paper Coding                       |

| DPCCH   | Dedicated Physical Control Channel       |

| DPCCH2  | Dedicated Physical Control Channel 2     |

| DPDCH   | Dedicated Physical Data Channel          |

| DSP     | Digital Signal Processing                |

| DTB     | Device Tree Blob                         |

| DTS     | Device Tree Source                       |

| DUT     | Device Under Test                        |

| EDGE    | Enhanced Data rates for GSM Evolution    |

| E-DPCCH | E-DCH Dedicated Physical Control Channel |

| E-DPDCH | E-DCH Dedicated Physical Data Channel    |

| EGLIBC  | Embedded GNU C Library                   |

| eSDK | Extensible Software Development Kit                |

|------|----------------------------------------------------|

| ETSI | European Telecommunications Standards<br>Institute |

| FBI  | Feed-Back Information                              |

| FCC  | Federal Communications Commission                  |

| FF   | Flip Flops                                         |

| FFT  | Fast Fourier Transform                             |

| FIFO | First In First Out                                 |

| FPGA | Field Programmable Gate Array                      |

| FSM  | Finite state machine                               |

| FSBL | First Stage Boot Loader                            |

| GCC  | GNU Compiler Collection                            |

| GP   | General Purpose                                    |

| GPP  | General Purpose Processor                          |

| GPRS | General Packet Radio Services                      |

| GRC  | GNU Radio Companion                                |

| GSM  | Global System for Mobile                           |

| GUI  | Graphical User Interface                           |

| HDF  | Hardware Description File                          |

| HDL  | Hardware Description Language                      |

| HF   | High Performance                                   |

| HS-DPCCH | Dedicated Control Channel with HS-DSCH transmission |

|----------|-----------------------------------------------------|

| HSPA     | High Speed Packet Access                            |

| ΙΑ       | Intelligent Antenna                                 |

| IC       | Integrated Circuit                                  |

| ICAP     | Internal Configuration Access Port                  |

| ICD      | Interrupt Control Distributer                       |

| IDE      | Integrated Development Environments                 |

| IEEE     | Institute of Electrical and Electronics Engineers   |

| IFFT     | Inverse Fast Fourier Transform                      |

| IP       | Intellectual Property                               |

| IPK      | Itsy Package                                        |

| ISI      | Inter Symbol Interference                           |

| JTAG     | Joint Test Action Group                             |

| LNA      | Low Noise Amplifier                                 |

| LTE      | Long Term Evolution                                 |

| LUTs     | Look up Tables                                      |

| MAC      | Medium Access Control                               |

| MFIFO    | Multi-channel First In First Out                    |

| MM2S     | Memory Mapped to Streaming                          |

| MMU      | Memory Management Unit                              |

| MPDUs | MAC Protocol Data Units                    |

|-------|--------------------------------------------|

| MSCS  | Multi-Standard Communication System        |

| NBPSC | Number of Coded Bits Per Subcarrier        |

| OCM   | On Chip Memory                             |

| OE    | Open Embedded                              |

| OFDM  | Orthogonal Frequency Division Multiplexing |

| РА    | Power Amplifiers                           |

| PCAP  | Processor Configuration Access Port        |

| PCCC  | Parallel Concatenated Convolutional Code   |

| PDR   | Partial Dynamic Reconfiguration            |

| РНҮ   | Physical Layer                             |

| PL    | Programmable Logic                         |

| PLB   | Programmable Logic Blocks                  |

| PLCP  | Physical Layer Convergence Protocol        |

| PLL   | Phase Locked Loop                          |

| PMD   | Physical Medium Dependent                  |

| PPDU  | PLCP Protocol Data Unit                    |

| PPI   | Private Peripheral Interrupt               |

| PRC   | Partial Reconfiguration Controller         |

| PS    | Processing System                          |

| PSDU  | Physical layer Service Data Unit           |

| QAM     | Quadrature Amplitude Modulation                      |

|---------|------------------------------------------------------|

| QA      | Quality Assurance                                    |

| QEMU    | Quick Emulator                                       |

| QoS     | Quality of Service                                   |

| QPSK    | Quad Phase Shift Key                                 |

| RF      | Radio Frequency                                      |

| RP      | Reconfigurable Partition                             |

| RPM     | Red Hat Package Manager                              |

| S2MM    | Streaming to Memory Mapped                           |

| SCU     | Snoop Control Unit                                   |

| SC-FDMA | Single-Carrier Frequency Division Multiple<br>Access |

| SCM     | Source Code Management                               |

| S-DPCCH | Secondary Dedicated Physical Control Channel         |

| SD-Card | Secure Digital Card                                  |

| SDK     | Software Development Kit                             |

| SDR     | Software Defined Radio                               |

| SF      | Spreading Factor                                     |

| SMP     | Symmetric Multi-Processing                           |

| SPDX    | Software Package Data Exchange                       |

| SPI     | Serial Peripheral Interface                          |

| SoC   | System on Chip                              |

|-------|---------------------------------------------|

| TFCI  | Transport-Format Combination Indicator      |

| TPC   | Transmit Power Control                      |

| TrCH  | Transport Channel                           |

| TTI   | Transmission Time Interval                  |

| UART  | Universal Asynchronous Receiver-Transmitter |

| UHD   | USRP Hardware Driver                        |

| UMTS  | Universal Mobile Telecommunications System  |

| USB   | Universal Serial Bus                        |

| USRP  | Universal Software Radio Peripheral         |

| VIO   | Virtual Input Output                        |

| WCDMA | Wide Code Division Multiple Access          |

| WLAN  | Wireless Local Area Network                 |

| XSCT  | Xilinx Software Command Line Tool           |

## Acknowledgement

This year's work wouldn't have come to fruition if it were not for, after God, some pretty amazing people whom we got know this year. Without their help and support we wouldn't have been where we are today.

First, we would like to thank Dr. Hassan Mostafa for administering our work, providing us with the idea, the necessary guidance, the kits and a suitable working environment. We would also like to thank him for training us throughout the year for this day and keeping up with our work and encouraging team work and the collaboration between the teams to achieve the best results possible.

Second, we would like to thank Eng. Sherif Hosny for his guidance and time throughout the year and always responding to our questions regarding the last years' work. Also, Eng. Mostafa Gamal for meeting with us whenever possible and explaining the last year's work to us and putting us on the start of the road that took us where we are today.

Third, Eng. Ossama Ryad who was a great help with the USRP. Thank you for your help, your time and your patience in teaching us.

Fourth, we would like to thank Eng. Mohammed Osama for his immense help on the last leg of this journey and spending all his free time and vacation time with us trying to get the best results possible. Thank you for your time, effort and patience.

Last but not least, we would like to thank the previous years teams who have worked on this project and provided the great base on which we built our project.

## Abstract

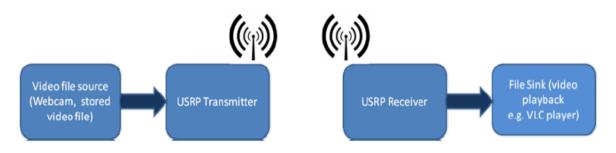

This year's part of the Software Defined Radio (SDR) graduation project discusses the implementation of communication chains via real channel for multi-standards on a partially reconfigurable heterogeneous platform as ZYNQ board and USRPs. It depends on the ability of the ZYNQ board to control the USRP board to use it as its RF plate form for transmitting and receiving.

Separating the transmitter and receiver blocks is needed in order to operate them on two different ZYNQ boards with two separate USRPs, so that real channel communication may take place. On each ZYNQ board, the two processors of the ZYNQ board are used independently to run two different applications on different platforms. One processor is used to run a bare metal application that runs on the FPGA which represents a single static standard -without DPR-. The other processor is used to run a Linux image which is used to control the USRP, by installing the UHD image.

During the project, experience has been gained in HDL, C/C++, GNU Radio, and Embedded-Linux.

The future work in this project will be integrating the Dynamic Partial Reconfiguration (DPR) of the previous year's project into this year's project using separate ZYNQ boards and real channel communication.

In the last few years, the number of users has increased significantly; a way was needed to handle the communication among them. Different types of standards have been implemented to compromise between area, power, quality and the large number of users. However, since those standards are not used simultaneously, every standard has its own transceiver which causes a big waste in area, power and correspondingly battery life. To solve those problems, SDR was proposed as a solution.

SDR is a way to implement the hardware using mainly software and simple hardware resources in order to decrease the hardware and use area in an efficient way. It is a way to define the physical layer functions in software.

In this thesis we are going to discuss the interface between the FPGA and USRP to have a real channel between transmitter and receiver, testing different communication standard behavior through the wireless channel.

## **1.1. Organization of the thesis**

This dissertation will go as follows; First, there is a brief introduction to the project, its purpose, the concepts it follows and its progress over the years. Second, this year's project is outlined and an introduction to the work needed to execute it is written. Third, the hardware and software tools and kits needed are introduced in detail, their benefits discussed and the purpose behind them elaborated. Fourth, a brief introduction to the main tool, ZYNQ board, its uses and main functions. Fifth, the integration between the USRP and ZYNQ board is discussed in detail and the steps taken to interface between them are explained. Sixth comes the chapter on how to operate two processors of the same board independently in order to operate both bare-metal codes and OS on the same board without interfering with each other, thus achieving the purpose of chapter five. Seventh, the conclusion of our work and the results we've achieved is depicted in this chapter along with the future work this project will need, in order to reach the market as a final working project that will save a lot of power, money and time.

## **1.2. Software Defined Radio (SDR)**

## **1.2.1. Introduction**

The communication standards are being developed and upgraded to satisfy the speed and the time to handle connectivity among the users, whose number is increasing with time. Consequently, different communication standards have been developed, but the radio frequency spectrum is not utilized in an efficient way [1, 2], as the communication bands are not being used simultaneously. The research in the radio spectrum utilization leads to two approaches to solve this problem, the first approach is the Intelligent Antenna (IA), which is an antenna array technology that uses spatial beam forming and signal processing algorithms to cancel interference and reuse of the space resources [3]. IA depends on the Dirty Paper Coding (DPC) technique. The second approach is the Cognitive Radio (CR), which dynamically configures the user terminals, to utilize the radio spectrum that is not used, depending on the available wireless channels detected without interfering with the other users. In other words, CR is considered a way of managing the radio spectrum in an efficient way and it can be developed using the SDR technique [4, 5].

Generally, in a Multi-Standard Communication System (MSCS) two major problems exist, the utilization of the radio spectrum pointed to in the previous paragraph and utilization of hardware. As each standard has its own transceiver this leads to high cost, large area, high power consumption and low battery life. At the same time, the development of the central base stations and the users' devices change tremendously to adapt to the new technologies and support the old ones. Developing hardware, upgrading and redistributing cost money and effort. These two major problems, unutilized radio spectrum and waste in hardware, initiated the research for finding new ways of reusing (reconfiguring) the same set of hardware to operate the old and new technologies. The utilization of the radio resources and the physical hardware resources can be done by off-loading the data transmitted between the different communication systems, and at the same time reconfiguring the hardware resources or reordering them to switch from one standard to another. SDR is a type of radio system implementation using software, which is used to form different waveforms. These waveforms allow the system to switch among different communication standards.

The motivation of SDR came from the existence of some physical layer blocks, which have the same functionality in different communication systems like (GSM, UMTS, LTE, etc....). Note that, these standards are not used at the same time which allows their hardware resources and radio spectrum resources to be shared among the standards and hence, be used in a more efficient way. Also, the switching among the different waveforms should be dynamic, more or less in real time. The Partial Dynamic Reconfiguration (PDR) is a technique used in the (FPGA), which allows hardware real time reconfigurable computing. By using the PDR's capability of dynamically changing and partially configured system files, real time SDR system can be implemented.

## **1.2.2.** Communication System

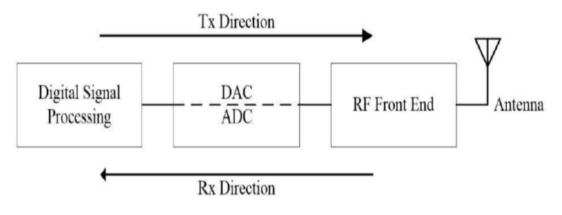

Figure 1-1 shows the main blocks in a modern communication system. It is composed of a Digital Signal Processing (DSP) unit, digital and analog converters (DAC, ADC), RF front end and antenna.

Figure 1-1 Simple communication system

High data rates can be achieved by processing the communication signals digitally using software, which is easier to develop, distribute and upgrade, the digital transceivers penetrate the traditional analog transceivers by pushing the digital and analog converters towards the antenna and pulling the communication systems more to software design on a given hardware.

This work will concentrate on the DSP block, however a brief description for each block is presented as follows:

- **Digital Signal Processing Block**: In the transmitter, this block is responsible for signal adaptation to be sent over a channel. Signal adaptation includes encryption, error correction coding schemes, modulation ...etc. Whereas, in the receiver this block is responsible for extracting the original information sent by the transmitter, by reconstructing the signal using demodulation, decoding and decryption. This block increases the flexibility of the radio development.

- **DAC/ADC Blocks:** Analog and digital converters used to transfer the signal between the analog domain and digital domain. Using ADC, the received signal is digitalized to be processed digitally using the DSP block. The digital representation depends on the sampling rate, which may lead to some information loss. On the other hand, the DAC can reconstruct the signal to nearly the original one.

- **RF Front End Block:** It is the classical block that contains the Low Noise Amplifier (LNA), filters and the Power Amplifier (PA). This block is the most challenging block in the SDR development.

- Antenna: Generally, the antenna is a passive device used to capture the electromagnetic waves from the surrounding media and converts it to an electrical signal. The antenna design complexity varies from a single antenna to multiple antenna arrays. The smart antenna is an antenna array that uses the signal processing algorithms to locate the direction of signal arrival and the reconfigurable antenna is capable of changing its frequency for adaptable systems.

## **1.2.3. SDR Definition**

The daily usage of communication standards is increasing. Phone calls, accessing the internet, sharing data and controlling devices are examples of modern communication usage. The devices using these standards vary in shape, functionality and the way of usage like cellphones, wireless routers, smart chips, smart metering ...etc. Although it is not easy to invent a generic device that can do everything, but it is achievable by using an adaptable communication device that can manage the communication between them all.

This adaptation is easier to be done through software defined modules, where these modules can change functionality by using the software.

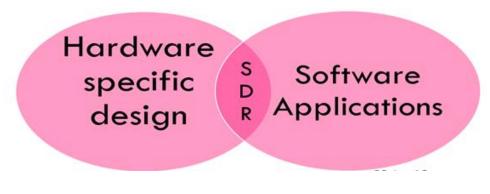

SDR is a way to implement the hardware using mainly software and simple hardware resources in order to decrease hardware and use area in an efficient way. It is a way to define the physical layer functions in software.

Figure 1-2 SDR approach

## **1.2.4. SDR Advantages**

There are many benefits for using SDR that it can be used in different industries and applications, hereby listing some of these advantages:

#### 1. Adaptability

The waveform is adapted to handle different scenarios for Radio. For example, if the Radio has low battery the waveform will be low powered or if it's downloading a file the waveform will have a high throughput and so on...

## 2. Interoperability

As some radios are incompatible with each other, SDR handles the communication between them.

## **3.** Frequency Reuse (cognitive Radio)

If there is an assigned band for a user and it is unused for a certain time, SDR can use it (borrow it) to increase its available band.

#### 4. Updating and Remote Upgrading

As we use the same hardware for different standards and the only change is in the software, we can easily update those standards and need no extra or new hardware or resources, so there is no need to go back to lab

## 5. Less Area and cost

The hardware is decreased. Hence, area, power and cost are decreased.

- 6. Ability to receive and transmit various modulation methods using a common set of hardware

- 7. The ability to alter functionality by downloading and running new software at will.

- **8.** The possibility of adaptively choosing an operating frequency and a mode best suited for prevailing conditions.

- **9.** Elimination of analog hardware and its cost, resulting in simplification of radio architectures and improved performance.

## **1.2.5. SDR Implementation**

SDR can be implemented on different hardware platforms such as General Purpose Processor (GPP), Digital Signal Processor (DSP), and Field Programmable Gate Array (FPGA). FPGA is suitable for high rate applications that have to be low in power and resources. Also, the high flexibility of the FPGA achieved by Dynamic Partial Reconfiguration (DPR) allows it to be used in hardware implementation of SDR as explained later.

## **1.3. Field Programmable Gate Array (FPGA)**

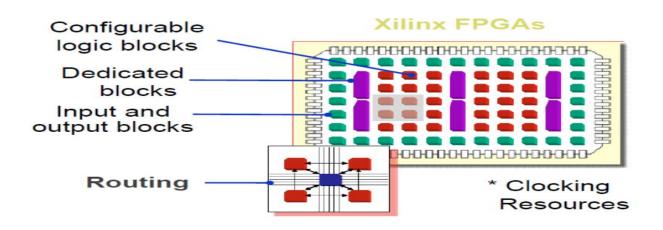

FPGA is a programmable device that can be configured by the user for any desired application. It consists of the following blocks as shown in the Figure 1-3:

- **1. Configurable Logic Blocks (CLBs):** include Look Up Tables (LUTs) and registers to implement combinational and sequential logic.

- 2. Dedicated blocks: such as DSP and RAM blocks.

- 3. Input and output blocks: are special logic blocks for external connectivity.

- **4. Routing:** connects inputs and outputs to CLBs or generally any source to any destination by connecting wires through switching matrices.

- **5.** Clocking resources: like digital clock manger (DCM). It is used to eliminate clock skew and to synthesize the desired clock frequency or shift phase.

## 1.3.1. FPGA configuration

FPGA is a volatile device, which means that its contents are erased once the power is turned off or interrupted so we need to configure it each time we need to use it.

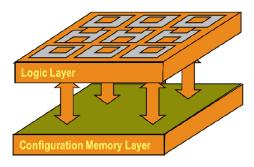

FPGA is considered a two-layered device as shown in the following Figure 1-4:

- Logic layer contains the logic to be configured as the desired application.

- 2. Configuration memory layer contains the configuration file used to configure the logic layer.

Figure 1-4 FPGA layers

## **1.3.2.** Types of configuration

## 1.3.2.1. Full/Fixed Reconfiguration

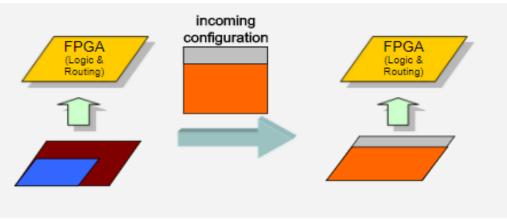

As shown in Figure 1-5, a configuration file is downloaded to configure the whole chip. FPGA has to stop working during downloading the new configuration file so, it takes long time to reconfigure the chip each time.

Figure 1-5 Full reconfiguration

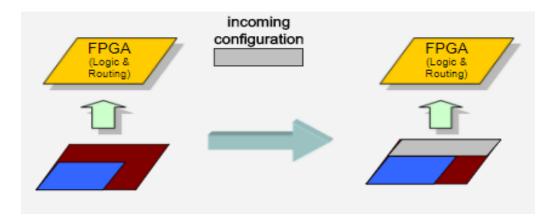

## 1.3.2.2. Static partial reconfiguration

As shown in Figure 1-6, an initial full bit file with complete configuration is downloaded for the whole chip then to reconfigure a part of the FPGA a partial bit file is downloaded while suspending the work of the FPGA. In this type the reconfiguration overhead time is reduced compared with the previous type.

Figure 1-6 Static partial reconfiguration

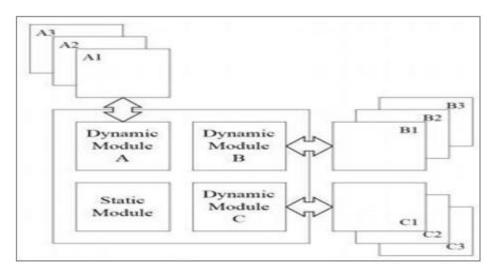

## **1.3.2.3.** Dynamic partial reconfiguration (DPR)

Like the previous type, an initial full bit file with complete configuration is downloaded at first, as shown in Figure 1-7. The main difference is that a part of the FPGA can be reconfigured at run time by loading a partial bit file to the configuration memory while the FPGA continues its normal operation except for this part so this decreases the reconfiguration time. As shown in the following figure, the FPGA is divided to static and dynamic parts. The static part is configured from the initial full bit file and remains fixed while the dynamic modules in the dynamic part is reconfigured at run time by partial bit files.

In our case, we are concerned with the Dynamic Partial Reconfiguration of the FPGA.

Figure 1-7 Dynamic partial reconfiguration

## 1.4. Dynamic Partial Reconfiguration (DPR)

DPR is very helpful in implementing multi-standard SDR system on a single chip as it allows runtime reconfiguration of a previously chosen partition on the FPGA to be reconfigured with partial bit-stream files.

## 1.4.1. Advantages of DPR

## 1. Resource Utilization

In static reconfiguration, for different standards to work simultaneously each standard must have its own resources but using DPR allows having only one set of resources that serves all standards in turn.

## 2. Upgradeability

All standards have different versions and updates that either make the system better or deals with a definite issue. DPR allows the download of the new update without any change in hardware as long as the resources reserved could support the new update. An updated partial bit-stream file can be downloaded to replace the older version.

## 3. Saving power

As there's only one chain working at a time and due to the lower utilization of resources, power is decreased considerably.

## 4. Saving money

Due to the decreased utilization of resources and the power saved, money is also saved. To load one of the partial bit-stream files stored into the reconfigurable partition we must use access ports such as JTAG, PCAP... etc. and different DPR modes.

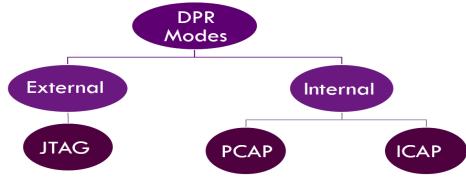

## 1.4.2. DPR Modes

XILINX offers two different modes for implementing DPR in order to transfer the bitstream file into the configuration memory, where each mode has different techniques (Only common and familiar techniques are discussed not all of them), as shown in Figure 1-8,.

Figure 1-8 DPR Modes

## **1.4.2.1. External Mode:**

Partial bit-stream are loaded through external source JTAG - Joint Test Action Group-. It has high reconfiguration time and a lot of time overhead due to headers, checksum and the transfer of the data from source of JTAG to the reconfigurable memory which takes about 150 msec.

The max theoretical bandwidth is approximately 66 Mbps and it transfers 1-bit at a time (i.e. serial) which leads to an actual BW of 8.25 Mbps.

## 1.4.2.2. Internal Mode:

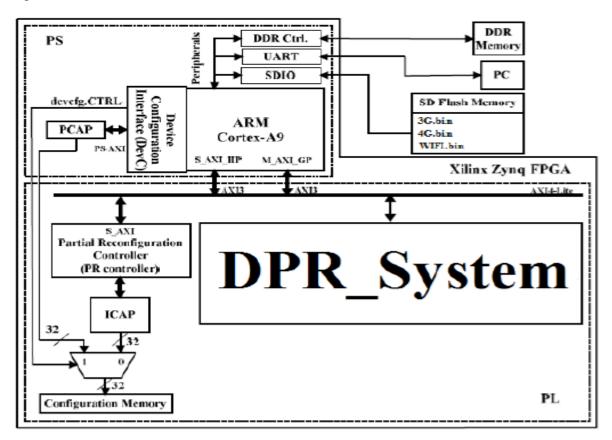

Reconfiguration takes place through an already implemented access port to the configuration memory. The ARM processor is responsible for the control signal which activates the MUX in PL to either be ICAP or PCAP. A quick system overview is shown in Figure 1-9.

Figure 1-9 PS & PL Configuration

#### a. Processor Configuration Access Port (PCAP)

Located in processing system (PS), it is controlled directly by the ARM cortex  $9_0$  processor. It has no memory of its own so it must retrieve 32-bits by 32-bits – bus size – of the partial bit-stream file stored in the DDR memory.

It takes a higher reconfiguration time than ICAP as it is limited by the speed and size of the bus and requesting to take the bus in the first place as it has no memory.

Theoretically it has a BW of 3.2 Gbps or 400 MB/sec but its actual BW is around 145 MB/sec.

#### **b.** Internal Configuration Access Port (ICAP)

It is located in the programmable logic (PL) partition and it is controlled through controllers. Those controllers have memories inside them which are small. They can hold parts of the partial bit-stream file in order to limit the use of the bus to certain periods of time during which the controller is the master of the bus. As the ICAP transfers the stored data in controller to reconfigurable memory the controller retrieves another segment simultaneously, decreasing the overall overhead on the reconfiguration time.

It has a theoretical BW of 400MB/sec or 3.2 Gbps but its actual BW depends on the type of controller used.

As complexity increases so does bandwidth.

## **Types of controllers:**

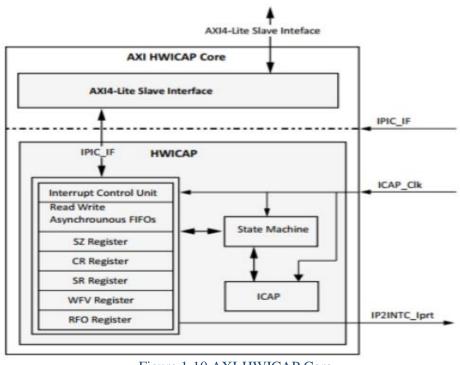

## 1) AXI-HWICAP:

This is a simple IP of a simple controller composed of an asynchronous Read & Write FIFOs, control registers and an FSM along with ICAP used for reconfiguration as shown in Figure 1-10. It has low resource utilization and low average power but it also has low throughput.

Figure 1-10 AXI-HWICAP Core

## 2) PRC:

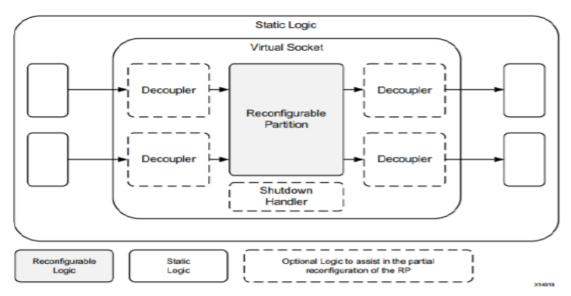

More complex than AXI-HWICAP, but it has higher throughput and achieves larger BW. It uses virtual sockets which represent reconfigurable partitions and logic blocks to isolate reconfigurable partition from static region during reconfiguration.

Figure 1-11 AXI-HWICAP Core

## **1.4.3. DPR Flow**

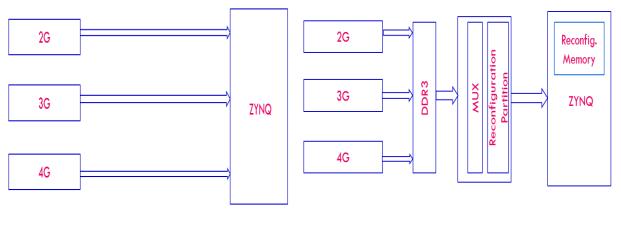

XILINX DPR flow will be introduced through implementing a multi-standard SDR system (2G, 3G, 4G, Wi-Fi, and Bluetooth) on two reconfigurable partitions (TX, RX) using HW-ICAP IP core with the help of Vivado and SDK tools.

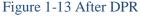

First, we have the SDR systems at the same time as shown in Figure 1-12, but that wastes hardware resources as previously discussed, so the system will be modified by removing (2G, 3G, 4G, Wi-Fi, Bluetooth) blocks and putting only one block which will be reconfigurable with the reconfigurable modules (RMs) as shown in Figure 1-13, where each RM represents one of the five chains that would be loaded into the chosen floor-planned reconfigurable partition on the FPGA

Figure 1-12 Before DPR

#### The Flow Steps:

The flow chart shown in Figure 1-14, shows the flow steps of the DPR flow where from step 1 to step 6 are performed using Vivado, while Step No. 7 SDK is used to run our software "C" code on the processor.

Figure 1-14 DPR flow steps

## **Step 1: Generate DCP for Static and RMs**

1. Read HDL codes for each RM

2. Prepare a Black Box Top Module and prepare each RM to have the same I/O ports

$\rightarrow$  Black Box Module is a module where you only define the input and output ports of the module without performing any logic. This module will be used in the static design (Reconfigurable Partition shown in Figure 1-9). This Black Box Module will be modified later in the following steps with the RMs (2G, 3G, 4G, Wi-Fi, and Bluetooth). The top module of each RM must have the same module name and same input and output ports of the Black Box Module.

3. Synthesize the static and Reconfigurable Modules separately.

$\rightarrow$  In this step the static design of the DPR system is synthesized with the black box, Each RM (Standard Chain) is synthesized in a separate project

4. Generate the DCP for each synthesized RM.

## Step 2: Load Static and one RM for the RP

1. Open the static DCP to do the floor-planning of the Reconfigurable Partition with resources which can cover the resources needed by each RM. In this case we have only one reconfigurable partition.

2. Make sure the Static block cover all the resource required by each RM. In our case the maximum resources required goes to the 4G RM, so if 4G RM fit into the Static block it would be guaranteed that other RMs will fit.

#### 3. Reset after reconfigure RM

$\rightarrow$  Partial Reconfiguration solutions from Xilinx have required a manual reset action from the user to ensure all newly reconfigured logic begins in a known state (ensure that no one standard in one column at the memory, that is stagnant from the last reconfiguration, overlaps with any other standard that is newly configured).

4. Snapping Mode

$\rightarrow$  This command is to ensure that each column achieve minimum size of LUT (400)

5. Write Checkpoint for this step

## **Step 3: Create and implement first configuration**

$\rightarrow$  In this step we will Implement a complete design (static and one Reconfigurable Module per Reconfigurable Partition) in context.

1. Read one of the RMs DCP generated in Step 1 in the Black Box cell. We start with 4G just to make sure that static block covers all the resources needed by 4G RM.

2. Implement Design using the Three Tcl command "opt\_design, place\_design, route design"

3. Write Full design Checkpoint of the implemented design, as it will be used in the generation of bitstreams in Step 6.

4. Remove Reconfigurable Modules from this design and save a static-only design checkpoint.

5. Write the DCP as this DCP represents the fully implemented and routed static design that would be used later in the implementation of other RMs.

## **Step 4: Create and implement other configurations**

$\rightarrow$  Repeat Step 3 until all Reconfigurable Modules are implemented

## Step 5: Run PR\_verify

$\rightarrow$  Run a verification utility (pr\_verify) on all configurations to verify that the static implementation and interfaces between static block and RMs are compatible.

#### Step 6: Generate bit-stream

- 1. Read Checkpoint of each RM from DDR memory

- 2. Create Full bit-stream (.bit) for each RM

- $\rightarrow$ .bit using JTAG

- 3. Create Partial bit-stream (.bin) for each RM

- $\rightarrow$ .bin using SD Card

## Step 7: Generate the Software App

- 1. Export Hardware

- 2. Launch SDK

- 3. Run C code

#### **Step 8: Test the Design**

Place the board in the SD boot mode. Copy the (BOOT.bin) file on the SD Card. Copy the partial bin files generated in the bitstreams directory on the SD card, and place the SD card in the board then test.

## **1.5. Progress of the previous years**

## 1.5.1. Internship summer 2014

This was the first attempt in implementing SDR by using DPR. Most of the chain blocks of the three different chains (3G, Wi-Fi and LTE) were eliminated to make it simpler to implement.

The chosen blocks were only implemented using VHDL & they were as follows:

- In 3G: Convolutional Encoder, Rate Half & Rate Third.

- In Wi-Fi: Convolutional Encoder, Rate Half

- In LTE: Convolutional Encoder, Rate Third.

### 1.5.2. Graduation Project 2015

In that year, the objective was to design, simulate, and implement DPR system for SDR on FPGAs which was met by investigating and modeling on two different steps.

The first step by implementing PDR system for convolutional encoders used in different communication standards 3G, LTE and WIFI (completing the internship work). Where the convolutional encoders initially not exist on the chip but stored in external memory and loaded on demand.

This PDR design for the convolutional encoder was compared to conventional convolutional encoder system, where all encoders existed on the same chip. They were compared with respect to area, power, latency and memory. The results showed that PDR implementation consumes less power and area when compared to the normal design, whereas the normal design had less memory and latency.

The second step was to implement ideal communication chains for 3G, LTE and WIFI using PDR technique where swapping occurs among different blocks for implemented encoders, modulation, FFT and DFT used in these standards. This produces a reconfigurable system that can adapt different communication standards. Using PDR shows an improvement in area and power consumption with fewer extra memory and latency when compared to the normal static implementation.

These designs of both steps were implemented on Xilinx FPGA kit XUPV5-LX110T.

### 1.5.3. Graduation Project 2016

In that year, the progress continued & the following results were achieved.

- HDL and MATLAB implementation of 3G full transmitter and some of receiver blocks.

- HDL and MATLAB implementation of WI-FI full transmitter.

- HDL and MATLAB implementation of some of LTE transmitter blocks.

- Building a test framework to Verify of HDL implementation.

- Implementation of the three chains on the FPGA (Virtex 5).

- Generating and proving the concept of multiple RPs by implementing it on a simple example.

- Debugging the FPGA results using Chipscope.

- Building a system on chip (SOC) with input and output files.

- Reducing the total area and resources needed for implementation of the three standards.

- Reducing the total power of the system as they eliminated the static and sleep mode power consumed by the idle chains.

- Reducing reconfiguration overhead by reconfigure each internal block of the chain after finishing its function. This is a kind of pipelining as there wasn't any need to wait until all frame data was generated to reconfigure each internal block of the chain.

# 1.5.4. Graduation project 2017

That year is an experience of both hardware and software skills. The verification of results had been done to make sure of the success of the work.

The final results of that year's work:

- Optimization of 3G, LTE, and Wi-Fi transmitter HDL codes.

- HDL and MATLAB implementations of 3G, LTE, and Wi-Fi Receiver.

- HDL and MATLAB implementation of 2G transmitter and receiver.

- HDL and MATLAB implementation of Bluetooth transmitter and receiver.

- Building testing environment on FPGA to test all the implemented chains.

- Building DPR system using two different controllers of ICAP (HWICAP & PRC).

# 2.1. Transmitter and Receiver separation

The transmitter and receiver of all standards were originally constructed so that, the output data of the transmitter is wired directly to the input data of the receiver with simulated attenuation and noise added to the signal, to try to imitate real channel noise and attenuation. In order to send the data via real channel, the transmitter and receiver of the standards had to be separated into two different designs with different codes, block diagrams and separate kits.

# 2.2. Overview

One standard was separated for testing purposes into transmitter and receiver with independent codes. The first challenge in the separation was to put that one standard into a separate code as this project will not apply the DPR concept, yet.

In this part we will talk about the steps taken in order to separate the transmitter and receiver, following the sequence of the data flow through the blocks.

For each transmitter/ receiver to act independently on a ZYNQ board it must have controlled access to the AXI interface and the processor, an input interface, a DMA, FIFO, data splitter and standard based block -which has the rate specified for the standard and the modulated data-.

The following part will be an overview of the whole system and its stages. Each stage will be discussed in detail later on in this chapter.

For the transmitter, the first block is the AXI-DMA which can control the memory access and the interface between memory mapped and stream type data. The input data is then entered through the input interface to adjust its clock to suit the system clock, which then passes the data on to the chosen test standard block. The output of said block is the modulated data, which has two parts; imaginary and real. Both parts are entered into the FIFO block for temporary storage.

The imaginary and real parts are combined together to form a single stream, which will then be stored in the SD card as a text file.

As for the receiver, the only change is an added block called data splitter. As mentioned before the imaginary and real parts of the data are concatenated into a single stream in the FIFO block of the transmitter, so in the receiver this procedure has to be reversed.

This is done using the data splitter block which comes after the input interface. It takes the received data and re-splits it into imaginary and real parts which are then entered into the chosen test standard block. Demodulation occurs in this block and then the sequence of the stages continues as before, in the transmitter.

Each of the blocks mentioned in the previous paragraph will be discussed in detail in the following parts of this chapter.

# 2.3. Direct Memory Access (DMA)

A DMA engine allows you to transfer data from one part of your system to another. The simplest usage of a DMA would be to transfer data from one part of the memory to another, however a DMA engine can be used to transfer data from any data producer IP block (e.g. an ADC) to a memory, or from a memory to any data consumer IP block (e.g. a DAC).

Figure 2-1 Illustration of AXI DMA use

#### **2.3.1. The DMA functions**

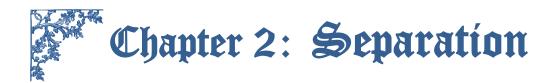

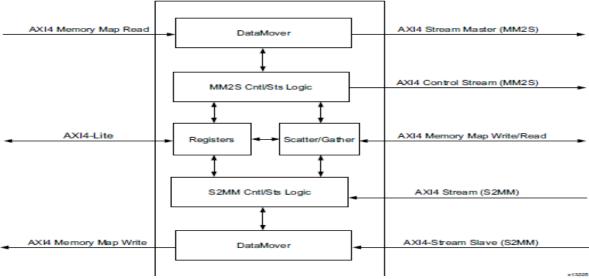

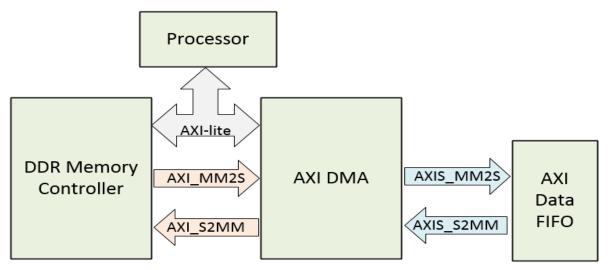

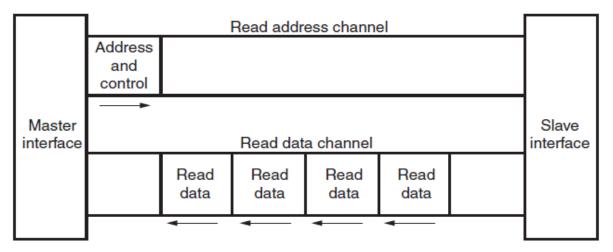

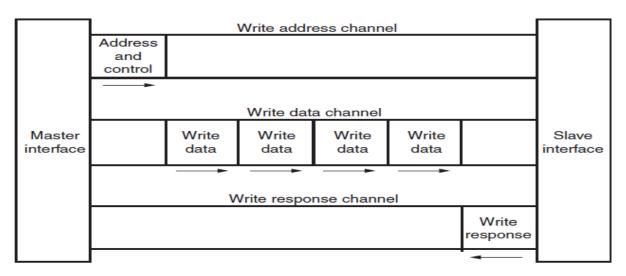

The AXI Direct Memory Access (AXI DMA) IP core provides high-bandwidth direct memory access between the AXI4 memory mapped and AXI4-Stream IP interfaces. All ZYNQ ports between PS and PL are memory mapped AXI interfaces, which needs a complicated control circuits to deal with it.

The AXI DMA can transfer high-burst data between PL and PS, by converting the data sent via the AXI4 interfaces to be sent via the AXI-stream interfaces, which is much easier to deal with.

As shown in Figure 2-1, the processor and DDR memory controller are contained within the Zynq PS. The AXI DMA and IP block are implemented in the Zynq PL. The AXI-lite bus allows the processor to communicate with the AXI DMA to setup, initiate and monitor data transfers. The AXI\_MM2S and AXI\_S2MM are memory-mapped AXI4 buses and provide the DMA access to the DDR memory. The AXIS\_MM2S and AXIS\_S2MM are AXI4-streaming buses, which source and sink a continuous stream of data, without addresses.

Its optional scatter/gather capabilities also offload data movement tasks from the Central Processing Unit (CPU) in processor-based systems. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface. Figure 2-2 illustrates the functional composition of the core. [6,7].

Figure 2-2 DMA block diagram

AXI Direct Memory Access

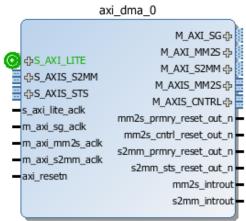

Figure 2-3 AXI DMA IP block

Figure 2-3 shows the IP block of the DMA with all its input and output signals. Primary high-speed DMA data movement between system memory and stream target is through the AXI4 Read Master to AXI4 memory-mapped to stream (MM2S) Master, and AXI stream to memory-mapped (S2MM) Slave to AXI4 Write Master. The Function of all the signals are listed in the two following tables in Figure 2-4 and Figure 2-5. [6,8]

| Signal Name                            | Interface  | Signal<br>Type   | Init<br>Status | Description                                                                                                                   |  |  |

|----------------------------------------|------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| s_axi_lite_aclk                        | Clock      | I                |                | AXI4-Lite Clock.                                                                                                              |  |  |

| m_axi_sg_aclk                          | Clock      | Ι                |                | AXI DMA Scatter Gather Clock                                                                                                  |  |  |

| m_axi_mm2s_aclk                        | Clock      | I                |                | AXI DMA MM2S Primary Clock                                                                                                    |  |  |

| m_axi_s2mm_aclk                        | Clock      | I                |                | AXI DMA S2MM Primary Clock                                                                                                    |  |  |

| axi_resetn                             | Reset      | I                |                | AXI DMA Reset. Active-Low reset. When<br>asserted Low, resets entire AXI DMA core. Must<br>be synchronous to s_axi_lite_aclk. |  |  |

| mm2s_introut                           | Interrupt  | 0                | 0              | Interrupt Out for Memory Map to Stream<br>Channel.                                                                            |  |  |

| s2mm_introut                           | Interrupt  | 0                | 0              | Interrupt Out for Stream to Memory Map<br>Channel.                                                                            |  |  |

| axi_dma_tstvec                         | NA         | 0                | 0              | Debug signals for internal use.                                                                                               |  |  |

| AXI4-Lite Interface Signals            |            |                  |                |                                                                                                                               |  |  |

| s_axi_lite_*                           | S_AXI_LITE | Input/<br>Output |                | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal.                                            |  |  |

| MM2S Memory Map Read Interface Signals |            |                  |                |                                                                                                                               |  |  |

| m_axi_mm2s_*                           | M_AXI_MM2S | Input/<br>Output |                | See Appendix A of the AAXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal.                                           |  |  |

Figure 2-4 AXI DMA signals' functions

| Signal Name                                       | Interface    | Signal<br>Type   | Init<br>Status   | Description                                                                        |  |  |  |

|---------------------------------------------------|--------------|------------------|------------------|------------------------------------------------------------------------------------|--|--|--|

| MM2S Master Stream Interface Signals              |              |                  |                  |                                                                                    |  |  |  |

| mm2s_prmry_reset_out_n                            | M_AXIS_MM2S  | 0                | 1                | Primary MM2S Reset Out. Active-Low reset.                                          |  |  |  |

| m_axis_mm2s_*                                     | M_AXIS_MM2S  | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| MM2S Master Control Stream Interface Signals      |              |                  |                  |                                                                                    |  |  |  |

| mm2s_cntrl_reset_out_n                            | M_AXIS_CNTRL | 0                | 1                | Control Reset Out. Active-Low reset.                                               |  |  |  |

| m_axis_mm2s_cntrl_*                               | M_AXIS_CNTRL | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| S2MM Memory Map Write Interface Signals           |              |                  |                  |                                                                                    |  |  |  |

| m_axi_s2mm_*                                      | M_AXI_S2MM   | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| S2MM Slave Stream Interface Signals               |              |                  |                  |                                                                                    |  |  |  |

| s2mm_prmry_reset_out_n                            | S_AXIS_S2MM  | 0                | 1                | Primary S2MM Reset Out. Active-Low reset.                                          |  |  |  |

| s_axis_s2mm_*                                     | S_AXIS_S2MM  | I                | Input/<br>Output | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| S2MM Slave Status Stream Interface Signals        |              |                  |                  |                                                                                    |  |  |  |

| s2mm_sts_reset_out_n                              | S_AXIS_STS   | 0                | 1                | AXI Status Stream (STS) Reset Output.<br>Active-Low reset.                         |  |  |  |

| s_axis_s2mm_sts_*                                 | S_AXIS_STS   | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| Scatter Gather Memory Map Read Interface Signals  |              |                  |                  |                                                                                    |  |  |  |

| m_axi_sg_*                                        | M_AXI_SG     | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

| Scatter Gather Memory Map Write Interface Signals |              |                  |                  |                                                                                    |  |  |  |

| m_axi_sg*                                         | M_AXI_SG     | Input/<br>Output |                  | See Appendix A of the AXI Reference Guide<br>(UG1037) [Ref 2] for the AXI4 signal. |  |  |  |

#### Figure 2-5 cntd' DMA signals' functions

The program code for the DMA engine is written by software into a region of system memory that is accessed by the controller using its AXI master interface. The DMA engine instruction set includes instructions for DMA transfers and management instructions to control the system.

# **2.3.2. DMAC**

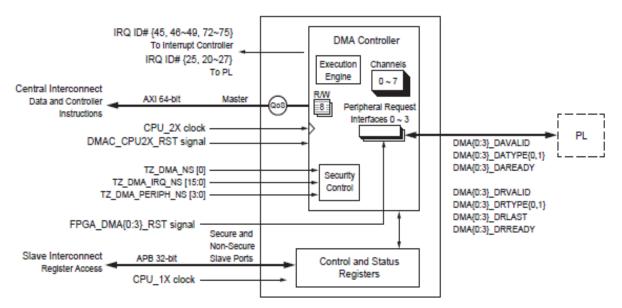

The DMA controller (DMAC) uses a 64-bit AXI master interface operating at the CPU\_2x clock rate to perform DMA data transfers to/from system memories and PL peripherals.

The DMAC is able to move large amounts of data without processor intervention. The source and destination memory can be anywhere in the system (PS or PL). The memory map for the DMAC includes DDR, OCM, linear addressed Quad-SPI read memory, SMC memory and PL peripherals or memory attached to an M\_GP\_AXI interface.

The transfers are controlled by the DMA instruction execution engine. The DMA engine runs on a small instruction set that provides a flexible method of specifying DMA transfers. This method provides greater flexibility than the capabilities of DMA controller methods.

The controller contains a multi-channel FIFO (MFIFO) to store data during the DMA transfers. The program code running on the DMA engine processor views the MFIFO as containing a set of variable-depth parallel FIFOs for DMA read and write transactions. The program code must manage the MFIFO so that the total depth of all of the DMA FIFOs does not exceed the 1,024-byte MFIFO.

The controller can be configured with up to eight DMA channels. Each channel corresponds to a thread running on the DMA engine's processor. When a DMA thread executes a load or store instruction, the DMA Engine pushes the memory request to the relevant read or write queue. See Figure 2-6 for illustration. [8]

Figure 2-6 DMAC system viewpoint

## 2.4. Input Interface

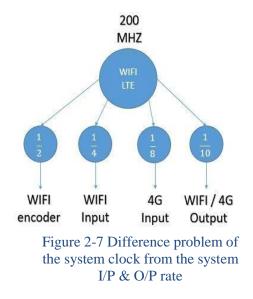

In multi-clock systems, the system may have different clock than input or output clocks such as in our case, where the system clock is different than the input rate of the system and the output rate of the system, as shown in Figure 2-7.

The traditional design is to set a DMA with a clock for input and another for output, and a third clock for the DUT itself [3]. This may cause some issues:

- a) The ARM is limited to generate 4 clocks only. Consider inserting another DUT to the system with another 3 clocks, the ARM cannot generate 7 clocks.

- b) As the number of clocks increases, the Vivado synthesize time increases.

- c) The clock routes in the FPGA floorplan are limited. As the clocks increases, the higher the possibility for time violation to occur.

So, the testing environment is to overcome these three issues by keeping the data (whether input or output) fixed for some clock cycles and by using the AXI-stream signals: Tready, Tvalid, Tlast.

The input interface controls the flow of data using the "Tready" signal. The Tready signal is an input to the DMA to say that the DUT is ready to receive signals. For example, if we want to get input data at a clock 8 times less than the system clock, we simply set the Tready to be LOW for 7 clock cycles and HIGH for only 1 clock cycle.

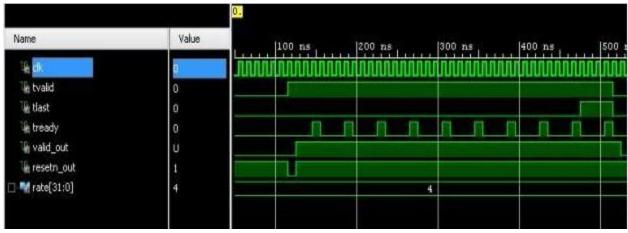

Figure 2-8 illustrates the waveform for testing the input interface in case of a rate of 4 and data length of 10.

Figure 2-8 the cycles illustrating the example

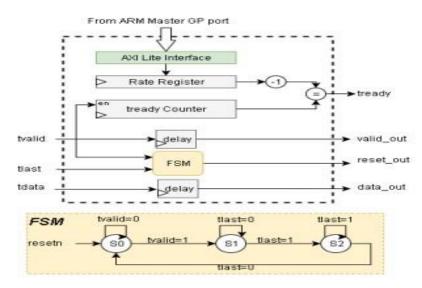

As shown in Figure 2-9, the Tready is controlled through the tready counter, while the rate itself is controlled by the ARM processor through AXI [3].

Figure 2-9 Input Interface hardware

The input interface's other function is re-setting the DUT. The idea simply is to reset the DUT at the beginning of transmitting input data, or in other words, when the "Tvalid" signal comes to HIGH. An FSM for that is shown in Figure 2-9. The "reset\_out" signal is active when the state is S1. The FSM takes one clock cycle to produce the output, which is why we used the delay elements to delay the data stream to the DUT.

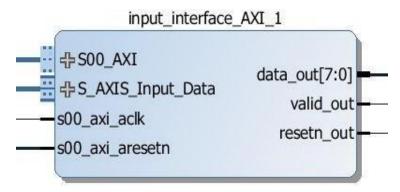

Figure 2-10 Input interface IP block

The input interface IP block illustrated in Figure 2-10, has seven signals divided into four input signals and three output signals, which will be discussed in detail. First, the S00\_AXI input signal, which is a set of communication signals between the system and the input interface. Second, the S\_AXIS\_Input\_Data input signal, which is the data coming from DDR memory and going to the connected system, remember that due to the different speeds of the connected system, the system and the memory, the input interface was needed. Third, s00\_axi\_aclk input signal, which is the input interface clock. Fourth, s00\_axi\_aresetn input signal, which is a reset signal for the input interface block. Then comes the output signals, data\_out, which is the output data from the DDR memory to the connected system at a time specified by the system. The valid\_out output signals specifies the time for the data\_out to go out.The resetn\_out signal resets the connected system.

## **2.5. Data splitter**

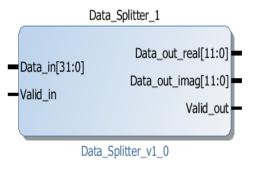

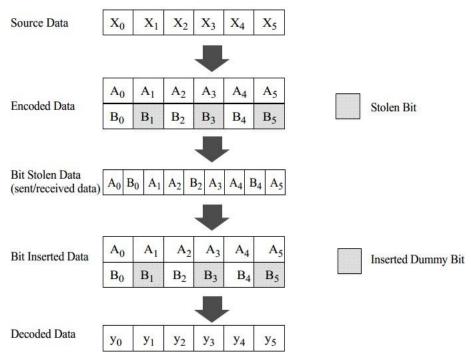

The data splitter is a custom IP block constructed for the purpose of splitting the data arriving at the receiver before entering it into the standard's IP block.

The IP block shown in Figure 2-11, has Data\_in signal, which is a 32-bit input signal from the input interface. The valid\_in signal determines when the IP block can take the data available on the bus. When valid\_in is high, this means that the data on the bus is complete and is intended for the data splitter block. After executing its sole function of splitting the input data, the block gives out three output signals, which are Data\_out\_real, Data\_out\_imag and valid out. The Data\_out signals both real and imaginary are 12-bit signals that represent the split data before concatenation. Valid\_out signal is the one that signifies that the output coming out of the block is correct and can be received by the next block, which is the standard block.

Figure 2-11 Data splitter IP block

# 2.6. WIFI standard IP block

The chosen standard for testing was the WIFI 802.11a. As it is standard procedure for any new technology or application to test it on the WIFI standard, then applying it on all other standards as the WIFI is easy to implement and works on a free band.

## 2.6.1. WIFI transmitter

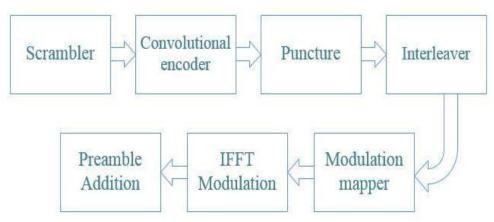

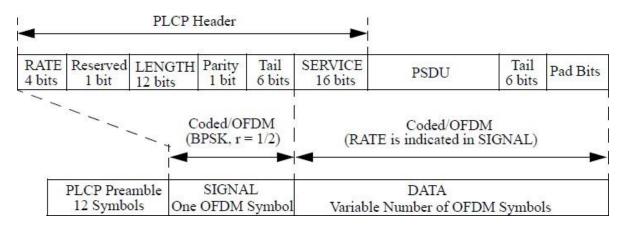

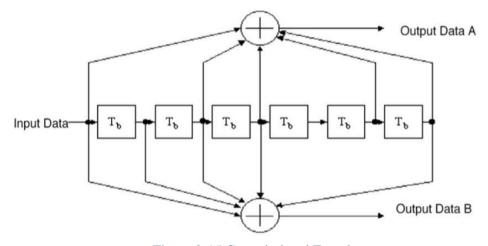

The transmitter of the WIFI consists of several blocks as shown in Figure 2-12. These blocks are the ones that do the modulation and produce the output data which is then transmitted through air by using USRPs.

Figure 2-12 WIFI transmitter functional blocks

The previous blocks will now be discussed so as to get an overall understanding of the blocks' functions and uses.

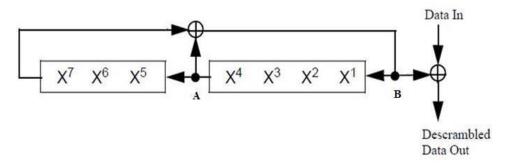

#### 2.6.1.1. Data Scrambler