### **GENERIC UVM FOR SOFT PROCESSORS**

By

Kholoud Mahmoud Ebrahim Abdulrahman Randa Ahmed Hussein Aboudeif Karim Ayman Heweidy Gad Mostafa Ayman Ibrahim Sarhan Waleed Samy Abdelhameed Taie Yasser Ibrahim Saleh Mohamed

A Graduation Project Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of Bachelor of Science

in Electronics and Communications Engineering

Under the supervision of

Associative Prof. Hassan Mustafa Dr. Khaled Salah

Faculty of Engineering, Cairo University

Giza, Egypt

July 2020

## ACKNOWLEDGEMENTS

We would like to thank our supervisors: Dr. Hassan Mostafa, for his great support, supervision and encouragement. Moreover, we are very grateful to Dr. Khaled Salah for his valuable technical support, patient guidance, enthusiastic encouragement and useful critiques throughout the project's phases. Special thanks to our Fund resources: ONE Lab. (Cairo University), ASRT (the Academy of Scientific Research and Technology) and Mentor Graphics Egypt.

# TABLE OF CONTENTS

| LIST O | F TABLES                                           | V    |

|--------|----------------------------------------------------|------|

| LIST O | F FIGURES                                          | VI   |

| LIST O | F LISTINGS                                         | VII  |

| ABSTR  | ACT                                                | VIII |

| CHPAT  | ER 1: INTRODUCTION                                 |      |

| 1.1    | Problem Definition                                 | 2    |

| 1.2    | Related Work and Contributions                     |      |

| 1.3    | Organization of the remaining chapters             | 4    |

| CHPAT  | ER 2: HISTORY AND BACKGROUND                       | 5    |

| 2.1    | UVM                                                | 5    |

| 2.2    | Soft Processors                                    |      |

| CHPAT  | ER 3: THE PROPOSED SOLUTION AND METHODOLOGY        |      |

| CHPAT  | ER 4: IMPLEMENTATION                               | 16   |

| 4.1    | Common                                             |      |

| 4.2    | testing_Xcore                                      | 44   |

| 4.3    | run                                                |      |

| CHPAT  | ER 5: AN ILLUSTRATIVE EXAMPLE                      | 54   |

| CHPAT  | ER 6: VALIDATION AND RESULTS                       | 56   |

| 6.1    | Hardware Experimental Results                      | 56   |

| 6.2    | Case Studies                                       | 58   |

| 6.2    | 1 ALU Instructions:                                | 59   |

| 6.2    | 2 Jump Instructions:                               | 61   |

| 6.2    | 3 Transaction and Memory Interaction Instructions: |      |

| 6.2    | 4 Branch Instructions:                             | 63   |

| 6.3    | Performance Evaluation                             | 64   |

| 6.4    | Comparison with Related Work                       | 64   |

| 6.5    | Limitations                                        | 65   |

| CHPAT  | ER 7: CONCLUSION AND FUTURE WORK                   | 66   |

| 7.1    | Conclusion                                         | 66   |

| 7.2    | Future Work                                        |      |

| REFERENCES | 68 | 3 |

|------------|----|---|

|------------|----|---|

# LIST OF TABLES

| Table 1 | Functional Testing Description | 3 |

|---------|--------------------------------|---|

|         |                                |   |

# LIST OF FIGURES

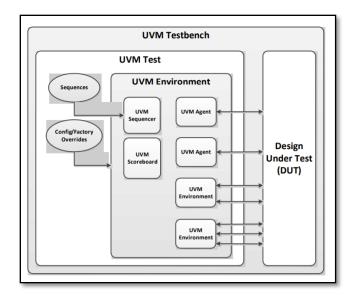

| Fig. 1 | UVM block diagram                                        |    |

|--------|----------------------------------------------------------|----|

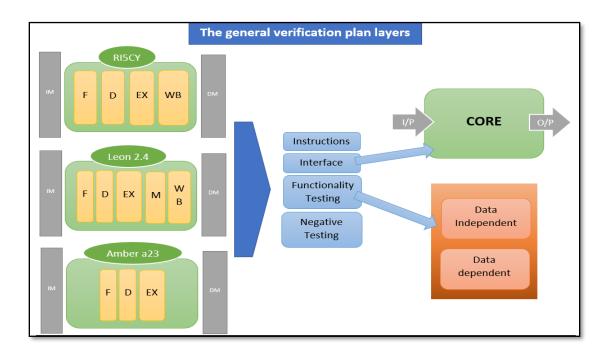

| Fig. 2 | The general verification plan layers                     | 11 |

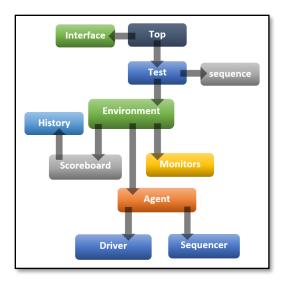

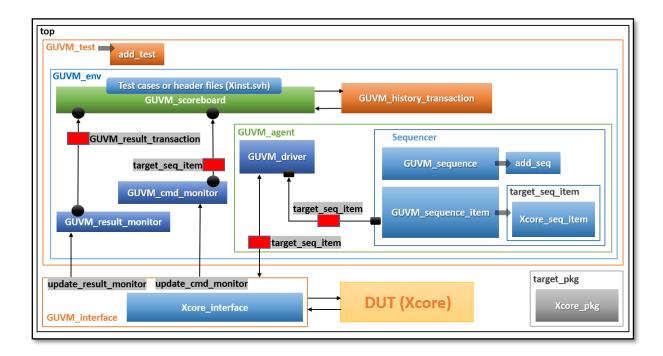

| Fig. 3 | The generic UVM test bench hierarchy.                    | 14 |

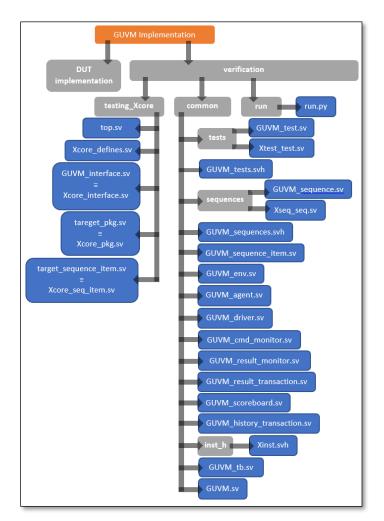

| Fig. 4 | The generic UVM implementation.                          | 16 |

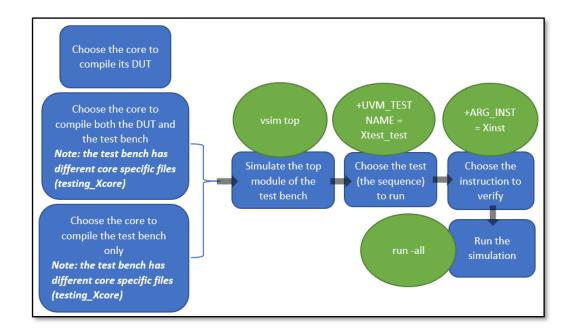

| Fig. 5 | The flow of the python script (run file)                 | 52 |

| Fig. 6 | Generic UVM for Soft Processors Test Bench Architecture. | 55 |

# LIST OF LISTINGS

| The parent test file (GUVM_test).                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A child test file (add_test).                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

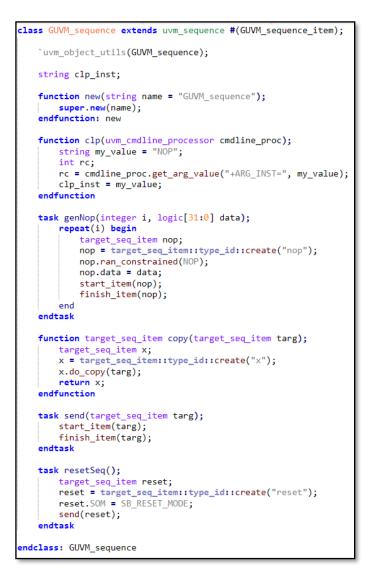

| The parent sequence file (GUVM_sequence)                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A child sequence file (add_seq).                                        | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

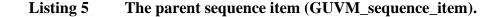

| The parent sequence item (GUVM_sequence_item).                          | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The parent sequence item: do_compare(), do_copy() and, convert2string() | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

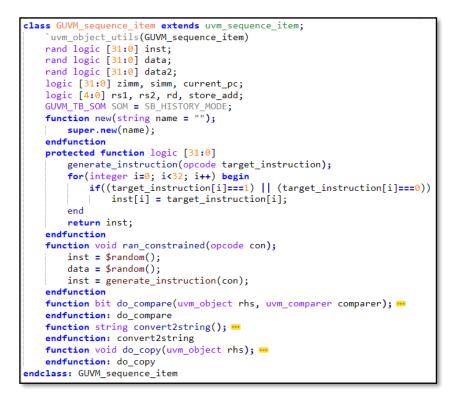

| The generic environment (GUVM_env).                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

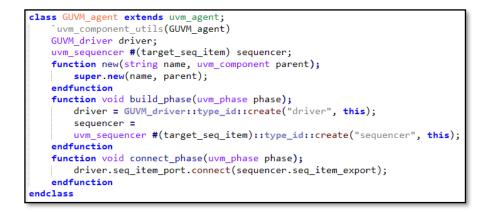

| The generic agent (GUVM_agent)                                          | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

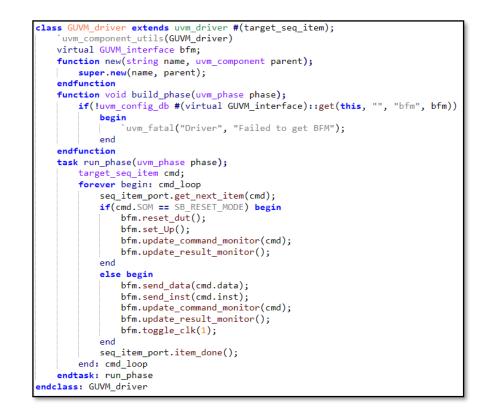

| The generic driver (GUVM_driver)                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The generic command monitor (GUVM_cmd_monitor)                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

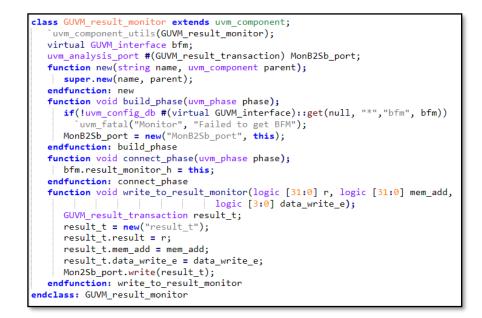

| The generic result monitor (GUVM_result_monitor)                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

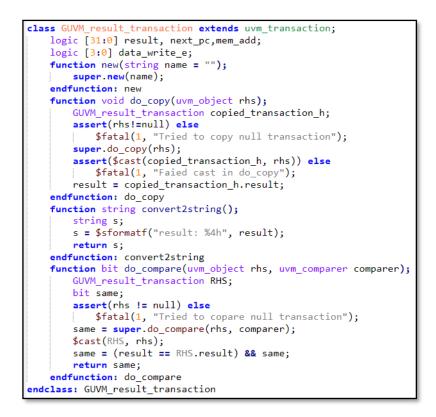

| The generic result monitor (GUVM_result_monitor)                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The generic scoreboard (GUVM_scoreboard)                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

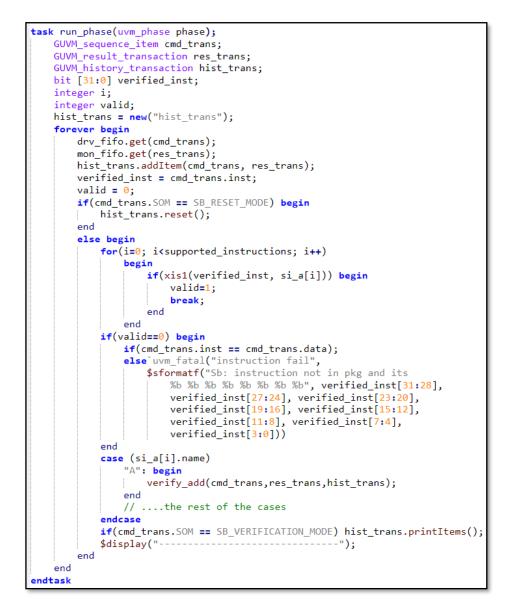

| The run phase of the generic scoreboard (GUVM_scoreboard)               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

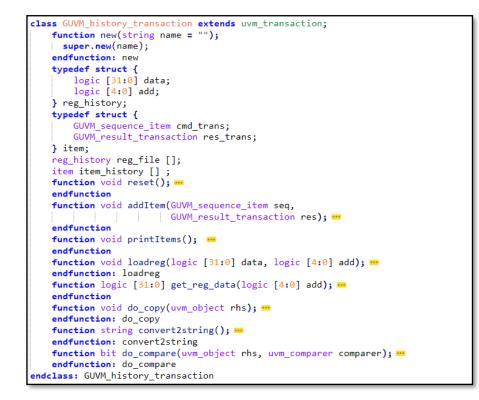

| The generic history transaction (GUVM_history_transaction)              | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

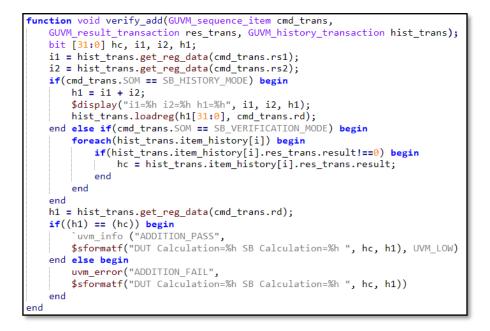

| The header file of the addition instruction                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Contents of "GUVM.sv" file.                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The top module of the test bench                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

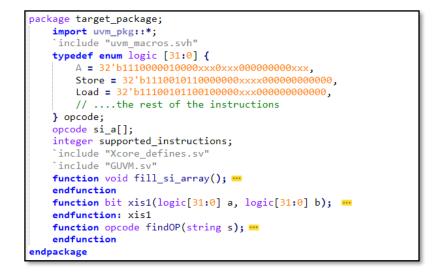

| The Xcore/target package (target_pkg).                                  | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The functions of the target package (target_pkg)                        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

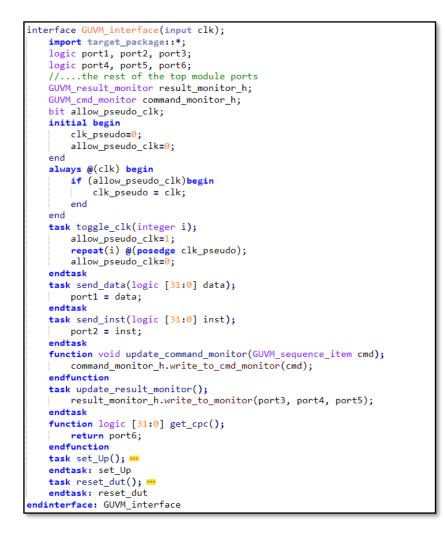

| The core (DUT) interface (GUVM_interface)                               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

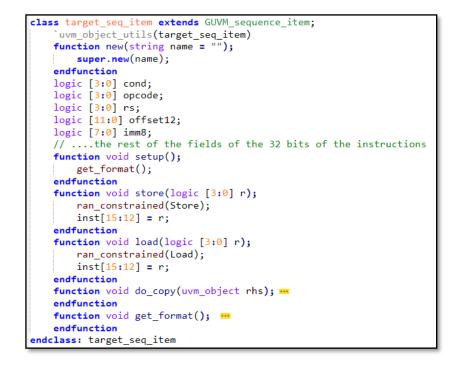

| The target sequence item (target_seq_item).                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UVM report summary for add test                                         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| First part of the detailed report for store half word test              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The dynamic register file saved                                         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| History table contents for add test.                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

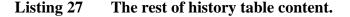

| The rest of history table content                                       | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Output of add with carry test                                           | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Test bench results for jump and link instruction                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Test bench results for load unsigned byte instruction                   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Test bench results for branch if equal                                  | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                         | A child test file (add_test)<br>The parent sequence file (GUVM_sequence)<br>A child sequence file (add_seq)<br>The parent sequence item (GUVM_sequence_item).<br>The parent sequence item: do_compare(), do_copy() and, convert2string()<br>The generic environment (GUVM_env).<br>The generic agent (GUVM_dagent).<br>The generic driver (GUVM_driver).<br>The generic command monitor (GUVM_cmd_monitor).<br>The generic result monitor (GUVM_result_monitor).<br>The generic result monitor (GUVM_result_monitor).<br>The generic coreboard (GUVM_scoreboard).<br>The generic scoreboard (GUVM_scoreboard).<br>The generic history transaction (GUVM_history_transaction).<br>The header file of the addition instruction.<br>Contents of "GUVM.sv" file.<br>The top module of the test bench.<br>The Xcore/target package (target_pkg).<br>The functions of the target package (target_pkg).<br>The functions of the target package (target_pkg).<br>The top the detailed report for store half word test.<br>The dynamic register file saved.<br>History table contents for add test.<br>The rest of history table content.<br>Output of add with carry test<br>Test bench results for jump and link instruction.<br>Test bench results for load unsigned byte instruction. |

### ABSTRACT

In the modern era of CPU complexity advancements, Processor verification has always been an ever-increasing challenge. The gap between what a verification plan can offer nowadays and the current technology requirements is constantly widened. Despite of varies efforts on perfecting "Golden-verification-models" during the design phase, and adoption of object-oriented programming into the whole process; numerous industry experts still consider solo verification test benches as an extreme, time-consuming barricade that leads to a longer time-to-market and a questionable continuity of the current verification process. The Universal Verification Methodology (UVM), has come in action as a literal savior to the whole verification community, by offering a merge between SystemVerilog and SystemC into one environment that is completely standardized, constrained, and reusable, allowing a powerful verification methodology to a wide range of design sizes and types. The main contribution that this work introduces is implementing a generic UVM. In other words, building one verification environment that can be used to accommodate many RTL designs (Soft Processors), having not only different Instruction Set Architectures (ISAs) of the same categories-, however additionally different techniques, and mechanisms handling the pipeline infrastructures. The proposed generic UVM (GUVM) structure permits the targeted user to attach any soft processor (core) having nearly the same microarchitecture to the proposed test bench, and to monitor both: CPU internal behavior and the complete flow of all supported instructions.

Keywords—UVM, SystemVerilog, Generic, Soft Processors, Cores, Verification Environment, Functional Verification, Simulation-based Verification, Instruction-based

VIII

Verification, Core-independent Verification.

#### CHPATER 1: INTRODUCTION

Design Verification is simply the process of checking that a given design parameter correctly implements the target, specifications, and the required functionality [1].

Traditionally, 70% of a chip development cycle is dedicated to design verification. Based on that, the verification to design team ratio ranges from 2:1 to 3:1; that major overhead in the whole process lead to a new trend in the verification arena: striving towards *standardized*, and *reusable* test benches. That is when newer methodologies have been introduced like the Open Verification Methodology (OVM) and the Verification Methodology Manual (VMM), both have been actually fine for a while, however the industry is in need of a non-proprietary approach; thus finally in 2011, major technology giants joined together through Accellera and created the Universal Verification Methodology (UVM) [2].

UVM has opened new horizons in the verification world, and its highly configurable features have made the *generic* proposal really possible; as the old saying goes: "You can never go wrong with an object-oriented-based line of code". Normally a System on Chip (SOC) can be verified effectively using a simulation testbench that provides data to the SoC inputs and checks resulting data at the SoC outputs. The problem is that running all the possible testing scenarios is computationally impossible. On the other hand, a modern testbench-based verification environment automatically generates randomized stimulus for the SoC inputs under control of user-specified constraints and checks the results of each test automatically. UVM is the best verification approach that has been created to develop

constrained-random testbenches in a uniform fashion and to permit limited reuse of testbench components [3].

In this work, an attempt to extend this reusability concept furthermore, by applying the same UVM environment to a plethora of different Designs Under Test (DUTs) implementation, with completely different architectures and some limitations on the common functions among different DUTs.

### **1.1 Problem Definition**

It becomes possible for electronic system designers to assemble complete systems-onchips due to the ever-increasing advances in the integrated circuit technology. At the same time, shrinking time-to-market leaves a small room for errors in the design development. Therefore, the verification process with all its stages (pre-silicon verification, post-silicon validation and runtime verification) has become one of the main tasks during the design-to-fabrication process, Thus, bugs are detected and fixed at early design flow stages [3].

Both design and verification nowadays are pushing towards reusable environments, and correspondingly the need of a standalone, and pre-verified verification infrastructure has arisen, to ensure that the verification step is not the bottleneck of the design flow.

UVM is being used as it has improved verification quality due to the constrained random verification. Test benches are reusable as verification components or agents get instantiated within a verification environment inside a project, and they may require some modification to suit the requirements of this verification environment. In addition to that, the overall verification environment could be used and modified according to the requirements of a certain test [2].

The problem of verifying soft processors using separate modified verification environments or different approaches still exists, and does cost the product cycle a long computational time and effort to get into the market. As a result, there is a great demand for a reusable generic environment used to verify soft processors with as minimum modification as possible; in order to save effort, time and cost.

#### **1.2 Related Work and Contributions**

For the best knowledge of the authors, this is the first Contribution in verifying different soft processors (cores) using only one generic and reusable UVM (the same UVM test bench without any tweaking); all the related works are based on the idea of implementing a UVM test bench to verify only one DUT (it can be reused however after tweaking the main components of the test bench itself).

In this work, the objective is to design and implement only one generic UVM that is used to verify the functionality of different soft processors (cores). These different cores are based on different instruction set architectures (ISAs), and they have different infrastructures and specifications such as, the number of the pipeline stages, and the behavior of the cache memories.

The proposed generic UVM attempts to prove this objective are on three open-source cores:

- RI5CY core, based on RISC-V ISA with four pipeline stages.

- LEON 2.4 core, based on SPARC-V8 ISA with five pipeline stages.

• Amber a23 core, based on ARM-V2a ISA with three pipeline stages.

The generic UVM proposed, can additionally be used to verify any similar soft processor based on one of the three previously mentioned ISAs, and has nearly the same specifications.

## **1.3** Organization of the remaining chapters

In Chapter 2, the history and the background about the UVM in general and the three proposed open-source cores are discussed. In Chapter 3, the proposed solution and methodology are explained. In Chapter 4, the proposed implementation is investigated in details, followed by an illustrative example in Chapter 5. in Chapter 6, the validation and the results of the proposed work are presented. Finally, in Chapter 7, conclusion and future work directions are drawn.

### CHPATER 2: HISTORY AND BACKGROUND

### **2.1 UVM** [4]-[12]

The most common term in verification is known as *functionality testing* or *functional verification* which is the process of demonstrating functional correctness of a processor design with respect to its specifications, this process is preceded by creating a verification plan that defines: which properties and functionalities need to be verified, different methods and approaches that will be used in processor testing, the expected behaviour of an appropriate design, defining functional coverage models and functional specifications of the verification, and finally the testing strategy; such major decisions must be taken in the verification planning phase [4].

Due to complex aspects of an IC design, these processes tend to be very challenging; during the past decade alone, average time spent by verification engineers to verily the complete functionality of their designs wasted more than 60 percent of the total design time. Even developers of smaller chips and FPGAs designs are facing difficulties with former verification approaches. The wanted goal of verification is becoming more difficult to achieve using conventional verification techniques, and hence solving this issue requires a detailed review of common testing methodology.

Directed testing was more convenient for testing single functionalities, however, it is hard to hit more complex scenarios using only directed testing. On the other hand, constrained-random verification (CRV) can be very efficient in tackling processor verification challenges, such as: complex instruction sets, multiple pipeline-stages, in order or out of order execution strategies, instruction parallelism, and multi precision operations. The most important module of a CRV environment is the test-case generator, which plays a very significant role in most of the recent approaches towards developing automated processor verification environments. A test-case generator generates a large set of valid test cases in a pseudo-random way, controlled and guided by constrained randomness. The development of such test generators has started to get the attention of functional verification engineers, and researchers since the early 2000s. However, the development of these generators has been categorized as a software problem due to poor and weak features of Hardware Description Languages (HDLs) available back then in terms of verification and software, like Verilog and VHDL [4].

However, recent efforts have been spent towards the utilization of SystemVerilog features as a Hardware Verification Language (HVL) to improve stimulus generation quality; and then UVM gradually dominated the verification world, as it covers these needs. UVM is a powerful verification methodology that was designed to be able to verify a variety of different design sizes and design types that could be in Verilog, SystemVerilog, VHDL, and SystemC code. It is an open source SystemVerilog library allowing creation of flexible, reusable verification components and assembling powerful test environments utilizing constrained random stimulus generation and functional coverage models [8]. It is based upon the three C's of random verification: [12]

Checkers: As long as the stimulus is automated, in addition you have to write selfchecking test benches in SystemVerilog.

- 2- Coverage: The question "Are we done yet?" have to be answered, as in addition is known as "Functional Coverage", it is about recording the progress during a verification run and identifying how thoroughly the design have been exercised.

- 3- Constraints: What if holes have been covered, or if the design have not been exercised thoroughly enough. That is where constraints come into play, the constraints have to be increased on those random vectors in order to increase test coverage.

A UVM test bench is composed of verification components that are encapsulated, reusable, ready-to-use, and configurable elements; checking an interface protocol, a design sub-module, or a full system. The architecture of each component is logical. It includes a complete set of elements enabling the stimulation, check and collection of coverage information related to the specific protocol or design. This test bench instantiates the Design under Test module and the UVM Test class, then configures all connections between them. Module-based components are instantiated under the UVM test bench as well. The UVM Test is dynamically instantiated at run-time, allowing the UVM test bench to be compiled once and run with many different tests. All complex test benches may be architected as shown in Fig. 1 with little or more modification depending on the design complexity. The proposed implementation will be explained in details during Chapter 3.

Fig. 1 UVM block diagram.

The overall verification environment can be tweaked by individual separately-written tests. It is typically a small piece of UVM code and that test would then customize the behavior of the complete verification environment in order to direct it in some way to try to test some particular feature of the DUT (interesting case).

### **2.2 Soft Processors** [13]-[24]

A soft microprocessor (or a soft core) is considered Register transfer logic (RTL) code that describes a specific design and capable of executing some sort of an instruction set. This code can then be synthesized into a net list and mapped onto a programmable logic such as FPGA. Unlike hard processors which are physically implemented as a structure in silicon. The main advantage of soft processors is the higher configurability, and adjustability, as all features are written in code and thus its instruction set could be easily extended, modified and altered; on the other hand, increasing those capabilities will result in much more waste of resources and FPGA area, in addition to consuming more power while running at lower speeds as they are limited by fabric speed. Nonetheless, some soft processors RTL is open source for research and development purposes, and that aligns perfectly with the used DUTs' choices as follows:

- 1- <u>RISCY Core:</u> A 4-stage 32-bit in order processor core based on RISC-V ISA under Solderpad license. In addition, some extensions were added to support embedded processing, hardware loops and advanced ALU instructions that are not included in standard RISC-V. It was first introduced in 2013 by Luca Benini as a collaboration between the University of Bologna and Zurich; this research work involved a team of 50-60 members with concentration on programmable systems that need to be flexible, scalable and does not waste energy. This core is fully written in Verilog and uses GCC as a compiler, with native support for interrupt and hardware synthesis. The core under consideration runs at 500 MHz, can interface with all basic peripherals like SPI, I2C, UART & JTAG Debug interface, and interfaces with both AXI/APF for high speed and low speed peripherals respectively [20], [21], and [22].

- 2- Leon 2.4: A 5-stage 32-bit processor core based on SPARC V8 ISA under GPL license. This project was initiated by the European Space Agency (ESA) in 1997 to develop a high-performance processor for their projects and future requirements. Later, it was developed even more for embedded applications with some features like: support for multi-core systems, separate data and instruction caches, hardware-based multiplier and divider, a memory management unit, interrupt controller, and finally an on-chip AMBA bus. This core is entirely written in VHDL, and in addition support both FPGA and ASIC synthesis [23].

3- <u>Amber a23:</u> A 3-stage 32-bit processor core based on ARM V2a ISA under LGPL license and hosted on the OpenCores website. It was developed in Verilog2001 and optimized for FPGA synthesis. Amber 23 is capable of 0.75 DMIPS per MHz, has a unified instruction and data cache, and communicates its data through wishbone bus interface. It can boot a Linux 2.4 kernel and its project does include a pre-made FPGA initialization, as well as peripheral support for UART, timer controller, interrupt controller, a test module and an Ethernet MAC [24].

## CHPATER 3: THE PROPOSED SOLUTION AND METHODOLOGY

Building a generic environment to verify different soft processors becomes a great demand nowadays, however to build an efficient and professional test bench, proper verification steps must be done, and followed in an effective manner to get the required results. Therefore, the proposed solution steps are as following:

- Understanding the design specifications: studying the architecture of the desired DUT to be verified using the available data sheets and documentations. The case study here is on the three different open-source cores; those are previously mentioned before [25].

- 2) **Creating a verification plan:** based on the study done on the DUTs, a general verification plan is set, which consists of four main layers as shown Fig. 2:

Fig. 2 The general verification plan layers

- <u>*The instructions layer:*</u> Where the specifying of instructions needed to be verified (functional verification) for each core (What to verify?).

- <u>*The interface layer:*</u> Where the determination of the I/O ports of the core in a blackbox approach (I/O ports of the top-level module of the core).

- <u>The functionality testing layer:</u> Where the instructions needed to be verified are divided in a table into functions, then each function is divided into a group of instructions with different types, followed by a description of the test applied on each instruction in this group with the coverage bits detailed division. An example of the functionality testing table for the "add" instruction is shown in TABLE I (How to verify?) [26], [27].

- <u>The Negative testing layer</u>: In which the core is fed with invalid input data to check if it is behaving as expected or not, for invalid input data; whether the test bench shows any error message when it is supposed to and does not show any error message when it is not supposed to. In other words, checking that to what extent the core keeps itself stable in different situations for invalid input data for which it is not designed.

- 3) **Identifying the verification methods required:** In the proposed solution, the Simulation Based Verification is used, where constrained-random stimuli are generated for the design under test, then a golden reference (the scoreboard) is used to generate the expected output, which is then compared to the actual output determining the validity of the design functionality. (What should be?)

- 4) **Building the verification environment** (this part will be covered in an abstraction level in the next section of this chapter, and in great details in Chapter 4).

5) **Executing the plan**: Developing and running the tests, finding bugs, and debugging to make sure that the bug is a flaw in the DUT, not a problem with the verification environment itself.

| Func.  | Inst. | Cores                                                                                                   |                                                                                                                                                                                 |                                                                                                         |

|--------|-------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|        |       | Leon 2.4                                                                                                | Ri5cy                                                                                                                                                                           | Amber a23                                                                                               |

| Arith. | Add   | Testing that the<br>output register<br>x[rd] has the result<br>of adding register<br>x[rs2] and x[rs1]. | Testing that the<br>output register<br>x[rd] has the result<br>of adding the<br>contents of<br>register x[rs2] and<br>register x[rs1].<br>Arithmetic<br>overflow is<br>ignored. | Testing that the<br>output register<br>x[rd] has the<br>result of adding<br>register x[m] and<br>x[rm]. |

|        |       | *Inst[31:30]→                                                                                           | * Inst[31:25]→                                                                                                                                                                  | * Inst[31:28]→                                                                                          |

|        |       | [2'b10]                                                                                                 | [7b'0000000]                                                                                                                                                                    | [4'bxxxx]                                                                                               |

|        |       | *Inst[29:25]→                                                                                           | *Inst[24:20]→                                                                                                                                                                   | *Inst[27:20]→                                                                                           |

|        |       | [5'bxxxxx]                                                                                              | [5'bxxxxx]                                                                                                                                                                      | [8'b00001000]                                                                                           |

|        |       | *Inst[24:19]→                                                                                           | *Inst[19:15]→                                                                                                                                                                   | *Inst[19:16] <b>→</b>                                                                                   |

|        |       | [6'b'000000]                                                                                            | [5'bxxxxx]                                                                                                                                                                      | [4'bxxxx]                                                                                               |

|        |       | *Inst[18:14] <b>→</b><br>[5'b'xxxxx]                                                                    | *Inst[14:12]→<br>[3'b000]                                                                                                                                                       | *Inst[15:12] <b>→</b><br>[4'bxxxx]                                                                      |

|        |       | *Inst[13]→                                                                                              | *Inst[11:7]→<br>[5'bxxxxx]                                                                                                                                                      | *Inst[11:4]→<br>[8'b0000000]                                                                            |

|        |       | [1'b0]<br>*Inst[12:5] <b>→</b>                                                                          | *Inst[6:0] <b>→</b><br>[7'b0110011]                                                                                                                                             | *Inst[3:0]→<br>[4'bxxxx]                                                                                |

|        |       | [8'b00000000]                                                                                           |                                                                                                                                                                                 |                                                                                                         |

|        |       | *Inst[4:0]→                                                                                             |                                                                                                                                                                                 |                                                                                                         |

|        |       | [5'bxxxxx]                                                                                              |                                                                                                                                                                                 |                                                                                                         |

Table 1Functional Testing Description.

The main goal of the proposed methodology is to obtain a generic verification environment using a generic UVM test bench to verify different soft processors. Fig. 3 shows the hierarchy of the proposed generic UVM test bench (this hierarchy will be explained and covered in details in Chapter 4).

Fig. 3 The generic UVM test bench hierarchy.

The flow of the hierarchy works as following:

- The top module instantiates the test and the interface.

- The test instantiates the environment and the sequence (which is extended from the parent sequence)

- The environment instantiates the agent, the scoreboard, and the monitors.

- The scoreboard instantiates the history.

- The agent instantiates the sequencer and the driver.

The proposed verification approach allows the designated user to use the proposed generic UVM with any soft processor of the three previously mentioned open-source cores (or any available core with the same instructions and with a similar mechanism) after attaching, and connecting a few things to the test bench:

- 1. The DUT itself (RTL implementation code).

- 2. **The Core Package** (and its related files): Includes all the core instructions, the format mapping of each one of the instructions, and some core specific defines.

- 3. **The Core Interface:** Includes input and output ports for the top-level-module of the core, in addition to pre-defined functions that the driver uses to drive instructions or data to the DUT.

- 4. **The Sequence:** Where the determination of the sequence, and behavior of how to verify the instructions. This child sequence inherits a parent shared, and pre-programmed sequence file (in the sequencer).

- 5. **Running the Test file**: Every child sequence has its own test to be instantiated, and triggered.

- 6. Header files connected to the scoreboard contain the test cases of the instructions needed to be verified that are included in the core package.

## **CHPATER 4: IMPLEMENTATION**

In this chapter, the implementation of the proposed generic UVM (GUVM) environment will be discussed in details.

Fig. 4 shows the hierarchy of the proposed implementation.

Fig. 4 The generic UVM implementation.

As the hierarchy consists of two main folders as following:

• **DUT implementation:** The RTL implementation code of the DUT needed to be verified (Xcore).

- Verification: Where the actual code of the test bench is organized into three main subfolders as following:

- *common:* Where the main generic components of the test bench are instantiated and triggered.

- *testing\_X*: Where the DUT specific files are instantiated and triggered.

- *run:* Where running the test bench using a python scripts take place with a great flexibility.

Following, the contents of each sub-folder will be discussed in details:

### 4.1 common:

It consists of a number of files and sub-sub-folders connected to each other to form the generic components of the proposed test bench:

- **a.** <u>tests:</u> a sub-sub-folder contains a number of files (child tests) to run with the proposed test bench such as, "add\_test.sv", all these child tests are extended from a parent test: "GUVM test.sv":

- 1. <u>"GUVM\_test.sv"</u>: Where the parent test (GUVM\_test) is extended from the (uvm\_test) base class, it is registered with the UVM factory, then the constructor of the new class is declared. The generic environment (GUVM\_env), the generic parent sequence (GUVM\_sequence), and the UVM command line processor class (uvm\_cmdline\_processor) are declared to be instantiated and created at the build phase as shown in Listing 1. Then the objection has been raised at the run phase to let (uvm\_cmdline\_processor) get the required arguments, and start the sequencer responsible for sending the transactions or the sequence items to the driver (GUVM\_driver). More details related to the arguments of

(uvm\_cmdline\_processor) are in Section 4.1.b.1, and more details related to the sequencer, and the generic driver (GUVM\_driver) are in Section 4.1.e, and Section 4.1.f.

Listing 1 The parent test file (GUVM\_test).

```

class GUVM_test extends uvm_test;

`uvm_component_utils(GUVM_test);

GUVM_env env_h;

GUVM_sequence generic_sequence_h;

uvm_cmdline_processor cmdline_proc;

function new(string name = "GUVM_test", uvm_component parent);

super.new(name, parent);

endfunction: new

function void build_phase(uvm_phase phase);

cmdline_proc = uvm_cmdline_processor::get_inst();

env_h = GUVM_env::type_id::create("env_h",this);

generic_sequence_h = GUVM_sequence::type_id::create("generic_sequence_h");

endfunction: build phase

task run phase(uvm phase phase);

phase.raise_objection(this);

$display("test have started ");

generic_sequence_h.clp(cmdline_proc);

generic_sequence_h.start(env_h.agent.sequencer);

phase.drop_objection(this);

endtask: run_phase

endclass: GUVM test

```