## Comparative Analysis for Power Computation and Simulation Time Between RTL and TLM

By

Ahmed Mohamed Mahmoud Abdulhamid Khalil

Ahmed Mohamed Mahmoud Aly

Ahmed Nagy Mohamed Mohamed El-Zeiny

Adham Hassan Rageh

AbdelRahman Saeed Anwar

Karim Mohamed Abo El-Makarem

Under supervision of

Dr, Hassan Mostafa

Dr, Magdy El-Moursy

A Graduation Project Report Submitted to the Faculty of Engineering at Cairo University

in Partial Fulfillment of the Requirements for the

Degree of

Bachelor of Science

in

Electronics and Communications Engineering

Faculty of Engineering, Cairo University

Giza, Egypt

July 2017

# **Table of Contents**

# Chapter 1: Contents

| List of Tablesv                             |

|---------------------------------------------|

| List of Figuresvi                           |

| List of Symbols and Abbreviations           |

| Acknowledgmentsix                           |

| Abstractx                                   |

| Chapter 2: Introduction                     |

| 2.1 Problem Overview                        |

| 2.2 Solution                                |

| 2.3 Work Flow                               |

| Chapter 3: Zynq-7000 All Programmable SoC   |

| 3.1 Introduction                            |

| 3.2 Block Diagram                           |

| 3.3 GPIO7                                   |

| 3.3.1 Features                              |

| 3.3.2 Block Diagram7                        |

| 3.3.3 Functional Description                |

| 3.3.4 EMIO Signals10                        |

| 3.3.5 Interrupts11                          |

| 3.4 GIC12                                   |

| 3.4.1 Block Diagram                         |

| 3.4.2 Functional Description14              |

| 3.4.3 Interrupt Sensitivity and Targeting15 |

| 3.4.4      | Interrupt Prioritization and Handling10  | 5 |

|------------|------------------------------------------|---|

| 3.5 UA     | ART17                                    | 7 |

| 3.5.1      | Features                                 | 7 |

| 3.5.2      | Block Diagram18                          | 8 |

| 3.5.3      | Functional Description                   | 9 |

| 3.5.4      | Status and Interrupts2                   | 5 |

| 3.5.5      | Block Flow Building                      | 7 |

| 3.6 SP     | I                                        | 2 |

| 3.6.1      | Features                                 | 2 |

| 3.6.2      | Block Diagram                            | 3 |

| 3.6.3      | Functional Description                   | 5 |

| 3.7 I2C    | C40                                      | 0 |

| 3.7.1      | Features                                 | 1 |

| 3.7.2      | Block Diagram42                          | 2 |

| 3.7.3      | Functional Description44                 | 4 |

| 3.7.4      | Modes of Operation4                      | 7 |

| 3.8 DN     | /IA                                      | 2 |

| 3.8.1      | Features                                 | 5 |

| 3.8.2      | Block Diagram                            | 5 |

| 3.8.3      | Functional Description                   | 8 |

| 3.8.4      | Events and Timing Diagram65              | 5 |

| Chapter 4: | Simulation, Synthesis, and Integration72 | 2 |

| 4.1 Sir    | nulation72                               | 2 |

| 4.1.1      | GPIO72                                   | 2 |

| 4.1.2      | GIC                                      | 5 |

| 4.1.3      | UART                                     | 5 |

| 4.1.4      | SPI                                      | 7 |

| 4.1     | .5   | I2C                              | 3 |

|---------|------|----------------------------------|---|

| 4.2     | Syn  | thesis78                         | 3 |

| 4.2     | .1   | Logic Synthesis                  | 9 |

| 4.2     | .2   | Synthesis Problems               | 1 |

| 4.3     | Inte | gration82                        | 2 |

| 4.3     | .1   | Zynq Blocks Integration          | 3 |

| 4.3     | .2   | Scenarios                        | 1 |

| 4.3     | .3   | Integration Problems             | 5 |

| Chapter | 5:   | Transaction Level Power Modeling | 7 |

| 5.1     | Pow  | ver Modeling for TLM87           | 7 |

| 5.2     | TLF  | PM Methodology                   | 3 |

| 5.3     | Cor  | relation Matrix90                | ) |

| 5.4     | Vist | ra92                             | 2 |

| Chapter | 6:   | Results and Conclusion           | 5 |

| 6.1     | Res  | ults of each block95             | 5 |

| 6.2     | Ove  | erall System results97           | 7 |

| 6.3     | Con  | clusion                          | ) |

| Referen | ces  |                                  | ) |

## List of Tables

| Table 1 GPIO Interrupt signals                       | 12 |

|------------------------------------------------------|----|

| Table 2 PPI Interrupt Requests IDs                   | 14 |

| Table 3 SPI Interrupt Requests IDs                   | 15 |

| Table 4 Auto/Manual SS and Start                     | 36 |

| Table 5 Clock Phase and Polarity Parameters          | 39 |

| Table 6 Operations of the DMA state machine          | 63 |

| Table 7 UART Scenarios                               | 76 |

| Table 8 GPIO results                                 | 95 |

| Table 9 SPI results                                  | 95 |

| Table 10 I2C results                                 | 96 |

| Table 11 Power Calculation results of overall system | 99 |

| Table 12 Simulation Time results of overall system   | 99 |

# List of Figures

| Figure 2-1. Flow of the extraction of power parameters        | 3   |

|---------------------------------------------------------------|-----|

| Figure 3-1. Block Diagram of Zynq-7000                        | 6   |

| Figure 3-2. GPIO main banks                                   | 8   |

| Figure 3-3. GPIO Functional Block Diagram                     | 8   |

| Figure 3-4 GIC Block Diagram                                  | .13 |

| Figure 3-5 UART System block                                  | .19 |

| Figure 3-6 UART Block Diagram                                 | .19 |

| Figure 3-7 Baud Rate Generator                                | .20 |

| Figure 3-8 Default BDIV Receiver Data Stream                  | .22 |

| Figure 3-9 UART Mode Switch for TxD and RxD                   | .24 |

| Figure 3-10 Interrupts and status signals                     | .25 |

| Figure 3-11 UART RxFIFO and TxFIFO Interrupt                  | .27 |

| Figure 3-12 TX state diagram                                  | .29 |

| Figure 3-13 RX state diagram                                  | .29 |

| Figure 3-14 Controllers, FIFOs and Baud Rate generator        | .31 |

| Figure 3-15 SPI system block diagram                          | .33 |

| Figure 3-16 SPI functional block diagram                      | .34 |

| Figure 3-17 Rx and Tx FIFO interrupts                         | .39 |

| Figure 3-18 The clock phase parameter and the state of the SS | .40 |

| Figure 3-19 I2C Block Diagram                                 | .42 |

| Figure 3-20 I2C Device Connections                            | .44 |

| Figure 3-21 I2C Transaction waveform                          | .46 |

| Figure 3-22 I2C Clock Division                                | .47 |

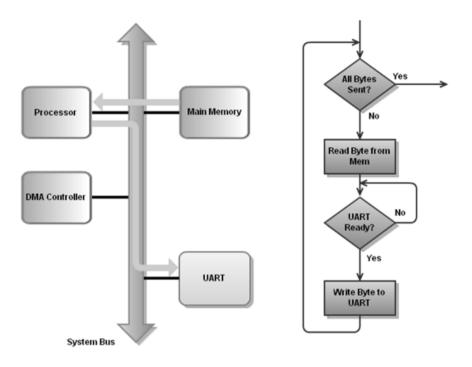

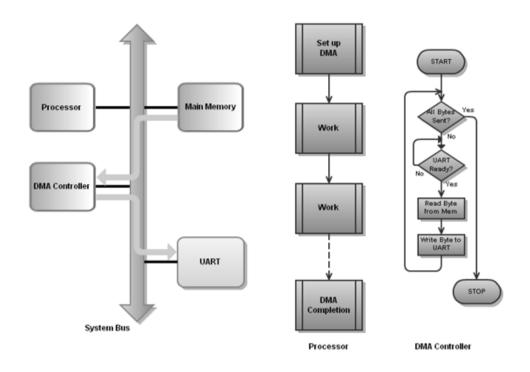

| Figure 3-23 Programmed I/O to UART                            | .53 |

| Figure 3-24 DMA Transfer to UART                              | .54 |

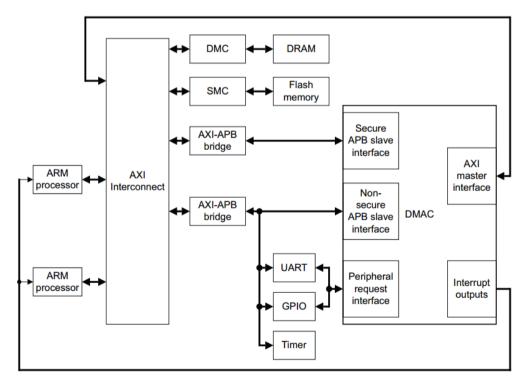

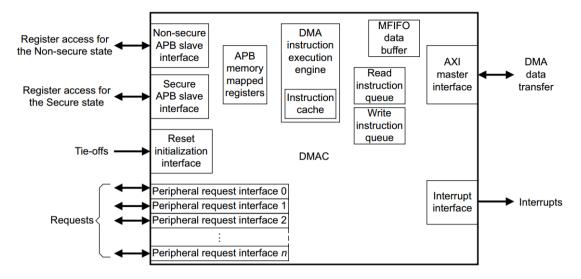

| Figure 3-25 DMA Interface                                     | .56 |

| Figure 3-26 DMA Block Diagram                                 | .57 |

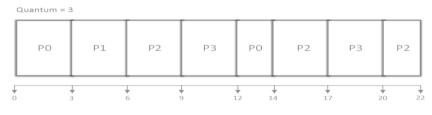

| Figure 3-27 Round Robin Scheduling                            | .59 |

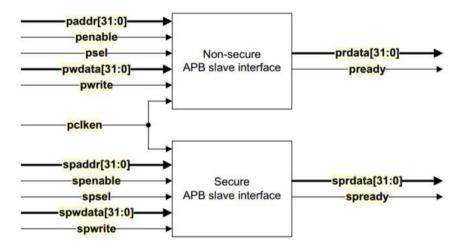

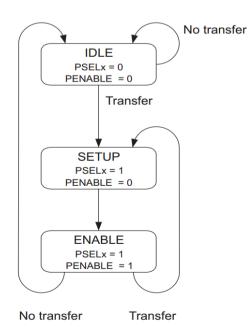

| Figure 3-28 DMA APB Interface                                 | .59 |

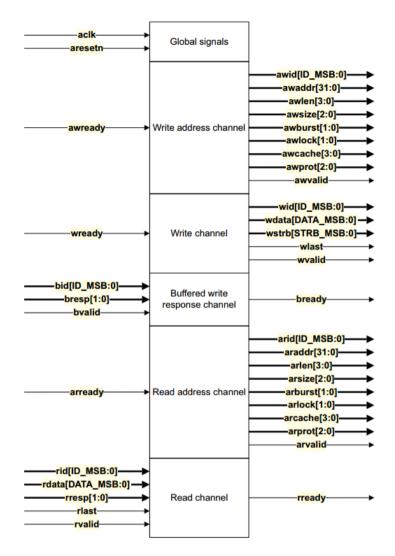

| Figure 3-29 DMA AXI Interface                                 | .60 |

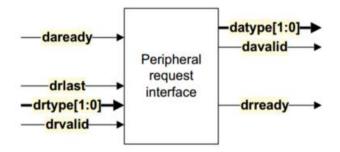

| Figure 3-30 Peripheral request interfaces                    | 61 |

|--------------------------------------------------------------|----|

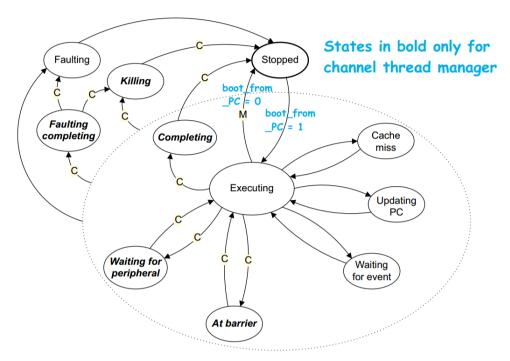

| Figure 3-31 Operating state in DMAC                          | 62 |

| Figure 3-32 DMA Write Transfer                               | 63 |

| Figure 3-33 DMA Read Transfer                                | 64 |

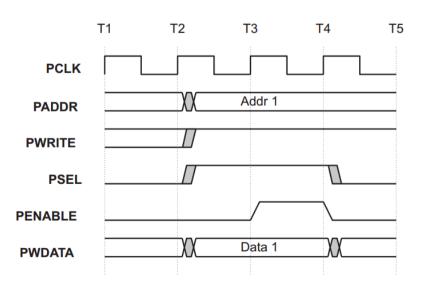

| Figure 3-34 Single and Burst request timing diagram          | 65 |

| Figure 3-35 Burst request timing diagram                     | 66 |

| Figure 3-36 DMA Abort handling                               | 68 |

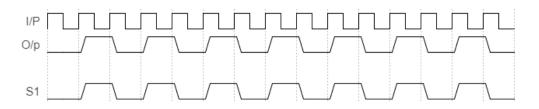

| Figure 3-37 Even Divider Timing Diagram                      | 69 |

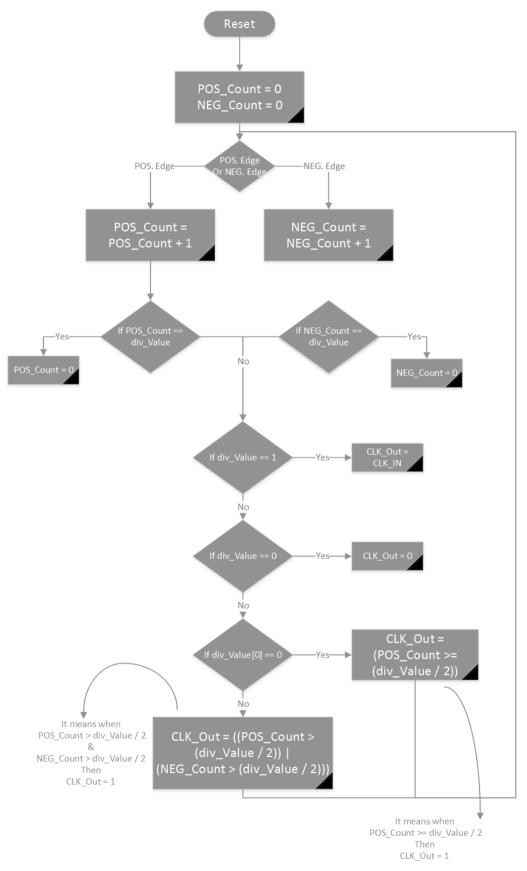

| Figure 3-38 Even Diagram Flow Chart                          | 69 |

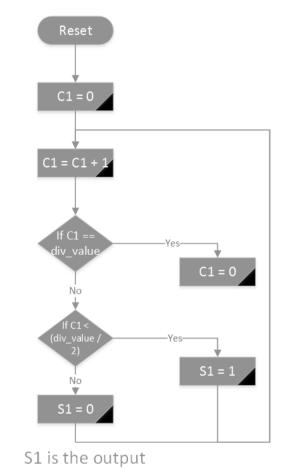

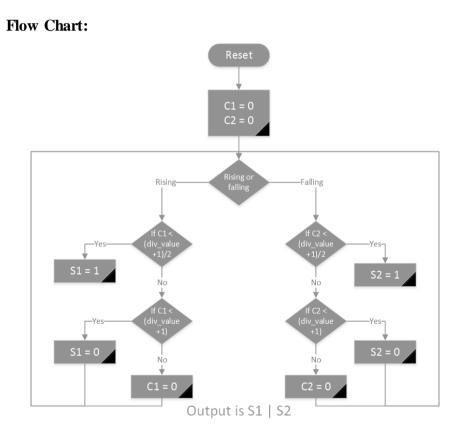

| Figure 3-39 Odd Divider Timing Diagram                       | 70 |

| Figure 3-40 Optimized Design Flow Chart                      | 71 |

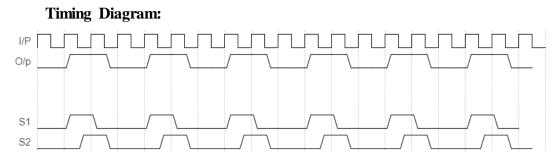

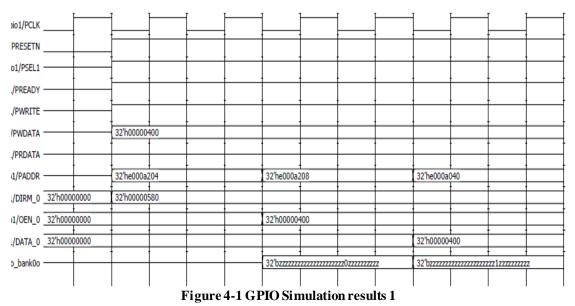

| Figure 4-1 GPIO Simulation results 1                         | 72 |

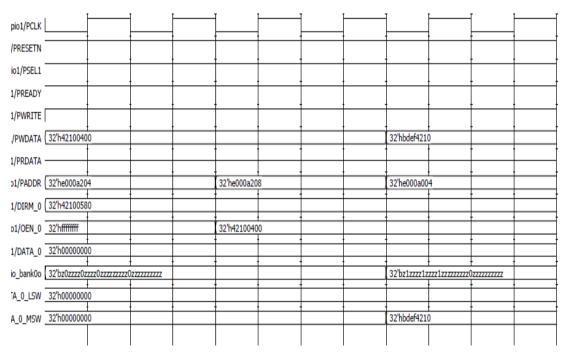

| Figure 4-2 GPIO Simulation results 2                         | 73 |

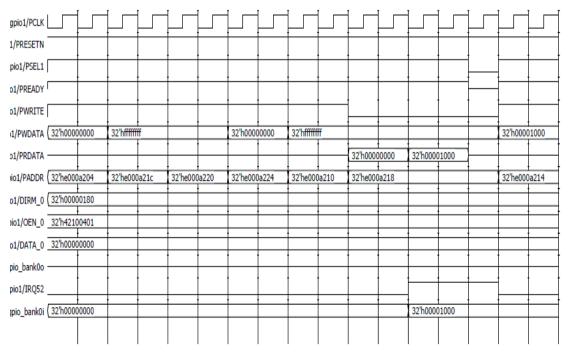

| Figure 4-3 GPIO Simulation results 3                         | 74 |

| Figure 4-4 GPIO Simulation results 4                         | 74 |

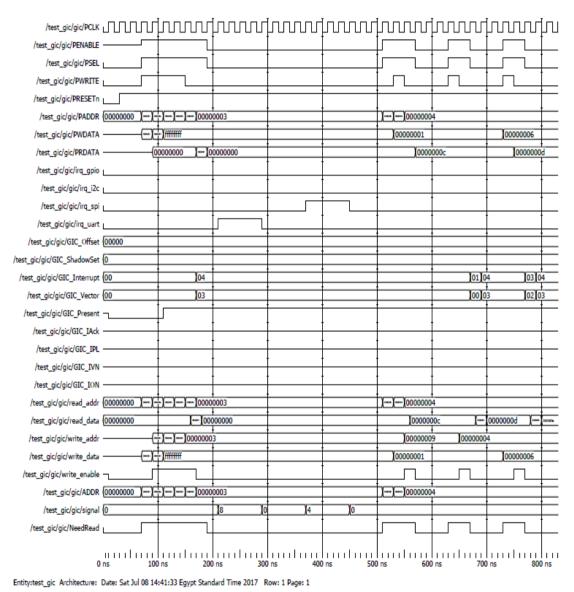

| Figure 4-5 GIC Simulation Results                            | 75 |

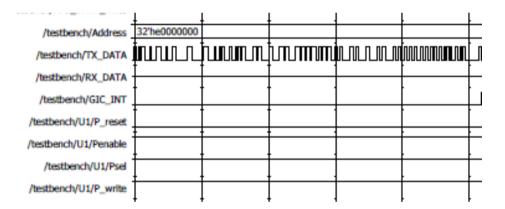

| Figure 4-6 FIFO containing the 16 bytes to be sent           | 76 |

| Figure 4-7 interrupt is raised and 0the data is totally sent | 76 |

| Figure 4-8 SPI Simulation Results                            | 77 |

| Figure 4-9 SPI Memory results                                | 78 |

| Figure 4-10 I2C Simulation results                           | 78 |

| Figure 4-11 Synthesis diagram                                | 79 |

| Figure 4-12 Logic Synthesis steps                            | 79 |

| Figure 4-13 Static Timing Analysis                           | 80 |

| Figure 4-14 Negative slack                                   | 81 |

| Figure 4-15 Synthesis Problem 1                              | 81 |

| Figure 4-16 Integration                                      | 82 |

| Figure 4-17 Zynq Blocks Integration                          | 83 |

| Figure 4-18 GPIO Scenarios                                   | 84 |

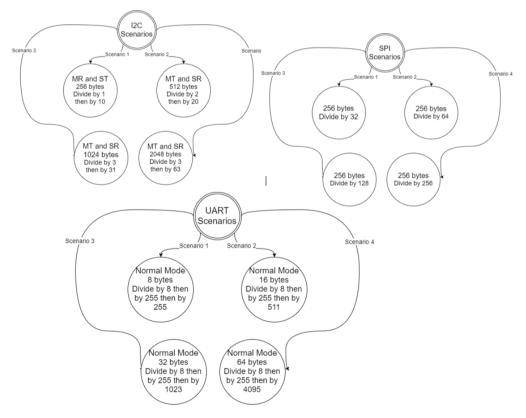

| Figure 4-19 I2C, SPI, UART Scenarios                         | 84 |

| Figure 4-20 Integration Problem 1                            | 85 |

| Figure 4-21 Interrupts implementation Problem                | 86 |

| Figure 5-1 Power Characterization flow                       | 87 |

| Figure 5-2 Power Characterization in TLPM                    |    |

# List of Symbols and Abbreviations

| RTL  | Register Transfer Level                     |

|------|---------------------------------------------|

| TLM  | Transaction Level Modeling                  |

| DMA  | Direct Memory Access                        |

| GPIO | General Purpose Input/ Output               |

| GIC  | Generic Interrupt Controller                |

| I2C  | Inter-Integrated Circuit                    |

| SPI  | Serial Peripheral Interface                 |

| UART | Universal Asynchronous Receiver Transmitter |

| FIFO | First In First Out                          |

| Rx   | Receiver                                    |

| Тх   | Transmitter                                 |

| PPI  | Private Peripheral Interrupt                |

| SPI  | Shared Peripheral Interrupt                 |

| SGI  | Software Generated Interrupt                |

| APB  | Advanced Peripheral Bus                     |

## Acknowledgments

We have the opportunity to present our appreciation to all of those who helped and supported us along the year work.

First, to our advisors, Dr. Hassan Mostafa and Dr. Magdy El-Morsy, we would like to express our sincere gratefulness and appreciation for their excellent guidance, caring, patience, and immense help in planning and executing the work in a timely manner. Their great personality and creativity provided us with an excellent atmosphere for work, while their technical insight and experience helped us a lot in our research. Their support at the time of crisis will always be remembered.

Of course, we will never find words enough to express the gratitude and appreciation that we owe to our families. Their tender love and support have always been the cementing force for building what we achieved. The all-round support rendered by them provided the much needed stimulant to sail through the phases of stress and strain.

We would like also to thank Eng. Amr Baher, who was always there for any research questions, providing precious advice and sharing his time and experience.

We would like to thank Eng. Zyad Abd El Tawab and Eng. Amr Hany for their assistance and contribution in the tools support.

Finally, Thanks are due to previous GP members. Their theses were supportive, informative and guided us in many critical issues.

## Abstract

Designing a system on chip (SoC) is one of the main challenges nowadays in the market. A wide introducing of the TLM in implementing SoCs is proposed to prove its uniqueness in getting faster validation for the designers. This paper introduces a methodology that using TLM to accelerate the simulation time than RTL with accurate power estimation. Some techniques (RTL simulation, Design synthesis and SystemC prototyping) are used to achieve the methodology purpose. ZYNQ-7000 FPGA blocks (GPIO, SPI, I2C and UART) are implemented on RTL and TLM to validate the methodology.

The validation of the functionality is obtained through similar scenarios on both TLM and RTL. Experimental results reveal the efficiency and accuracy of the methodology. This methodology has appeared to speed up the simulation time up to 636 times than RTL while the error in power estimation is on average 1.2%.

In our study, we show that by raising the level of abstraction, one not only achieves better simulation speed, flexibility, ease of verification but also reduces time to develop and shorten code length. All this is achieved while being able to maintain almost the same accuracy.

Evaluating power consumption at early phase of product life cycle is important to decrease the number of the expensive design iterations. A methodology is proposed in our study for dynamic power estimation using Transaction Level Modelling (TLM). The methodology exploits the existing tools for RTL simulation, design synthesis and SystemC prototyping to provide fast and accurate power estimation using Transaction Level Power Modelling (TLPM).

## **Chapter 2:** Introduction

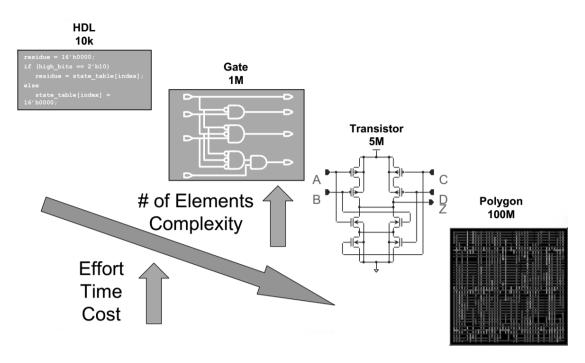

SoCs are widely used nowadays in many applications like mobiles, cameras, FPGAs,...etc. Trying to implement SoC on RTL reveals some restrictions. The main restriction is the simulation time. As the SoC complexity increases, the simulation time increases or simulation crashes. As a result, another restriction appeared which is power estimation.

Trying to get an estimation of the dynamic power on RTL has become an impossible target due to the large simulation time. To overcome the drawbacks of RTL, different methodologies and modeling techniques have been implemented to keep the design life cycle short. The trials show that implementing SoCs using TLM has a great impact on accelerating design life cycle and introducing it to the market in a short time.

Whenever the estimation of the power was in early stages, the release of the design will be accelerated. This will save the expensive costs paid on the huge computations of the long iterations which elongate the design life cycle. SoC design brings with it new challenges and difficulties.

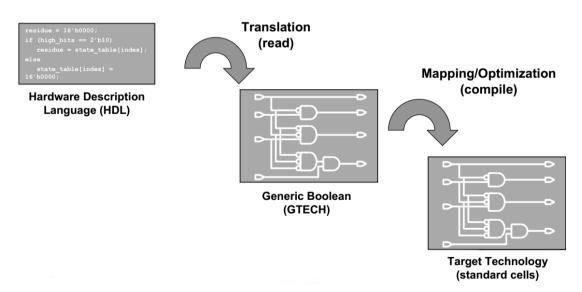

The designs are large, complicated, and involve software and hardware components. These designs have to be modeled at a high level of abstraction before partitioning into hardware and software components for final implementation. From the hardware (HW) design point of view, hardware description languages (HDLs) such as Verilog and VHDL, in conjunction with hardware simulation and synthesis tools, have proven highly valuable. Efforts have been made to extend these approaches to work for multiprocessor-based SoC design, but these tend to require a significant amount of information about the partitioning of the system into coarse-grained blocks at the start. With the increased complexity new approaches seem inevitable.

We are at a transition stage similar to the move from schematic-based design to hardware description language (HDL)-based design. A few years ago, just the notion of a new language (such as C) for hardware design, raised technical and suitability issues. Hardware engineers accustomed to using HDLs find it difficult to accept that a software development and modeling language such as C/C++ could be useful for hardware design. To accelerate hardware design, designers use software models of the hardware that they build. These models developed at high level of abstraction are used to validate the functionality and evaluate performance.

SystemC a relatively new language, is aimed at facilitating model development above the register transfer level (RTL) [1,2]. SystemC 2.0 provides the ability to capture designs at various levels of abstraction. The single language solution to express designs at different levels of abstraction makes SystemC language a strong contender for system level design language. Built around the C++ language, SystemC inherits the reputation of C++ as a multiparadigm language, and offers additional capabilities for HW design. SystemC is close enough to C++ to develop SW intellectual property (IP) blocks, and is well suited for developing HW soft IP's.

Earlier to SystemC, a typical design at system level was created using C/C++, Matlab, Spreadsheet or some variant. Next, these designs had to be manually translated into RTL to capture the architecture. This conversion would typically lead to many design errors making previous work unfit for reuse.

SystemC provides various features to perform system level modeling and simulation, which are missing in the generic HDL's such as VHDL and Verilog. But SystemC is not intended to replace Verilog or VHDL. Supporting models at various levels of abstraction is a key feature in SystemC. Synthesizability of the SystemC models currently lacks commercial tool support.

### 2.1 Problem Overview

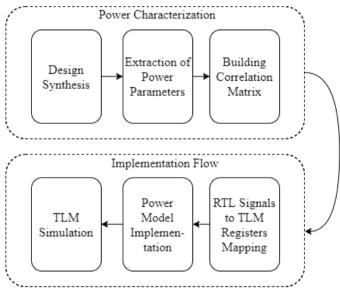

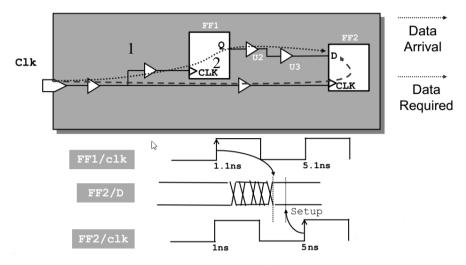

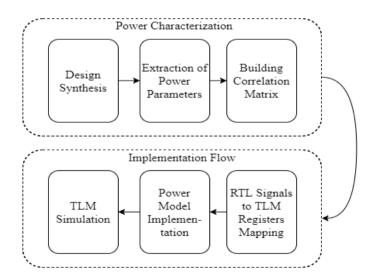

Determining the power of large System-on-Chip (SoC) designs is very computational and time expensive on Register Transfer Level (RTL), if even possible. Power should be addressed in early stages of the design process to prevent long expensive iterations, which hinders releasing a design. Integration of power computation with TLM is gaining interest in both research and industry. TLM for power is needed to overcome any unexpected drawback in the design at early stages. In this paper, estimating power dissipation on TLM is performed in two stages: Characterization and Implementation. Characterization represents the extraction of power model to TLM and the execution of this model to have reliable numbers of power consumption. The flow is introduced in Figure 2-1.

## 2.2 Solution

Several approaches have been developed to estimate the power using different methodologies at various abstraction levels of the design. The presented approach misses important design elements such as power management components, which affects accuracy for the resulting power numbers versus actual on-chip ones. The flow in Power Kernel tool adopts cycle-accurate models in TLM. This leads to large simulation time.

Figure 2-1. Flow of the extraction of power parameters

Transaction Level Power Modeling (TLPM) Flow Characterizing power parameters has been addressed in previous works using extracted Gate level parasitics as introduced in [3,5]. The parasitics are used to build database in order to calculate the power equation. This process of parasitics extraction and Gate level simulation is complicated and time consuming. Simulation overhead is very high in [8,9]. Extending every SystemC module with add-on library leads to undesirable additional simulation time for power instrumentation.

Previous approaches are not suitable for large designs of SoC. They are either too slow or too inaccurate. In this thesis, approximately-timed modeling at high level of abstraction of the design components is adopted to achieve fast simulation with high precision. A methodology for estimating power dissipation on TLM (TLPM) is developed. The simulation overhead of power instrumentation is minimized.

## 2.3 Work Flow

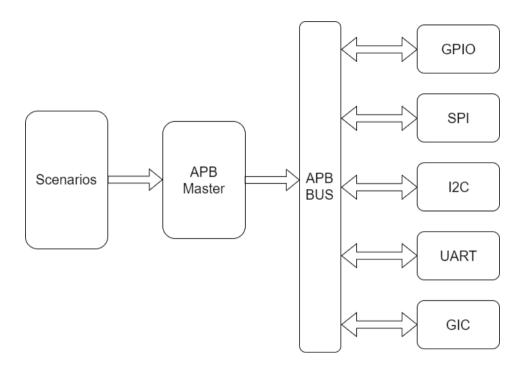

In this document, we discuss the effect of modeling at different levels of abstractions using SystemC and Verilog. We start with an introduction to Zynq-7000 SoC and the implemented blocks (GPIO, GIC, SPI, I2C, and UART) in Chapter 3. Then, we discuss the Simulation of each block along with Synthesis and Integration in Chapter 4.

In Chapter 5, we introduce the Transaction Level Power Modeling methodology and power characterization flow. Finally, in Chapter 6, we discuss the results obtained and provide conclusions.

## Chapter 3: Zynq-7000 All Programmable SoC

## 3.1 Introduction

The System-on-Chip (SoC) we are basing our comparative analysis on is the Zynq-7000 family platform. The Zynq<sup>®</sup>-7000 family is based on the Xilinx<sup>®</sup> All Programmable SoC (AP SoC) architecture. These products integrate a feature-rich dual-core ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 MPCore<sup>TM</sup> based processing system (PS) and Xilinx programmable logic (PL) in a single device, built on a state-of-the-art, highperformance, low-power (HPL), 28 nm, and high-k metal gate (HKMG) process technology. The ARM Cortex-A9 MPCore CPUs are the heart of the PS which also includes on-chip memory, external memory interfaces, and a rich set of I/O peripherals.

The Zynq-7000 family offers the flexibility and scalability of an FPGA, while providing performance, power, and ease of use typically associated with ASIC and ASSPs. The range of devices in the Zynq-7000 AP SoC family enables designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each device in the Zynq-7000 family contains the same PS, the PL and I/O resources vary between the devices. As a result, the Zynq-7000 AP SoC devices can serve a wide range of applications including:

- Automotive driver assistance, driver information, and infotainment

- Broadcast camera

- Industrial motor control, industrial networking, and machine vision

- IP and smart camera

- LTE radio and baseband

- Medical diagnostics and imaging

- Multifunction printers

- Video and night vision equipment

The Zynq-7000 architecture conveniently maps the custom logic and software in the PL and PS respectively. It enables the realization of unique and differentiated system

functions. The integration of the PS with the PL provides levels of performance that two-chip solutions (for example, an ASSP with an FPGA) cannot match due to their limited I/O bandwidth, loose-coupling and power budgets.

## 3.2 Block Diagram

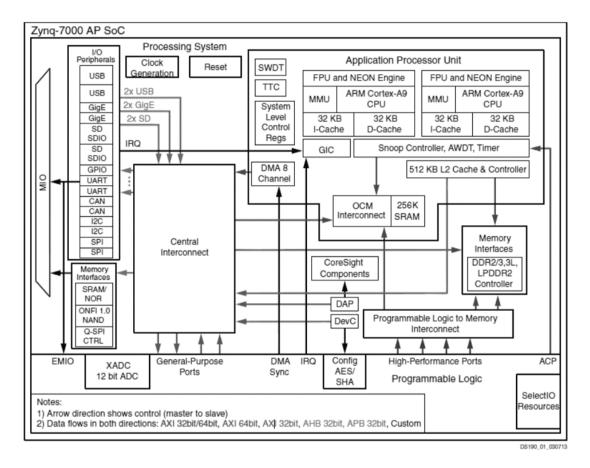

Figure 3-1 illustrates the functional blocks of the Zynq-7000 AP SoC.

Figure 3-1. Block Diagram of Zynq-7000

It is obvious that the System is too huge and could never be completely built within neither the available time nor the allowed team number. Hence, only six blocks were chosen to build our analysis on. These blocks are GPIO, SPI, UART, GIC, I2C, and DMAC. In the next sections in this chapter, we will talk about each one of these blocks in details.

## **3.3 GPIO**

The general purpose I/O (GPIO) peripheral provides software with observation and control of up to 54 device pins via the MIO module. It also provides access to 64 inputs from the Programmable Logic (PL) and 128 outputs to the PL through the EMIO interface. The GPIO is organized into four banks of registers that group related interface signals. Each GPIO is independently and dynamically programmed as input, output, or interrupt sensing.

Software can read all GPIO values within a bank using a single load instruction, or write data to one or more GPIOs (within a range of GPIOs) using a single store instruction. The GPIO control and status registers are memory mapped at base address 0xE000\_A000.

## 3.3.1 Features

Key features of the GPIO peripheral are summarized as follows:

- 54 GPIO signals for device pins (routed through the MIO multiplexer).

- Outputs are 3-state capable.

- 192 GPIO signals between the PS and PL via the EMIO interface.

- 64 Inputs, 128 outputs (64 true outputs and 64 output enables).

- The function of each GPIO can be dynamically programmed on an individual or group basis.

- Enable, bit or bank data write, output enable and direction controls.

- Programmable interrupts on individual GPIO basis.

- Status read of raw and masked interrupt.

- Selectable sensitivity: Level-sensitive (High or Low) or edge-sensitive (positive, negative, or both).

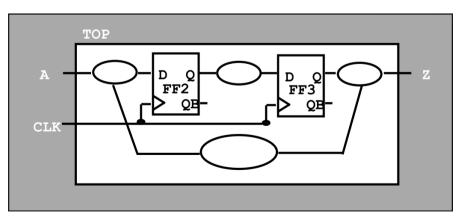

#### 3.3.2 Block Diagram

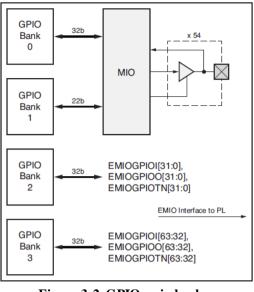

As shown in Figure 3-2, the GPIO module is divided into four banks:

- 1. Bank0: 32-bit bank controlling MIO pins [31:0].

- 2. Bank1: 22-bit bank controlling MIO pins [53:32].

- 3. Bank2: 32-bit bank controlling EMIO signals [31:0].

- 4. Bank3: 32-bit bank controlling EMIO signals [63:32].

*Note:* Bank1 is limited to 22 bits because the MIO has a total of 54 pins.

Figure 3-2. GPIO main banks

Each bank consists of several registers and other functional hardware as shown in Figure 3-3.

Figure 3-3. GPIO Functional Block Diagram

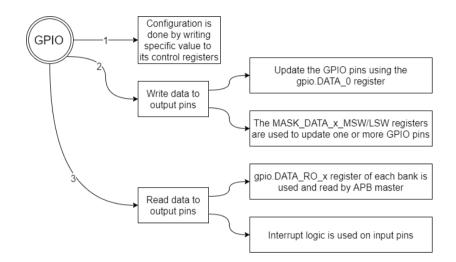

### **3.3.3 Functional Description**

The GPIO is controlled by software through a series of memory-mapped registers. The control for each bank is the same, although there are minor differences between the MIO and EMIO banks due to their differing functionality.

Software configures the GPIO as either an output or input. The DATA\_RO register always returns the state of the GPIO pin regardless of whether the GPIO is set to input (OE signal false) or output (OE signal true). To generate an output waveform, software repeatedly writes to one or more GPIOs (usually using the MASK\_DATA register).

Applications might need to switch more than one GPIO at the same time (less a small amount of inherent skew time between two I/O buffers). In this case, all the GPIOs that need to be switched simultaneously must be from the same 16-bit half-bank (i.e., either the most-significant 16 bits or the least-significant 16 bits) of GPIOs to enable the MASK\_DATA register to write to them in one store instruction.

GPIO bank control (for Bank0 and Bank1) is summarized as follows:

- DATA\_RO: This register enables software to observe the value on the device pin. If the GPIO signal is configured as an output, then this would normally reflect the value being driven on the output. Writes to this register are ignored. If the MIO is not configured to enable this pin as a GPIO pin, then DATA\_RO is unpredictable because software cannot observe values on non-GPIO pins through the GPIO registers.

- DATA: This register controls the value to be output when the GPIO signal is configured as an output. All 32 bits of this register are written at one time. Reading from this register returns the previous value written to either DATA or MASK\_DATA {LSW, MSW}; it does not return the current value on the device pin.

- MASK\_DATA\_LSW: This register enables more selective changes to the desired output value. Any combination of up to 16 bits can be written. Those bits that are not written are unchanged and hold their previous value. Reading from this register returns the previous value written to either DATA or MASK\_DATA {LSW, MSW}; it does not return the current value on the device pin. This register avoids the need for a read-modify-write sequence for unchanged bits.

- MASK\_DATA\_MSW: This register is the same as MASK\_DATA\_LSW, except it controls the upper16 bits of the bank.

- DIRM: Direction Mode. This controls whether the I/O pin is acting as an input or an output. Since the input logic is always enabled, this effectively enables/disables the output driver. When DIRM[x]==0, the output driver is disabled.

- OEN: Output Enable. When the I/O is configured as an output, this controls whether the output is enabled or not. When the output is disabled, the pin is 3-stated. When OEN[x]==0, the output driver is disabled. If MIO TRI\_ENABLE is set to 1, enabling 3-state and disabling the driver, then OEN is ignored and the output is 3-stated.

## 3.3.4 EMIO Signals

This section describes the operation of Bank2 and Bank3. The register interface for the EMIO banks is the same as for the MIO banks described in the previous section. However, the EMIO interface is simply wires between the PS and the PL, so there are a few differences:

- The inputs are wires from the PL and are unrelated to the output values or the OEN register. They can be read from the DATA\_RO register when DIRM is set to 0, making it an input.

- The output wires are not 3-state capable, so they are unaffected by OEN. The value to be output is programmed using the DATA, MASK\_DATA\_LSW, and MASK\_DATA\_MSW registers. DIRM *must* be set to 1, making it an output.

- The output enable wires are simply outputs from the PS. These are controlled by the DIRM/OEN registers as follows: EMIOGPIOTN[x] = DIRM[x] & OEN[x].

- The EMIO I/Os are not connected to the MIO I/Os in any way. The EMIO inputs cannot be connected to the MIO outputs and the MIO inputs cannot be connected to the EMIO outputs. Each bank is independent and can only be used as software observable/controllable signals.

GPIO bits [8:7] of Bank0 correspond to package pins that are used to control the voltage mode of the I/O buffers themselves during reset. These pins are called the VMODE pin straps for the MIO. They must be driven by the external system

according to the proper voltage mode. To prevent them from being driven by other system logic, they cannot be used as general-purpose inputs.

These bits can be used as general-purpose outputs since the output driver is disabled at reset. The system can start using these as outputs after the voltage mode has been read during system boot.

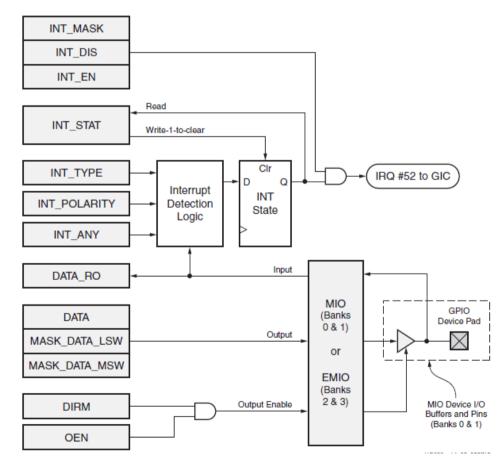

## 3.3.5 Interrupts

The interrupt detection logic monitors the GPIO input signal. The interrupt trigger can be a positive edge, negative edge, either edge, Low-level or High-level. The trigger sensitivity is programmed using the INT\_TYPE, INT\_POLARITY and INT\_ANY registers as shown in Table 1.

If an interrupt is detected, the GPIO's INT\_STAT state is set true by the interrupt detection logic. If the INT\_STAT state is enabled (unmasked), then the interrupt propagates through to a large OR function. This function combines all interrupts for all GPIOs in all four banks to one output (IRQ ID#52) to the interrupt controller. If the interrupt is disabled (masked), then the INT\_STAT state is maintained until cleared, but it does not propagate to the interrupt controller unless the INT\_EN is later written to disable the mask. As all GPIOs share the same interrupt, software must consider both INT\_MASK and INT\_STAT to determine which GPIO is causing an interrupt.

The interrupt mask state is controlled by writing a 1 to the INT\_EN and INT\_DIS registers. Writing a 1 to the INT\_EN register disables the mask allowing an active interrupt to propagate to the interrupt controller. Writing a 1 to the INT\_DIS register enables the mask. The state of the interrupt mask can be read using the INT\_MASK register.

If the GPIO interrupt is edge sensitive, then the INT state is latched by the detection logic. The INT latch is cleared by writing a 1 to the INT\_STAT register. For level-sensitive interrupts, the source of the interrupt input to the GPIO must be cleared to clear the interrupt signal. Alternatively, software can mask that input using the INT\_DIS register.

The state of the interrupt signal going to the interrupt controller can be inferred by reading the INT\_STAT and INT\_MASK registers. This interrupt signal is asserted if INT\_STAT=1 and INT\_MASK=0. GPIO bank control is summarized as follows:

11

- **INT\_MASK:** This register is read-only and shows which bits are currently masked and which are un-masked/enabled.

- **INT\_EN:** Writing a 1 to any bit of this register enables/unmasks that signal for interrupts. Reading from this register returns an unpredictable value.

- **INT\_DIS:** Writing a 1 to any bit of this register masks that signal for interrupts. Reading from this register returns an unpredictable value.

- **INT\_STAT:** This register shows if an interrupt event has occurred or not. Writing a 1 to a bit in this register clears the interrupt status for that bit. Writing a 0 to a bit in this register is ignored.

- **INT\_TYPE:** This register controls whether the interrupt is edge sensitive or level sensitive.

- **INT\_POLARITY:** This register controls whether the interrupt is active-Low or active High (or falling-edge sensitive or rising-edge sensitive).

- **INT\_ON\_ANY:** If INT\_TYPE is set to edge sensitive, then this register enables an interrupt event on both rising and falling edges. This register is ignored if INT\_TYPE is set to level sensitive.

| Туре                                   | gpio.INT_TYPE_0 | gpio.INT_POLARITY_0 | gpio.INT_ANY_0 |

|----------------------------------------|-----------------|---------------------|----------------|

| Rising edge-sensitive                  | 1               | 1                   | 0              |

| Falling edge-sensitive                 | 1               | 0                   | 0              |

| Both rising and falling edge-sensitive | 1               | Х                   | 1              |

| Level sensitive, asserted High         | 0               | 1                   | Х              |

| Level sensitive, asserted Low          | 0               | 0                   | Х              |

#### Table 1 GPIO Interrupt signals

## **3.4 GIC**

The generic interrupt controller (GIC) is a centralized resource for managing interrupts sent to the CPUs from the Processing System (PS) and the Programmable Logic (PL). The controller enables, disables, masks, and prioritizes the interrupt sources and sends them to the selected CPU (or CPUs) in a programmed manner as the CPU interface accepts the next interrupt.

The controller is based on the ARM Generic Interrupt Controller Architecture version 1.0 (GIC v1), non-vectored. The registers are accessed via the CPU private bus for fast read/write response by avoiding temporary blockage or other bottlenecks in the interconnect.

The interrupt distributor centralizes all interrupt sources before dispatching the one with the highest priority to the individual CPUs. The GIC ensures that an interrupt targeted to several CPUs can only be taken by one CPU at a time. All interrupt sources are identified by a unique interrupt ID number. All interrupt sources have their own configurable priority and list of targeted CPUs.

#### 3.4.1 Block Diagram

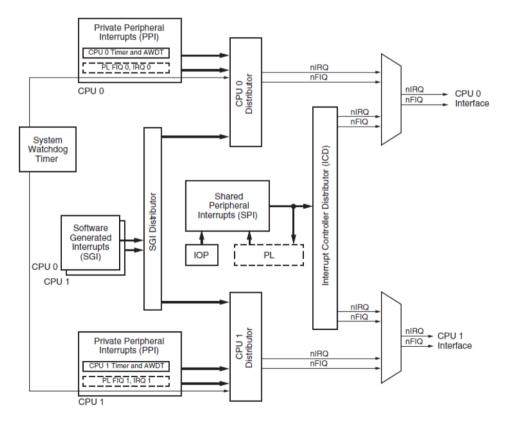

There are three main sources of interrupts controlled by the GIC; Software Generated Interrupts (SGI), CPU Private Peripheral Interrupts (PPI), and Shared Peripheral Interrupts (SPI). The shared peripheral interrupts are generated from various subsystems that include the I/O peripherals in the PS and logic in the PL. The interrupt sources are illustrated in Figure 3-4.

Figure 3-4 GIC Block Diagram

## 3.4.2 Functional Description

## Software Generated Interrupts (SGI)

Each CPU can interrupt itself, the other CPU, or both CPUs using a software generated interrupt (SGI). There are 16 software generated interrupts whose IDs are from 0 to 15. An SGI is generated by writing the SGI interrupt number to the ICDSGIR register and specifying the target CPU(s). This write occurs via the CPU's own private bus.

Each CPU has its own set of SGI registers to generate one or more of the 16 software generated interrupts. All SGIs are edge triggered. The sensitivity types for SGIs are fixed and cannot be changed; the ICDICFR0 register is read-only, since it specifies the sensitivity types of all the 16 SGIs.

## **CPU Private Peripheral Interrupts (PPI)**

Each CPU connects to a private set of five peripheral interrupts whose IDs are from 7 to 31 since IDs from 16 to 26 are reserved as shown in Table 2. The sensitivity types for PPIs are fixed and cannot be changed.

| PPI # | IRQ ID # | Source            |

|-------|----------|-------------------|

| ~     | 16:26    | Reserved          |

| 0     | 27       | Global Timer      |

| 1     | 28       | nFIQ              |

| 2     | 29       | CPU Private Timer |

| 3     | 30       | AWDT (Watchdog)   |

| 4     | 31       | nIRQ              |

#### Table 2 PPI Interrupt Requests IDs

#### Shared Peripheral Interrupts (SPI)

A group of approximately 60 interrupts from various modules can be routed to one or both CPUs or the PL. The interrupt controller manages the prioritization and reception of these interrupts for the CPUs. Except for IRQ #61 through #68 and #84 through #91 (PL), all interrupt sensitivity types are fixed by the requesting sources and cannot be changed.

The SPI interrupts are listed in Table 3.

| SPI # | IRQ ID # | Source   |

|-------|----------|----------|

| 0:3   | 32:35    | APU      |

| ~     | 36       | Reserved |

| 4:5   | 37:38    | PMU      |

| 6     | 39       | XADC     |

| 7     | 40       | DevC     |

| 8     | 41       | SWDT     |

| 9:11  | 42:44    | TTC0     |

| 12:16 | 45:49    | DMAC     |

| 17:18 | 50:51    | Memory   |

| 19:27 | 52:60    | IOP (0)  |

| 28:35 | 61:68    | PL (0)   |

| 36:38 | 69:71    | TTC1     |

| 39:42 | 72:75    | DMAC     |

| 43:50 | 76:83    | IOP (1)  |

| 51:58 | 84:91    | PL (1)   |

| 59    | 92       | SCU      |

| ~     | 93:95    | Reserved |

#### Table 3 SPI Interrupt Requests IDs

#### 3.4.3 Interrupt Sensitivity and Targeting

There are three types of interrupts that come into the GIC as explained before: SPI, PPI and SGI. In a general sense, the interrupt signals include a sensitivity setting, whether one or both CPUs handle the interrupt, and which CPU or CPUs are targeted: zero, one, or both. However, the functionality of most interrupt signals includes fixed settings, while others are partially programmable.

#### Shared Peripheral Interrupts (SPI)

The SPI interrupts can be targeted to any number of CPUs, but only one CPU handles the interrupt. If an interrupt is targeted to both CPUs and they respond to the GIC at the same time, the MPcore ensures that only one of the CPUs reads the active interrupt ID#. The other CPU receives the Spurious ID# 1023 interrupt or the next pending interrupt, depending on the timing. This removes the requirement for a lock in the interrupt service routine. Targeting the CPU is done by the ICDIPTR [23:8] registers.

## Private Peripheral Interrupts (PPI)

Each CPU has its own separate PPI interrupts with fixed functionality; the sensitivity, handling, and targeting of these interrupts are not programmable. Each interrupt only goes to its own CPU and is handled by that CPU.

### Software Generated Interrupts (SGI)

The SGI interrupts are always edge sensitive and are generated when software writes the interrupt number to ICDSGIR register. All the targeted CPUs defined in the ICDIPTR [23:8] must handle the interrupt to clear it.

## 3.4.4 Interrupt Prioritization and Handling

All of the interrupt requests (PPI, SGI and SPI) are assigned a unique ID number. The controller uses the ID number to arbitrate. The interrupt distributor holds the list of pending interrupts for each CPU, and then selects the highest priority interrupt before issuing it to the CPU interface. Interrupts of equal priority are resolved by selecting the lowest ID.

The prioritization logic is physically duplicated to enable the simultaneous selection of the highest priority interrupt for each CPU. The interrupt distributor holds the central list of interrupts, processors and activation information, and is responsible for triggering software interrupts to the CPUs.

SGI and PPI distributor registers are banked to provide a separate copy for each connected processor. Hardware ensures that an interrupt targeting several CPUs can only be taken by one CPU at a time. The interrupt distributor transmits to the CPU interfaces the highest pending interrupt. It receives back the information that the interrupt has been acknowledged, and can then change the status of the corresponding interrupt. Only the CPU that acknowledges the interrupt can end that interrupt.

If the interrupt is pending in the GIC and IRQ is de-asserted, the interrupt in the GIC becomes inactive (and the CPU never sees it). If the interrupt is active in the GIC (because the CPU interface has acknowledged the interrupt), then the software ISR determines the cause by checking the GIC registers first and then polling the I/O Peripheral interrupt status registers.

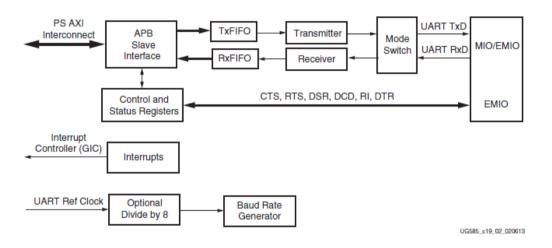

## **3.5 UART**

UART stands for universal asynchronous receiver and transmitter. It is one of the peripheral blocks found in any SoC. It supports full-duplex transmission and reception of data bits through different modes. The main usage of the UART is going from parallel to serial communication and vice versa. Also, as it is asynchronous, the receiver has to wait for the start bit and start reception. The UART implemented according to the specifications extracted from the Zynq-7000 FPGA.

UART supports a wide range of programmable baud rates and I/O signal formats. The controller can accommodate automatic parity generation and multi-master detection mode. The UART operations are controlled by the configuration and mode registers. The state of the FIFOs, modem signals and other controller functions are read using the status, interrupt status and modem status registers.

The controller is structured with separate Rx and Tx data paths. Each path includes a 64-byte FIFO. The controller serializes and de-serializes data in the Tx and Rx FIFOs and includes a mode switch to support various loopback configurations for the RxD and TxD signals. The FIFO interrupt status bits support a polling or interrupt driven handler. Software reads and writes data bytes using the Rx and Tx data port registers.

When the UART is being used in a modem-like application, the modem control module detects and generates the modem handshake signals and controls the receiver and transmitter paths according to the handshaking protocol. There are 2 UARTs inside the Zynq-7000. Both can work independently and there is an option to make them transmit and receive to each other.

#### 3.5.1 Features

The UART supports a lot of features. It includes features of the frame form. The number of bits can be adopted and the parity bit of the frame. Also, the Number of bytes and the modes supported in the UART is added. Besides, the interrupts are generated to the GIC. The option of setting the two UARTs together to transmit and receive between each other is supported but is performed by the main processor of the system.

Each UART controller (UART 0 and UART 1) has the following features:

- Programmable baud rate generator

- 64-byte receive and transmit FIFOs

- Programmable protocol

- o 6, 7, or 8 data bits

- 1, 1.5, or 2 stop bits

- Odd, even, space, mark, or no parity

- Parity, framing and overrun error detection

- Line-break generation

- Interrupts generation

- RxD and TxD modes: Normal/echo and diagnostic loopbacks using the mode switch

- Loop UART 0 with UART 1 option

- Modem control signals: CTS, RTS, DSR, DTR, RI and DCD are available only on the EMIO interface

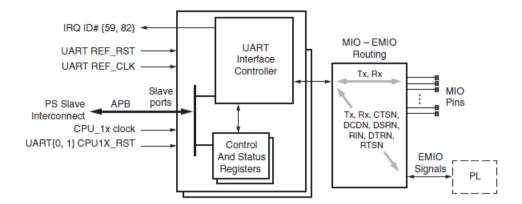

## 3.5.2 Block Diagram

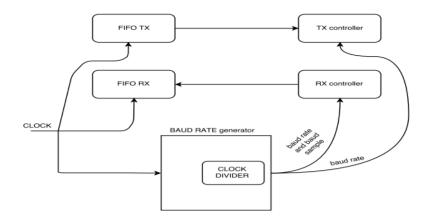

The overall system of the UART works according to Figure 3-5. The figure explains the block on system level. This overview shows how the main signals entering to the block and its interface with the I/O pins, the interface with the ABP bus and the interface with the GIC when interrupts are generated. The block has two different clocks coming from two different places (UART-REF-CLK and CPU-1X-CLK).

The pins of the Tx, Rx, GIC and modem signals are shown. Also, the interface of the controller with the registers appeared to control the features of the frame to be sent or received. The main brain of the UART is the controller that works and manages the other modules inside.

Figure 3-6 UART Block Diagram

The block diagram shows the internal structure of the UART block. And it is divided into several internal blocks. It is explained in the following section.

## 3.5.3 Functional Description

#### **Control Logic**

The control logic contains the Control register and the Mode register, which are used to select the various operating modes of the UART. The Control register enables, disables, and issues soft resets to the receiver and transmitter modules. In addition, it restarts the receiver timeout period, and controls the transmitter break logic. Receive line break detection must be implemented in Software. It will be indicated by a Frame Error followed by one or more zero bytes in the RxFIFO. The Mode register selects the clock used by the baud rate generator. It also selects the bit length, parity bit and stop bit to be used by transmitted and received data. In addition, it selects the mode of operation of the UART, switching between normal UART mode, automatic echo, local loopback, or remote loopback, as required.

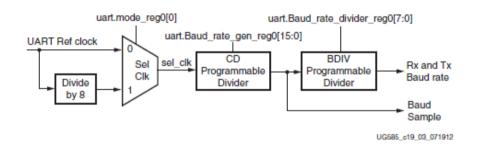

#### Baud Rate Generator

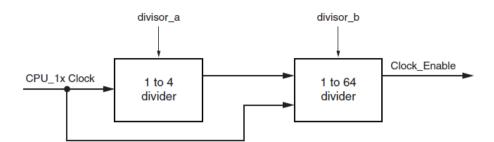

The baud rate generator furnishes the bit period clock, or baud rate clock, for both the receiver and the transmitter. The baud rate clock is implemented by distributing the base clock uart\_clk and a single cycle clock enable to achieve the effect of clocking at the appropriate frequency division. The effective logic for the baud rate generation is shown in Figure 3-7.

Figure 3-7 Baud Rate Generator

The baud rate generator can use either the master clock signal, Uart\_ref\_clk, or the master clock divided by eight, uart\_ref\_clk/8. The clock signal used is selected according to the value of the CLKS bit in the Mode register (uart.mode\_reg0). The resulting selected clock is termed sel\_clk in the following description.

The sel\_clk clock is divided down to generate three other clocks: baud\_sample, baud\_tx\_rate, and baud\_rx\_rate. The baud\_tx\_rate is the target baud rate used for transmitting data. The baud\_rx\_rate is nominally at the same rate, but gets resynchronized to the incoming received data. The baud\_sample runs at a multiple ([BDIV] + 1) of baud\_rx\_rate and baud\_tx\_rate and is used to over-sample the received data.

The sel\_clk clock frequency is divided by the CD field value in the Baud Rate Generator register to generate the baud\_sample clock enable. This register can be programmed with a value between 1 and 65535. The baud\_sample clock is divided by [BDIV] plus 1. BDIV is a programmable field in the Baud Rate

Divider register and can be programmed with a value between 4 and 255. It has a reset value of 15, inferring a default ratio of 16 baud\_sample clocks per baud\_tx\_clock /

baud\_rx\_rate. Thus, the frequency of the baud\_sample clock enable is shown in the following equation:

The frequency of the baud\_rx\_rate and baud\_tx\_rate clock enables is shown in the following equation:

## Transmit FIFO

The transmit FIFO (TxFIFO) stores data written from the APB interface until it is removed by the transmit module and loaded into its shift register. The TxFIFO maximum data width is eight bits. Data is loaded into the TxFIFO by writing to the TxFIFO register. When data is loaded into the TxFIFO, the TxFIFO empty flag is cleared and remains in this Low state until the last word in the TxFIFO has been removed and loaded into the transmitter shift register. This means that host software has another full serial word time until the next data is needed, allowing it to react to the empty flag being set and write another word in the TxFIFO without loss in transmission time.

The TxFIFO full interrupt status (TFULL) indicates that the TxFIFO is completely full and prevents any further data from being loaded into the TxFIFO. If another APB write to the TxFIFO is performed, an overflow is triggered and the write data is not loaded into the TxFIFO. The transmit FIFO nearly full flag (TNFULL) indicates that there is not enough free space in the FIFO for one more write of the programmed size, as controlled by the WSIZE bits of the Mode register.

The TxFIFO nearly-full flag (TNFULL) indicates that there is only byte free in the TxFIFO. A threshold trigger (TTRIG) can be setup on the TxFIFO fill level. The Transmitter Trigger register can be used to setup this value, such that the trigger is set when the TxFIFO fill level reaches this programmed value.

## Transmitter Data Stream

The transmit module removes parallel data from the TxFIFO and loads it into the transmitter shift register so that it can be serialized. The transmit module shifts out the start bit, data bits, parity bit, and stop bits as a serial data stream. Data is transmitted, least significant bit first, on the rising edge of the transmit baud clock enable (baud\_tx\_rate). The uart.mode\_reg0[CHRL] register bit selects the character length, in terms of the number of data bits. The uart.mode\_reg0[NBSTOP] register bit selects the number of stop bits to transmit.

#### **Receiver FIFO**

The RxFIFO stores data that is received by the receiver serial shift register. The RxFIFO maximum data width is eight bits. When data is loaded into the RxFIFO, the RxFIFO empty flag is cleared and this state remains Low until all data in the RxFIFO has been transferred through the APB interface. Reading from an empty RxFIFO returns zero.

The RxFIFO full status (Chnl\_int\_sts\_reg0 [RFUL] and Channel\_sts\_reg0 [RFUL] bits) indicates that the RxFIFO is full and prevents any further data from being loaded into the RxFIFO. When a space becomes available in the RxFIFO, any character stored in the receiver will be loaded. A threshold trigger (RTRIG) can be setup on the RxFIFO fill level. The Receiver Trigger Level register (Rcvr\_FIFO\_trigger\_level0) can be used to setup this value, such that the trigger is set when the RxFIFO fill level transitions this programmed value. The Range is 1 to 63.

#### **Receiver Data Capture**

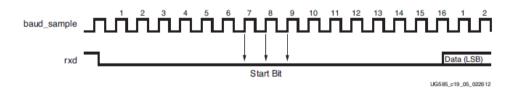

The UART continuously over-samples the UARTx\_RxD signal using UARTx REF\_CLK and the clock enable (baud sample). When the samples detect a transition to a Low level, it can indicate the beginning of a start bit. When the UART senses a Low level at the UART\_RxD input, it waits for a count of half of BDIV baud rate clock cycles, and then samples three more times. If all three bits still indicate a Low level, the receiver considers this to be a valid start bit, as illustrated in Figure 3-8 for the default BDIV of 15.

Figure 3-8 Default BDIV Receiver Data Stream

The logic value is determined by majority voting; two samples having the same value define the value of the data bit. When the value of a serial data bit has been determined, it is shifted to the receive shift register. When a complete character has been assembled, the contents of the register are then pushed to the RxFIFO. The Receiver has some errors and interrupts which are illustrated as follows:

## • Receiver Parity Error:

Each time a character is received, the receiver calculates the parity of the received data bits in accordance with the uart.mode\_reg0 [PAR] bit field. It then compares the result with the received parity bit. If a difference is detected, the parity error bit is set = 1, uart.Chnl\_int\_sts\_reg0 [PARE]. An interrupt is generated, if enabled.

## • Receiver Framing Error:

When the receiver fails to receive a valid stop bit at the end of a frame, the frame error bit is set =1, uart.Chnl\_int\_sts\_reg0 [FRAME]. An interrupt is generated, if enabled.

## • Receiver Overflow Error:

When a character is received, the controller checks to see if the RxFIFO has room. If it does, then the character is written into the RxFIFO. If the RxFIFO is full, then the controller waits. If a subsequent start bit on RxD is detected and the RxFIFO is still full, then data is lost and the controller sets the Rx overflow interrupt bit, uart.Chnl\_int\_sts\_reg0 [ROVR] = 1. An interrupt is generated, if enabled.

## • Receiver Timeout Mechanism:

The receiver timeout mechanism enables the receiver to detect an inactive RxD signal (a persistent High level). The timeout period is programmed by writing to the uart.Rcvr\_timeout\_reg0 [RTO] bit field. The timeout mechanism uses a 10-bit decrementing counter. The counter is reloaded and starts counting down whenever a new start bit is received on the RxD signal, or whenever software writes a 1 to uart.Control\_reg0 [RSTTO] (regardless of the previous [RSTTO] value).

If no start bit or reset timeout occurs for 1,023-bit periods, a timeout occurs. The Receiver timeout error bit [TIMEOUT] will be set in the interrupt status register, and the [RSTTO] bit in the Control register should be written with a 1 to restart the timeout counter, which loads the newly programmed timeout value. It is built as decrementing counter that moves downwards towards zero.

When the decrementing counter reaches 0, the receiver timeout occurs and the controller sets the timeout interrupt status bit uart.Chnl\_int\_sts\_reg0 [TIMEOUT] = 1. If the interrupt is enabled (uart.Intrpt\_mask\_reg0 [TIMEOUT] = 1), then the IRQ signal to the PS interrupt controller is asserted. Whenever the timeout interrupt occurs, it is cleared with a write back of 1 to the Chnl\_int\_sts\_reg0 [TIMEOUT] bit. Software must set uart.Control\_reg0 [RSTTO] = 1 to generate further receive timeout interrupts.

## I/O Mode Switch

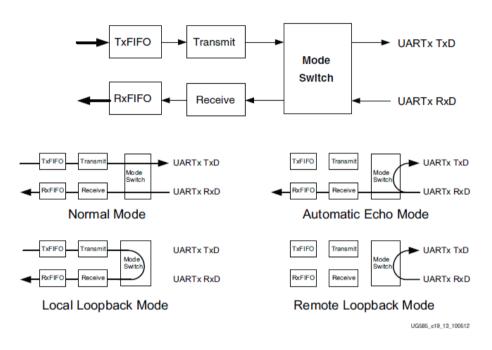

The mode switch controls the routing of the RxD and TxD signals within the controller as shown in Figure 3-9. The loopback using the mode switch occurs regardless of the MIO-EMIO routing of the UART TxD/RxD I/O signals. There are four operating modes as shown in Figure 3-9. The mode is controlled by the uart.mode\_reg0 [CHMODE] register bit field: normal, automatic echo, local loopback and remote loopback.

Figure 3-9 UART Mode Switch for TxD and RxD

- Normal Mode: Normal mode is used for standard UART operations.

- Automatic Echo Mode: Echo mode receives data on RxD and the mode switch routes the data to both the receiver and the TxD pin. Data from the transmitter cannot be sent out from the controller.

- Local Loopback Mode: Local loopback mode does not connect to the RxD or TxD pins. Instead, the transmitted data is looped back around to the receiver.

- **Remote Loopback Mode:** Remote loopback mode connects the RxD signal to the TxD signal. In this mode, the controller cannot send anything on TxD and the controller does not receive anything on RxD.

## **UART0-to-UART1** Connection

The I/O signals of the two UART controllers in the PS can be connected. In this mode, the RxD and CTS input signals from one controller are connected to the TxD and RTS output signals of the other UART controller by setting the slcr.LOOP [UA0\_LOOP\_UA1] bit = 1. The other flow control signals are not connected. This UART-to-UART connection occurs regardless of the MIO-EMIO programming.

## 3.5.4 Status and Interrupts

## **Interrupt and Status Registers**

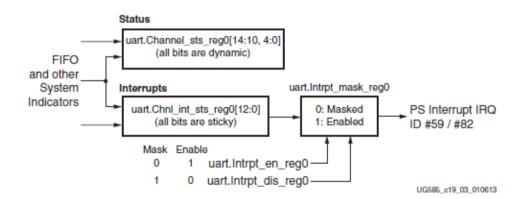

There are two status registers that can be read by software. Both show raw status. The Chnl\_int\_sts\_reg0 register can be read for status and generate an interrupt. The Channel\_sts\_reg0 register can only be read for status. The Chnl\_int\_sts\_reg0 register is sticky; once a bit is set, the bit stays set until software clears it. Write a 1 to clear a bit. This register is bit-wise ANDed with the Intrpt\_mask\_reg0 mask register. If any of the bit-wise AND functions have a result = 1, then the UART interrupt is asserted to the PS interrupt controller.

• Channel\_sts\_reg0: Read-only raw status of the UART. Writes are ignored

The various FIFO and system indicators are routed to the uart.Channel\_sts\_reg0 register and/or the uart.Chnl\_int\_sts\_reg0 register as shown in Figure 3-10.

Figure 3-10 Interrupts and status signals

## Interrupt Mask Register

Intrpt\_mask\_reg0 is a read-only interrupt mask/enable register that is used to mask individual raw interrupts in the Chnl\_int\_sts\_reg0 register:

- If the mask bit = 0, the interrupt is masked.

- If the mask bit = 1, the interrupt is enabled.

This mask is controlled by the write-only Intrpt\_en\_reg0 and Intrpt\_dis\_reg0 registers. Each associated enable/disable interrupt bit should be set mutually exclusive (e.g., to enable an interrupt, write 1 to Intrpt\_en\_reg0[x] and write 0 to Intrpt\_dis\_reg0[x]).

## **Channel Status**

These status bits are in the Channel\_sts\_reg0 register.

- **TACTIVE:** Transmitter state machine active status. If in an active state, the transmitter is currently shifting out a character.

- **RACTIVE:** Receiver state machine active status. If in an active state, the receiver is has detected a start bit and is currently shifting in a character.

- **FDELT:** Receiver flow delay trigger continuous status. The FDELT status bit is used to monitor the RxFIFO level in comparison with the flow delay trigger level.

## Non-FIFO Interrupts

These interrupt status bits are in the Chnl\_int\_sts\_reg0 register.

- **TIMEOUT:** Receiver Timeout Error interrupt status. This event is triggered whenever the receiver timeout counter has expired due to a long idle condition.

- **PARE:** Receiver Parity Error interrupt status. This event is triggered whenever the received parity bit does not match the expected value.

- **FRAME:** Receiver Framing Error interrupt status. This event is triggered whenever the receiver fails to detect a valid stop bit.

- **DMSI:** indicates a change of logic level on the DCD, DSR, RI or CTS modem flow control signals.

This includes High-to-Low and Low-to-High logic transitions on any of these signals.

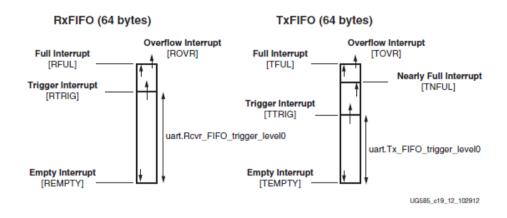

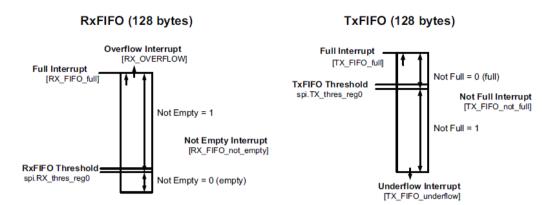

#### FIFO Interrupts

The status bits for the FIFO interrupts are illustrated in Figure 3-11. These interrupt status bits are in the Channel Status (uart.Channel\_sts\_reg0) and Channel Interrupt Status (uart.Chnl\_int\_sts\_reg0) registers with the exception that the [TOVR] and [ROVR] bits are not part of the uart.Channel\_sts\_reg0 register.

Figure 3-11 UART RxFIFO and TxFIFO Interrupt

The FIFO trigger levels are controlled by these bit fields:

- uart.Rcvr\_FIFO\_trigger\_level0[RTRIG], a 6-bit field

- uart.Tx\_FIFO\_trigger\_level0[TTRIG], a 6-bit field

# 3.5.5 Block Flow Building

Building of the UART block of the Zynq-7000 board has passed through many phases. After reading the manual, the UART is set to be divided into smaller blocks which are FIFO-TX, FIFO-RX, TX-controller, RX-controller, Sampler, Baud-rate-generator, Clock-divider, Main-controller and APB-interface. Each small block is concerned about doing one thing. Division of the functionality is very important and will be revealed later in the integration phase. It helps in detection of the errors and the problems that appears during the testing phase. Also, the interrupts are so important. There are two ways to add them to the functionality either from the beginning and test the functionality or build the block in normal case then add the interrupts to it later and test the functionality at the end. The first is the hardest to think about the interrupts while building but we chose it as to think of each smaller block as one big picture.

Moving to the building flow, the start comes from building the TX and RX controllers. It was a great challenge. They are responsible for the formation of the frame to be transmitted and the reception of the frame while receiving. The main challenge in those two blocks is choosing the most suitable states for those blocks as mentioned in the state diagrams.

The TX-controller is divided into 6 main states which are Idle, Start, Data, Parity, Stop, Break. The Idle state is the state where the TX keeps the bus idle by sending 1 on it. The Start state is responsible for getting down from 1 to 0 this trigger represents the start of data frame. The data state is the state where the data is sent bit by bit according to their size determined by frame characters either 6, 7 or 8. The parity state is adding a parity bit to the frame which is one of the following (even parity, odd parity, zero, mark, or no parity).

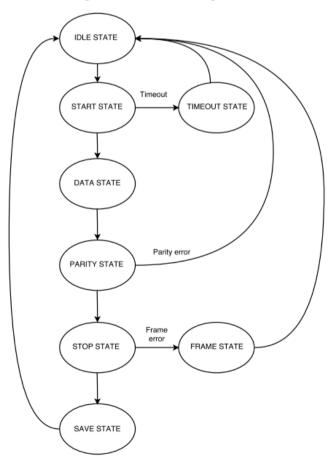

The Stop state which puts the number of stop bits added to the frame. The break state is recently added to halt the transmitter when it works as modem. The following state diagram in fig-x illustrates the previous explanation. Moving to the receiver state machine it is almost like the TX one except for some new things. The RX state machine works as follows with the following states (Idle, Start, Data, Parity, Stop, Break, Timeout, Parity, Frame, Save). First, IDLE state is the state where the RX is idle. Start state here unlike the receiver differs somehow through having timeout counter to detect the start bit but if it is not found it goes to Timeout state then to Idle again.

Moving to Data state, it ensures the reception of the data bit by bit and samples it using sampler block. Then, the Parity state appears to have different role in the RX as the block calculates the parity of the received data and compare them to the received parity bit. If it is true, it proceeds to the next state. But if it is false, it goes to the Parity state where parity interrupt is raised then moves to idle state. Detecting the stop bits is the last part in receiving the frame. If they are correctly received, it will go to save state to save data. If not, it will go to Frame state triggering Frame interrupt then to Idle state.

The Save state is to save the data to the FIFO-RX and return back to Idle state. The state diagram of the receiver is illustrated in Figure 3-12.

Figure 3-13 RX state diagram

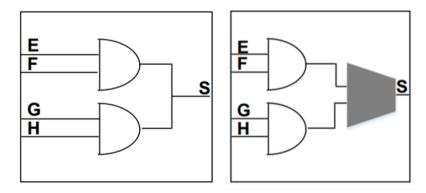

After setting those controllers, it is the role of the testing to ensure that those two blocks are achieving the required functionality. After building the TX and RX controllers, the two FIFOs are then built. The FIFOs are like a small memory to save the data. Each FIFO can hold till 64 bytes. The challenge is how to get round in the FIFO when the pointers reach the end. It is solved through a trick of setting the writer and reader pointers to move in double the size of the FIFO (128 bytes). It is abstracted from the pointers in data structure algorithms. The FIFOs have to be interfaced from the two sides. The first with the TX,RX controllers mentioned above. The other side with the main controller to get the bytes in TX\_FIFO and out from the RX\_FIFO will be discussed later. The interrupts concerning the FIFO are set inside the block.

Besides, building two of the important blocks that will help in reaching the results of the long simulation time which are the Baud-rate-generator and the Clock-divider. These two blocks are concerned with generating the baud rate and baud sample from the main clock coming to UART. We use hierarchal reference in those two blocks. The upper is the Baud-rate-generator and inside which embedded the Clock-divider. The value of the division will play an important role in proving the point as increasing the value of the division will make the simulation takes long time to show the results that will be mentioned later. The TX and RX controllers works on the baud rate generated form Baud-rate-generator. They are all connected through the main controller. The division values are defined through registers and they have reset default values. There is a small block which is the sampler, it is one of the blocks used in the receiver. The sampler is based on Majority check. It samples the bit three times and if it has majority of 2 or more '1's' it will give one otherwise will give zero. It is used in the receiver controller to detect whether the received bit is 1 or 0. It is built as the specifications mentioned in the manual with getting three samples.

Then, the first integration occurs between the previous blocks to be tested together that they meet the functionality required. The integration requires tracking all signals of the blocks to be totally connected and passing the tests on sending and receiving bits. It was a challenge to generate many tests in order to edit those blocks on that small scale. So that to be ready in further building of the coming blocks.

Figure 3-14 Controllers, FIFOs and Baud Rate generator

Moving to building the main controller, the master block that controls all the previous blocks and connect them together. It contains the registers and the connecting signals between the blocks. This block connects the two FIFOs with the TX,RX controllers and managing the clock for the blocks. Besides, it connects the FIFOs to the registers that are filled by the APB-interface through the databus. It handles the control of the overall system to meet the functionality with handling the interrupts. In addition to that this block is responsible to connect the internal blocks with the outside pins where the input is entered and the output is passed to. It is the brain of the UART where all the decisions are taken.

After the main controller is built and connecting all blocks under it, it is the time for validating this new integration. A rough test passes on the signals to ensure meeting the specifications. It is one of the long phases as it requires to do many edits to the blocks and the connections between them. It was one of the hardest phases and it took a very long time. After ensuring that everything is working as expected through the UART. It is time to go to the last part in the building of the UART.

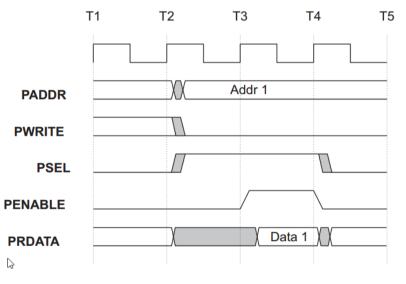

Building the APB was the end of the building phase of the UART. The APB-interface includes all the interfaces of the UART with the external system. It has the connections with the APB and the external I/O pins. The APB-interface block is concerned with writing and reading from the databus and getting the address from the address bus. Besides, getting the inputs and passing the outputs to the pins. It acts as the link between the main-controller and the external system. The testing phase on the new integration to ensure that the block is fully connected and is meeting all the specifications.

# 3.6 SPI

The Serial Peripheral Interface (SPI) bus controller enables communications with a variety of peripherals such as memories, temperature sensors, pressure sensors, analog converters, real-time clocks, displays, and any SD card with serial mode support. The SPI controller can function in master mode and in slave mode.

In master mode, the controller drives the serial clock and slave selects with an option to support SPI's multi-master mode. The serial clock is derived from the PS clock subsystem. The controller initiates messages using up to 3 individual slave select (SS) output signals that can be externally expanded.

The controller reads and writes to slave devices by writing bytes to the 32-bit read/write data port register. In slave mode, the controller receives the serial clock from the external device and uses the SPI reference clock to synchronize data capture. The slave mode includes a programmable start detection mechanism when the controller is enabled while the SS is asserted.

The read and write FIFOs provide buffering between the SPI I/O interface and the software servicing the controller via the APB slave interface. The FIFO are used for both slave and master I/O modes.

# 3.6.1 Features

Each SPI controller is configured and controlled independent, they include the following features:

- Four wire bus MOSI, MISO, SCLK, and SS

- up to 3 slave selects for master mode

- Full-duplex operation offers simultaneous receive and transmit

- 32-bit register programming via APB slave interface

- Memory mapped read/write data ports for Rx/Tx-FIFOs (byte-wide)

- 128-byte read and 128-byte write FIFOs

- Programmable FIFO thresholds status and interrupts

- Master I/O mode

- Manual and auto start transmission of data

- Manual and auto slave select (SS) mode

- Slave select signals can be connected directly to slave devices or expanded externally

- Programmable SS and MOSI delays

- Slave I/O mode

- Programmable start detection mode

- Programmable clock phase and polarity (CPHA, CPOL)

- Programmable interrupt-driven device or poll status

#### Device MIO – EMIO Boundary Routing IRQ ID# {58, 81} SPI Interface Controller MIO Slave Pins APB port Interconnect CPU 1x clock SPI{0, 1} CPU\_1x reset Control Registers EMIO Signals SPI REF reset SPI REF clock Clocking

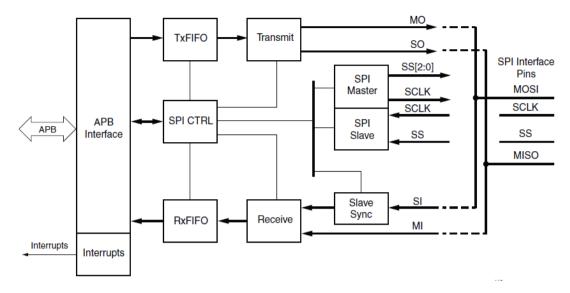

# 3.6.2 Block Diagram

Figure 3-15 SPI system block diagram

The system block diagram of the SPI is shown in Figure 3-15 and it consists of the following main blocks:

- 1. SPI Interface Controller: The I/O signals of controller can be routed to MIO pins or the EMIO interface. Each controller also has individual interrupts signals to the PS interrupt controller and a separate reset signal. Each controller has its own set of control and status registers.

- **2.** Clocking: The PS clock subsystem provides a reference clock to the SPI controller. The SPI reference clock is used for the controller logic and by the baud rate generator to create the SCLK clock for master mode.

- 3. MIO-EMIO: The SPI I/O signals can be routed to the MIO pins or the EMIO.

Figure 3-16 SPI functional block diagram

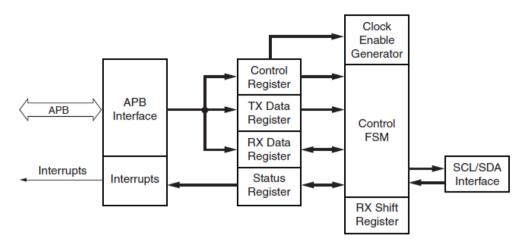

The functional block diagram of the SPI is shown in Figure 3-16 and it consists of the following main blocks:

- 1. APB Slave Interface: The 32-bit APB slave interface responds to register reads and writes, including data ports for reading and writing commands and data from and to the FIFOs. All registers transactions are 32 bits. The data ports use bits [7:0] of these ports

- 2. SPI Master Mode: When the controller operates in master mode, it drives the SCLK clock and up to 3 slave select output signals. The SS and start of transmission on MOSI can be manually controlled by software or automatically controlled by the hardware.

- **3. SPI Slave Mode:** When the controller operates in slave mode, it uses a single slave select input (SS 0). The SCLK is synchronized to the controller reference clock (SPI\_Ref\_Clk).

- 4. Tx and Rx FIFOs: Each FIFO is 128 bytes. Software reads and writes these FIFOs using the register mapped data port registers. The FIFOs bridge two clock domains; APB interface and the controller's SPI\_Ref\_Clk. Software writes to the TxFIFO in the APB clock domain and the controller reads the TxFIFO in the SPI\_Ref\_Clk domain. The controller fills the RxFIFO in the SPI\_Ref\_Clk domain and software reads the RxFIFO in the APB clock domain.

# 3.6.3 Functional Description

# Master Mode

In master mode, the SPI I/O interface can transmit data to a slave or initiate a transfer to receive data from a slave. The controller selects one slave device at the time using one of the three slave select lines.

# <u>Data Transfer</u>

The SCLK clock and MOSI signals are under control of the master. Data to be transmitted is written into the TxFIFO by software using register writes and then unloaded for transmission by the controller hardware in a manual or automatic start sequence. Data is driven onto the master output (MOSI) data pin. Transmission is continuous while there is data in the TxFIFO.

Data is received serially on the MISO data pin and is loaded 8 bits at a time into the RxFIFO. Software reads the RxFIFO using register reads. For every "n" bytes written to the TxFIFO, there will be "n" bytes stored in RxFIFO that must be read by software before starting the next transfer.

# Auto/Manual SS and Start

Data transfers on the I/O interface can be manually started using software or automatically started by the controller hardware. In addition, the slave select assertion/de-assertion can be done by the controller hardware or from software. These four combinations are shown in Table 4.

| Slave Select<br>Control | Data Transfer<br>Start Control | Manual<br>Slave<br>Select | Manual Start<br>Enable &<br>Command | Operation                                                                                                                                                                                      |

|-------------------------|--------------------------------|---------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manual SS<br>(software) | Manual Start                   | 1                         | 1                                   | Software controls the<br>slave select and must<br>issue the start<br>command to serialize<br>data.                                                                                             |

| Manual SS<br>(software) | Auto Start                     | 1                         | 0                                   | Software controls the<br>slave select, but the<br>controller hardware<br>automatically starts<br>to serialize data<br>when there is data in<br>the TxFIFO<br>(recommended for<br>general use). |

| Auto SS<br>(controller) | Manual Start | 0 | 1 | Controller hardware<br>controls the slave<br>select, but the<br>software must issue<br>the start command to<br>serialize data in the<br>TxFIFO. This mode<br>is applicable for<br>specific use cases<br>such as sending<br>small chunks of data<br>that fit into the SPI<br>controller FIFO. |

|-------------------------|--------------|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto SS<br>(controller) | Auto Start   | 0 | 0 | Controller hardware<br>controls the slave<br>select and serializes<br>data when there is<br>data in the TxFIFO.                                                                                                                                                                              |

Table 4 Auto/Manual SS and Start

## Manual SS

Software selects the manual slave select method by setting the spi.Config\_reg0 [Manual\_CS] bit = 1. In this mode, software must explicitly control the slave select assertion/de-assertion. When the [Manual\_CS] bit = 0, the controller hardware automatically asserts the slave select during a data transfer.

# Automatic SS

Software selects the auto slave select method by programming the spi.Config\_reg0 [Manual\_CS] bit = 0. The SPI controller asserts/de-asserts the slave select for each transfer of TxFIFO content on to the MOSI signal. Software writes data to the TxFIFO and the controller asserts the slave select automatically, transmits the data in the TxFIFO and then de-asserts the slave select. The slave select gets de-asserted after all the data in the Tx FIFO is transmitted. This is the end of the transfer. Software ensures the following in automatic slave select mode.

• Software continuously fills the TxFIFO with the data bytes to be transmitted, without the TxFIFO becoming empty, to maintain an asserted slave select.

• Software continuously reads data bytes received in the RxFIFO to avoid overflow. Software uses the TxFIFO and RxFIFO threshold levels to avoid FIFO under- and over-flows. The TxFIFO Not Full condition is flagged when the number of bytes in TxFIFO is less than the TxFIFO threshold level. The RxFIFO full condition is flagged when the number of bytes in RxFIFO is equal to 128.

### Manual Start

- Enable: Software selects the manual transfer method by setting the spi.Config\_reg0 [Man\_start\_en] bit = 1. In this mode, software must explicitly start the data transfer using manual start command mechanism. When the [Man\_start\_en] bit = 0, the controller hardware automatically starts the data transfer when there is data available in the TxFIFO.

- **Command:** Software starts a manual transfer by writing a 1 to the spi.Config\_reg0 [Man\_start\_com] bit. When the software writes the 1, the controller hardware starts the data transfer and transfers all the data bytes present in the TxFIFO. The [Man\_start\_com] bit is self-clearing. Writing a 1 to this bit is ignored if [Man\_start\_en] = 0. Writing a 0 to [Man\_start\_com] has no effect, regardless of mode.

#### Slave Mode

In slave mode, the controller receives messages from the external master and outputs a simultaneous reply. The controller enters slave mode when spi.Config\_reg0 [MODE\_SEL] = 0 and spi.En\_reg0 [SPI\_EN] = 1.

The SCLK latches data on the MOSI input. If the slave select input signal is High (inactive), the controller ignores the MOSI input. When the slave select is asserted, it must be held active for the duration of the transfer. If SS de-asserts during the transfer, the controller sets the spi.Intr\_status\_reg0 [MODE\_FAIL] interrupt bit. The software receives the [MODE\_FAIL] interrupt so it can abort the transfer, reset the controller, and re-send the transfer.

The error mechanism is enabled by the [Modefail\_gen\_en] bit. Data to be sent to the master is written into the TxFIFO by software and then serialized onto the master input (MISO) signal by the controller. Transmission continues while there is still data in the TxFIFO and the slave select signal remains asserted (active Low).

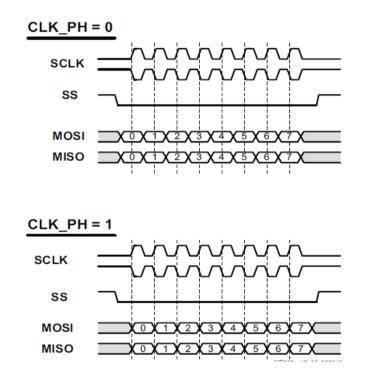

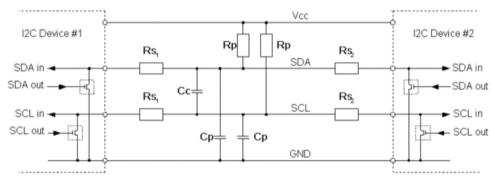

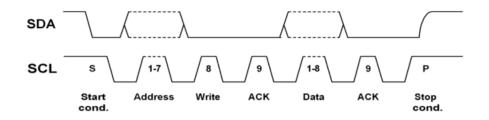

#### **Clocking**