# BUILDING SYNTHESIZABLE MODEL AND VERIFICATION ENVIRONMENT FOR AXI4-STREAM FIFO

**By** Ahmed Mohamed Yassien Aly Essam Aly Arwa Abdelaziz Abdelghany Aya Mahmoud Mahmoud Salma Khaled Hanafy Shadwa Mohsen Abdellatif

Under the Supervision of Associate Prof. Hassan Mostafa

A Graduation Project thesis submitted to Faculty of Engineering, Cairo University in Partial Fulfilment of the Requirements for the Degree of Bachelor of Science in Electronics and Electrical Communications Engineering

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT JULY 2019

Abstract

## Abstract

Streaming is a way of sending data from one block to another. The idea on streaming devices is to provide a steady flow of high speed data and to reduce overhead by using point to point connections which eliminate the need of addressing. In order to allow memory mapped access to an AXI4-Stream interface, the LogiCORE<sup>TM</sup> IP AXI4-Stream FIFO core is needed.

The core can be used to interface to AXI Streaming IPs, Similar to the LogiCORE IP AXI Ethernet core without the need to use a full Direct Memory Access (DMA) solution. The principal operation of this core allows the write or read of data packets to or from a device without any concern over the AXI Streaming interface. The AXI Streaming interface is transparent to the user.

In this thesis, the design, synthesis and verification using Universal Verification Method (UVM) of the AXI4-Stream FIFO core (Vivado design suite) are discussed.

Keywords: AXI4-Stream FIFO core, Universal Verification Methodology

Acknowledgments

# Acknowledgments

We are using this opportunity to express our gratitude to everyone who supported us throughout the graduation project. We are thankful for their aspiring guidance and friendly advice.

First, we want to thank our major advisor Dr. Hassan Mostafa for his encouragement through the whole year, his caring about following up of each stage in the project and his suggestions to solve some problems we faced during the project work.

We want to thank Mentor Graphics team; Eng. Wael Mahmoud and Eng. Haytham Shoukry, QA managers, Eng. Amr Abbas, QA team leader, Eng. Ziad Abdelati, QA Engineer and finally Eng. Michael Hany, Research assistant at ONE lab at Cairo University, for providing their time, experience to help us overcome some obstacles we faced during some stages especially when dealing with new concepts and tools.

Finally, we want to thank our families for their support, tolerance and love during this year especially during the hard times they were always there having faith in what we do. We are grateful to our families, colleagues and friends for always motivating us, without them we wouldn't have come so far.

# Table of Contents

| Abstract        |      | ii   |

|-----------------|------|------|

| Achnowledgem    | ents | iii  |

|                 | nts  |      |

| List of Figures |      | vi   |

| List of Tables  |      | viii |

| List of Acronyn | ns   | ix   |

| Chapter 1.Introduction                    | 1 |

|-------------------------------------------|---|

| 1.1.Motivation                            | 1 |

| 1.2.Problem Statement                     | 3 |

| 1.3.Solution Approach                     | 4 |

| 1.4.Organization                          | 5 |

| Chapter 2.Background                      | 6 |

| 2.1.AXI4 Protocol                         | 6 |

| 2.2.AXI4 – Lite Protocol                  | 9 |

| 2.3.AXI4 – Stream                         | 9 |

| Chapter 3. Vivado AXI4 Stream FIFO Design |   |

| 3.1.Block Introduction                    |   |

| 3.2.Design Overview                       |   |

| 3.2.1.Transmit Path                       |   |

| 3.2.2.Receive Path                        |   |

| 3.3.Individual Building Blocks            |   |

| 3.3.1.AXI4-Lite Interface                 |   |

| 3.3.2.AXI4 Interface                      |   |

| .3.3.3Register Space                      |   |

| 3.3.4.Transmit Control                    |   |

| .3.3.5Transmit FIFO Unit                  |   |

| 3.3.6.Stream Receive Interface            |   |

| .3.3.7Receive FIFO                        |   |

| .3.3.8Receive Control                     |   |

| 3.3.9.Calculation Unit                    |   |

| 3.3.10.Interrupt Interface                       |     |

|--------------------------------------------------|-----|

| Chapter 4.FPGA Synthesis and Implementation      |     |

| 4.1.Introduction                                 |     |

| 4.2.Results                                      |     |

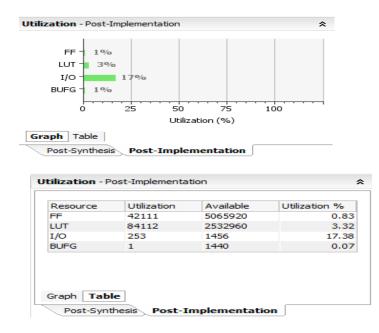

| 4.2.1.Synthesis Results                          | 109 |

| 4.2.2.Implementation Results                     | 111 |

| Chapter 5.Verification                           | 112 |

| 5.1.Introduction                                 | 112 |

| 5.2.Direct Testing                               |     |

| .5.2.1Unit Testing                               | 113 |

| 5.2.2.Integration Testing                        | 115 |

| 5.3.Universal Verification Methodology (UVM)     | 127 |

| 5.3.1.Introduction                               |     |

| 5.3.2.Overview                                   | 129 |

| 5.3.3.UVM Sequences                              | 133 |

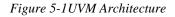

| Chapter 6.Simulation Results                     | 138 |

| 6.1.Transmit Path                                |     |

| 6.2.Receive Path                                 | 143 |

| Chapter 7. Conclusion and Future Work            | 146 |

| 7.1.Conclusion                                   | 146 |

| 7.2.Future Work                                  | 147 |

| 7.2.1.Completion of UVM testing                  | 147 |

| 7.2.2. Verification using equivalence checking   | 147 |

| 7.2.3. Verification using Questa Verification IP | 147 |

| Chapter 8.References                             |     |

# List of Figures

| Figure 2-1 VALID before READY handshake                        |     |

|----------------------------------------------------------------|-----|

| Figure 2-2 READY before VALID handshake                        | . 7 |

| Figure 3-1 Schematic of Vivado AXI4-Stream FIFO                | 13  |

| Figure 3-2 Transmit Path                                       | 14  |

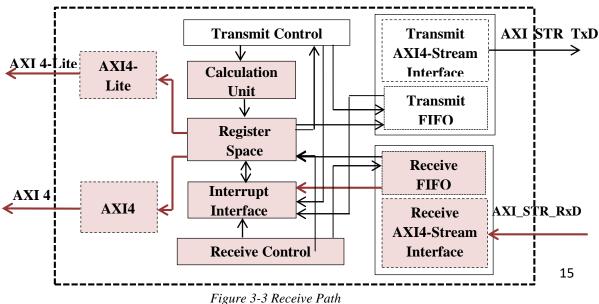

| Figure 3-3 Receive Path                                        | 15  |

| Figure 3-4 AXI4_Lite Write Operation Flow Chart                | 19  |

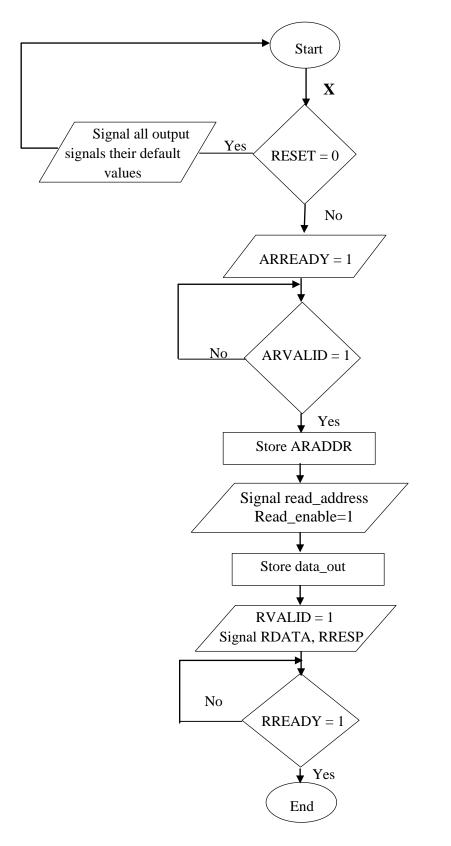

| Figure 3-5AXI4-Lite Read Operation Flow Chart                  | 20  |

| Figure 3-6 Block Diagram of AXI4-Lite                          | 21  |

| Figure 3-7 write operation FSM of AXI4-lite                    | 22  |

| Figure 3-8 Read Operation FSM of AXI4-Lite                     | 23  |

| Figure 3-9AXI4 Write tranasaction FlowChart                    | 29  |

| Figure 3-10 AXI4 Read transaction Flow Chart                   | 30  |

| Figure 3-11AXI4 block diagram                                  | 31  |

| Figure 3-12Write Operation FSM of AXI4                         | 32  |

| Figure 3-13 AXI4 Read Operation FSM                            | 34  |

| Figure 3-14 Interrupt Service Register (offset 0x00)           | 37  |

| Figure 3-15 Interrupt Service Register (offset 0x00)           | 38  |

| Figure 3-16Transmit Data FIFO Reset Register (offset 0x8)      | 39  |

| Figure 3-17 Transmit Data FIFO Vacancy Register (offset 0xC)   | 39  |

| Figure 3-18Transmit Data FIFO Data Write Port (offset 0x10)    | 39  |

| Figure 3-19 Receive Data FIFO Reset Register (offset 0x18)     | 40  |

| Figure 3-20 Receive Data FIFO Occupancy Register (offset 0x1C) | 40  |

| Figure 3-21 Receive Data FIFO Data Write Port (offset 0x20)    | 40  |

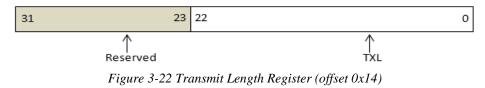

| Figure 3-22 Transmit Length Register (offset 0x14)             | 41  |

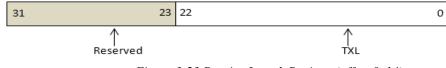

| Figure 3-23 Receive Length Register (offset 0x14)              | 41  |

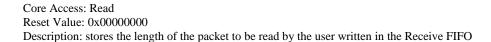

| Figure 3-24 AXI4-Sream Reset Register (offset 0x28)            | 42  |

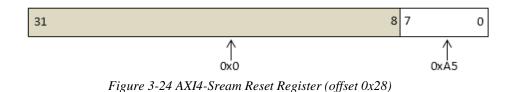

| Figure 3-25 Transmit Destination Register (offset 0x2C)        | 42  |

| Figure 3-26 Receive Destination Register (offset 0x30)         | 42  |

| Figure 3-27 Register Space block diagram                       | 43  |

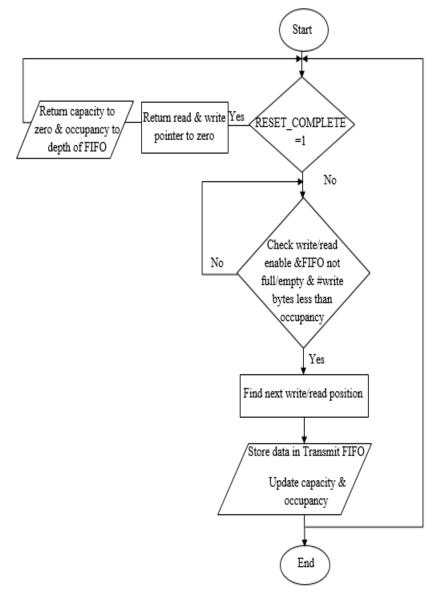

| Figure 3-28 Transmit Control functionality flow chart          | 48  |

| Figure 3-29 Transmit Control block diagram                     | 49  |

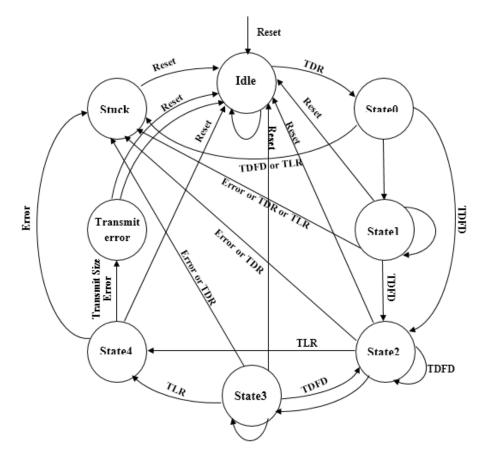

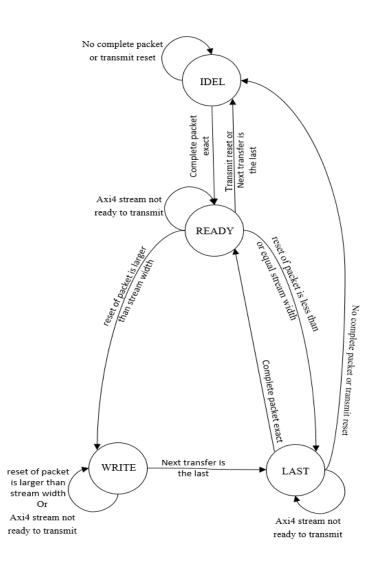

| Figure 3-30 Transmit Control FSM                               | 50  |

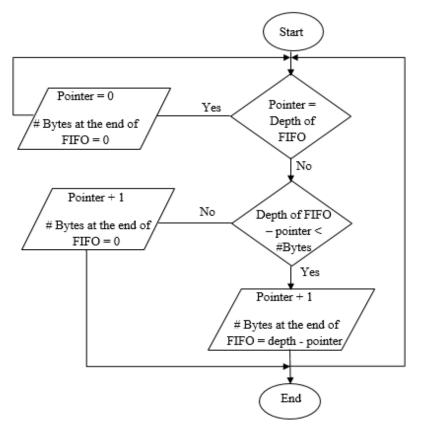

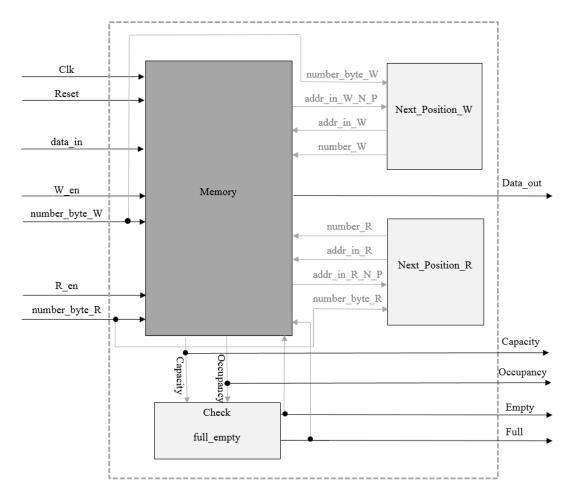

| Figure 3-31 Detecting Next position read/write flow chart      | 56  |

| Figure 3-32 Check Full and Empty of FIFO flow chart            | 57  |

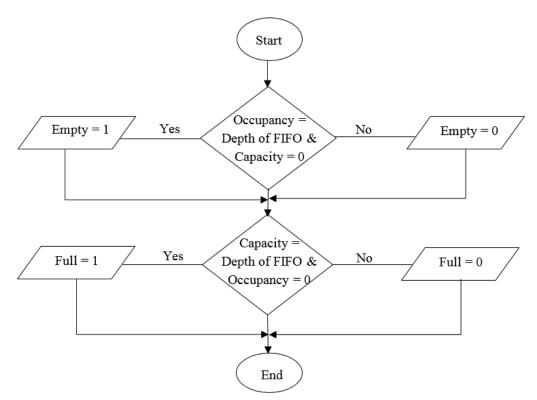

| Figure 3-33Write /Read operation in Transmit FIFO flow chart   | 58  |

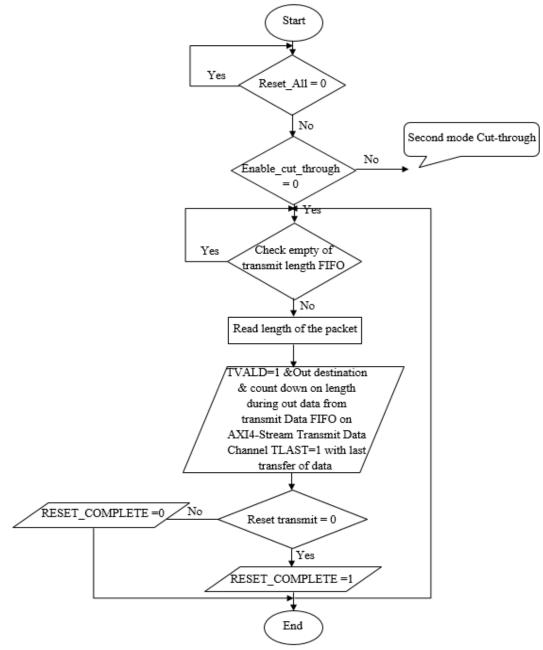

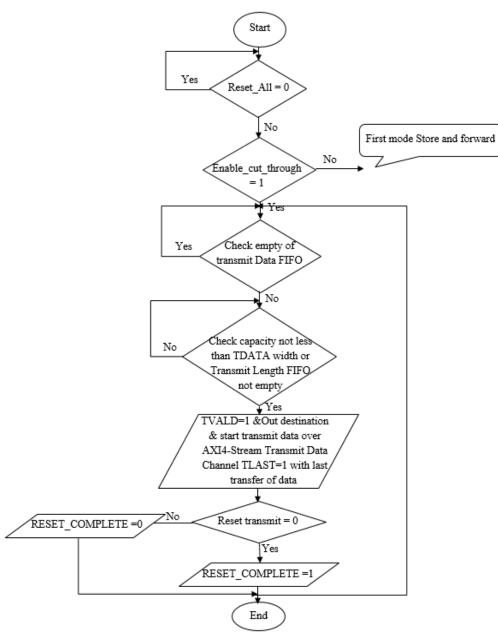

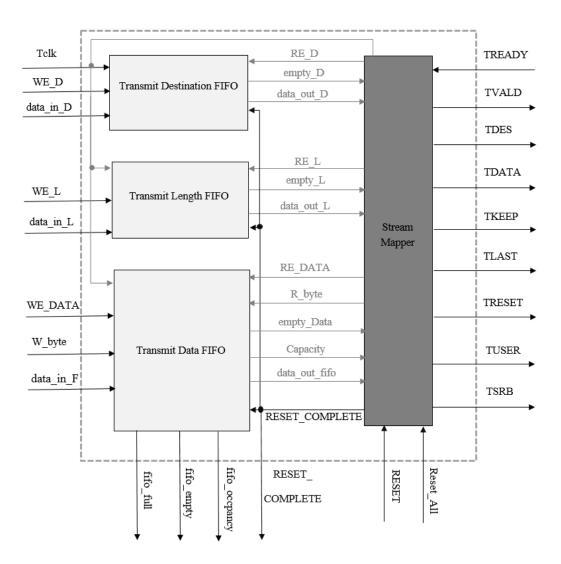

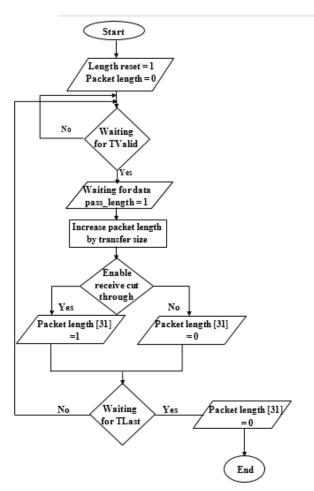

| Figure 3-34 Store and forward mode flow chart                  | 61  |

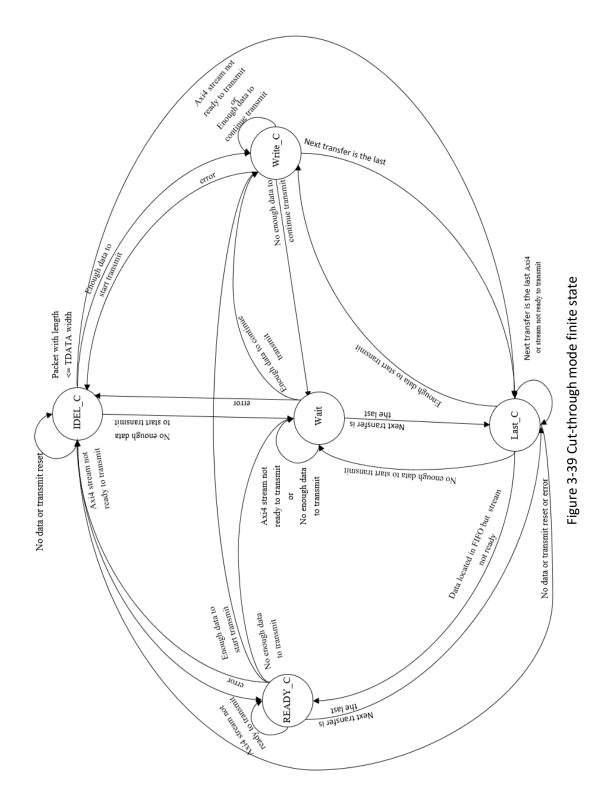

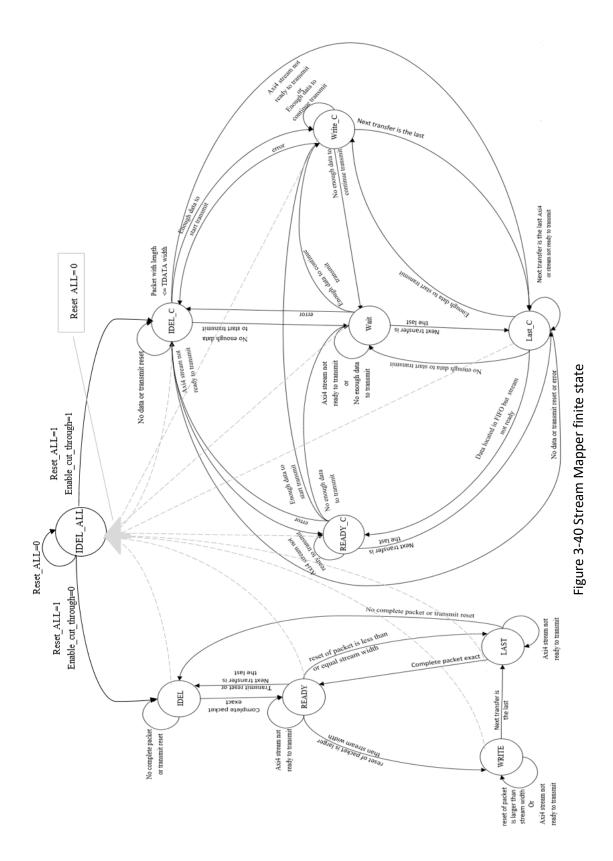

| Figure 3-35 Cut-through mode flow chart                        | 62  |

| Figure 3-36 FIFO and Stream Mapper block                       | 63  |

| Figure 3-37 Transmit Data FIFO                                 | 64  |

| Figure 3-38 Store and forward mode finite state machine        |     |

| Figure 3-39 Cut-through mode finite state machine              | 66  |

| Figure 3-40 Stream Mapper finite state machine                 |     |

| Figure 3-41 AXI4-Stream interface flow chart                   | 78  |

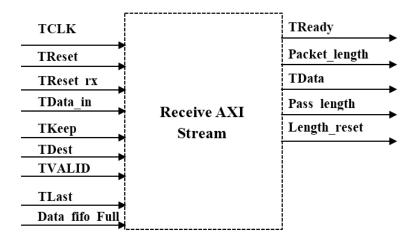

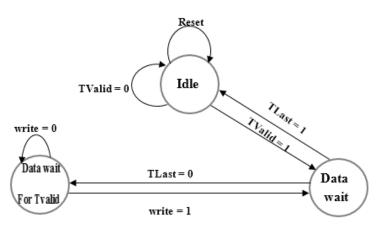

| Figure 3-42Receive AXI4 Stream block                                                |

|-------------------------------------------------------------------------------------|

| Figure 3-43 Receive AXI4 Stream FSM                                                 |

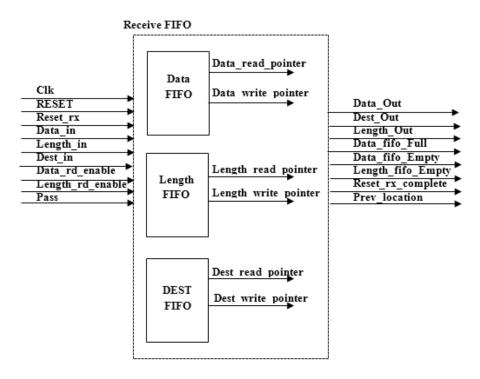

| Figure 3-44Receive FIFO block                                                       |

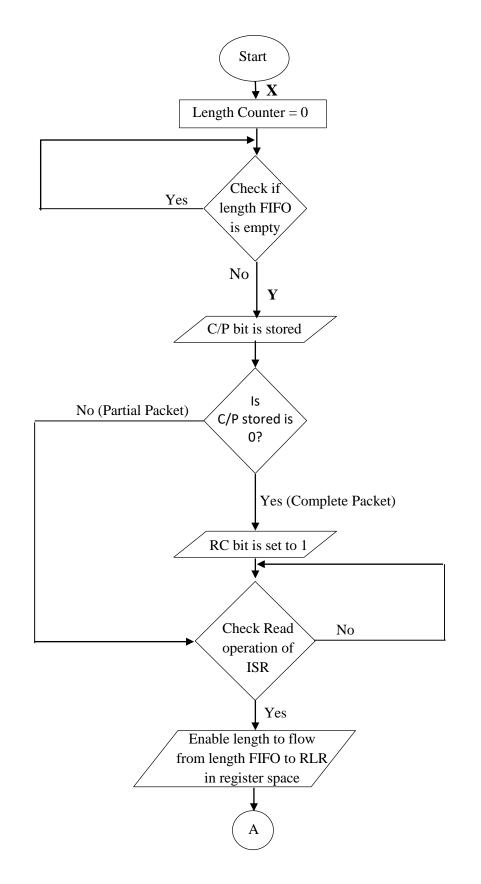

| Figure 3-45 Receive Control functionality flow chart                                |

| Figure 3-46 Receive Control FSM of both store and forward and cut-through modes     |

| Figure 3-47 TDFV functionality flow chart 101                                       |

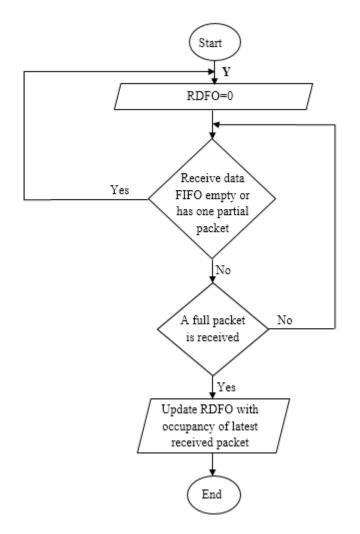

| Figure 3-48 RDFO Functionality flow chart                                           |

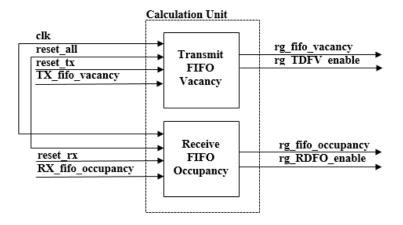

| Figure 3-49 Calculation Unit block diagram                                          |

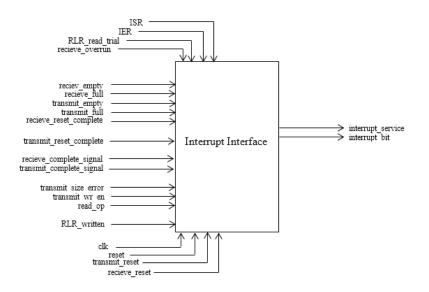

| Figure 3-50 Interrupt Interface                                                     |

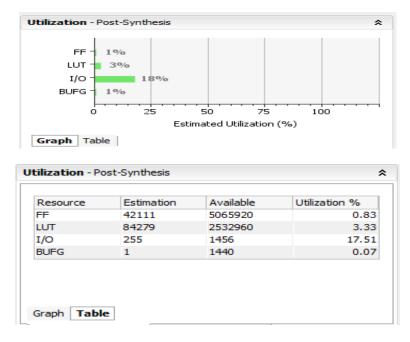

| Figure 4-1Total utilization of board resources (Post-Synthesis) 109                 |

| Figure 4-2Total utilization of board resources for each module (Post-Synthesis) 110 |

| Figure 4-3 Number of bonded IOB in design ( post-synthesis) 110                     |

| Figure 4-4Total Utilization of board resources (Post-Implementation) 111            |

| Figure 4-5Utilization of board resources for each module (Post-Synthesis) 111       |

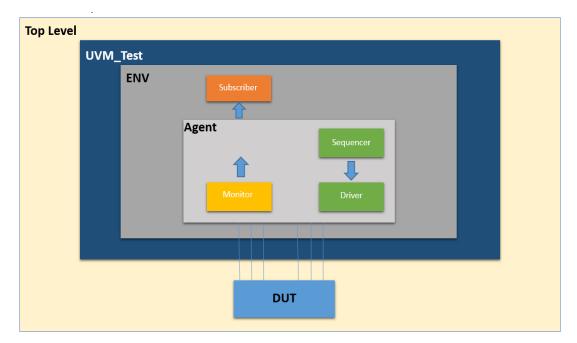

| Figure 5-1UVM Architecture                                                          |

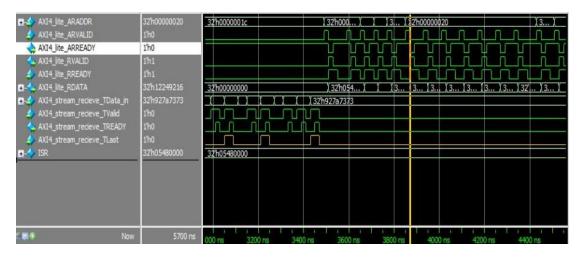

| Figure 6-1 Register Space and Control Unit simulation results1 138                  |

| Figure 6-2 Stream Interface simulation results1                                     |

| Figure 6-3 Register Space and Control Unit simulation results 2 139                 |

| Figure 6-4 Stream Interface simulation results 2                                    |

| Figure 6-5 Register Space and Control Unit simulation results 3 140                 |

| Figure 6-6 Stream Interface simulation results 3 140                                |

| Figure 6-7 Transmit path simulation result 4 141                                    |

| Figure 6-8 Transmit Path simulation result 5                                        |

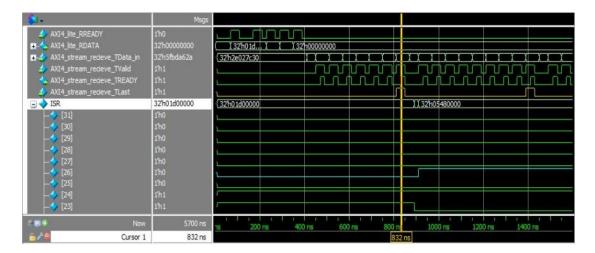

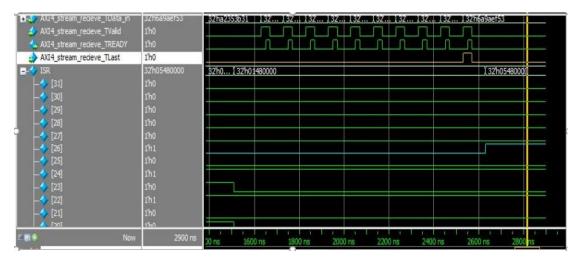

| Figure 6-9 Writing and reading random packets 143                                   |

| Figure 6-10 First word written to the core                                          |

| Figure 6-11 RC bit 26 goes high after TLAST 144                                     |

| Figure 6-12 First word written to the core                                          |

| Figure 6-13 First word read from the core                                           |

| Figure 6-14 RC bit 26 goes high after TLAST 145                                     |

# List of Tables

| Table 2-1 Supported Signals by AXI4                                  |     |

|----------------------------------------------------------------------|-----|

| Table 2-2 Supported signals by AXI4 - Lite                           | 9   |

| Table 2-3 Supported Signalsby AXI4-Stream                            | 10  |

| Table 3-1Parameters that can be configured in design                 | 12  |

| Table 3-2AXI4-Lite I/O Signals                                       |     |

| Table 3-3Write Interface States Illustration                         | 22  |

| Table 3-4Read Operation States Illustration                          |     |

| Table 3-5AXI4 I/O signals                                            |     |

| Table 3-6Write operation states illustration                         | 32  |

| Table 3-7AXI4 Write Interface FSM transition conditions illustration | 33  |

| Table 3-8AXI4 write operation FSM outputs                            | 33  |

| Table 3-9AXI4 Read operation states                                  | 34  |

| Table 3-10Register Space I/O signals                                 |     |

| Table 3-11Interrupt Service Register structure                       |     |

| Table 3-12Transmit Control I/O signals                               | 45  |

| Table 3-13Transmit Control FSM states illustration                   | 50  |

| Table 3-14Transmit Control FSM conditions                            | 51  |

| Table 3-15Trasmit Contro FSM outputs                                 | 51  |

| Table 3-16Transmit FIFO Unit I/O signals                             | 54  |

| Table 3-17 Stream Mapper FSM states                                  | 65  |

| Table 3-18 Receive AXI4 Stream I/O signals                           | 76  |

| Table 3-19Receive AXI4 Stream FSM states                             | 79  |

| Table 3-20Receive AXI4 Stream FSM conditions                         | 80  |

| Table 3-21 Receive AXI4 Stream FSM outputs                           | 80  |

| Table 3-22Receive FIFO I/O signals                                   | 82  |

| Table 3-23Receive Control I/O signals                                | 87  |

| Table 3-24 Receive Control FSM states                                |     |

| Table 3-25Receive Control FSM transition conditions                  |     |

| Table 3-26 Receive Control FSM outputs                               |     |

| Table 3-27Calculation Unit I/O signals                               | 100 |

| Table 3-28 Interrupt Interface I/O signals                           | 106 |

# List of Acronyms

| AMBA  | Advanced Microcontroller Bus Architecture         |

|-------|---------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit           |

| AXI   | Advanced Extensible Interface                     |

| DMA   | Direct Memory Access                              |

| DSP   | Digital Signal Processing                         |

| DUT   | Design Under Test                                 |

| eRM   | e Reuse Methodology                               |

| FIFO  | First-In First-Out                                |

| FPGA  | Field Programmable Gate Array                     |

| FSM   | Finite State Machine                              |

| IEEE  | Institute of Electrical and Electronics Engineers |

| IER   | Interrupt Enable Register                         |

| IP    | Intellectual property                             |

| ISR   | Interrupt Status Register                         |

| OVM   | Open Verification Methodology                     |

| PAR   | Place and Route                                   |

| RC    | Receive Complete                                  |

| RDFD  | Receive Data FIFO Data Register                   |

| RDFO  | Receive Data FIFO Occupancy Register              |

| RDFR  | Receive Data FIFO Reset Register                  |

| RDR   | Receive Destination Register                      |

| RFPE  | Receive FIFO Programmable Empty                   |

| RFPF  | Receive FIFO Programmable Full                    |

| RLR   | Receive Length Register                           |

| RPORE | Receive Packet Overrun Read Error                 |

- RPUE Receive Packet Underrun Error

- RPURE Receive Packet Underrun Read Error

- RRC Receive Reset Complete

- RTL Register Transfer Logic

- RX Receive

- SoC System-on-Chip

- SRR AXI4-Stream Reset Register

- TC Transmit Complete

- TDFD Transmit Data FIFO Data Write Port

- TDFV Transmit Data FIFO Vacancy Register

- TDR Transmit Destination Register

- TFDR Transmit FIFO Data Register

- TFPE Transmit FIFO Programmable Empty

- TFPF Transmit FIFO Programmable Full

- TLM Transaction-Level Modeling

- TLR Transmit Length Register

- TPOE Transmit Packet Overrun Error

- TRC Transmit Reset Complete

- TSE Transmit Size Error

- TX Transmit

- UUT Unit Under Test

- UVM Universal Verification Methodology

Chapter 1

# Chapter 1. Introduction

In this thesis, we are going to design and verify using UVM the AXI4 Stream FIFO that deals with some of AMBA 4.0 protocols such as AXI4, AXI4-Lite and AXI4-Stream.

## **1.1. Motivation**

The Advanced Microcontroller Bus Architecture (AMBA) protocol is a registered trademark of ARM Limited. It's an open standard, on-chip interconnect requirement for the connection and management of functional blocks in a System-On-Chip (SoC). It facilitates easy implementation of different macro functions operating at different frequencies (High frequency), and also facilitates right-first-time development of multi-processor designs with large numbers of controllers and peripherals. The AMBA protocol is technology independent, since it is implemented for any operating frequency range [1].

The scope of AMBA has gone far beyond microcontroller devices, and is at the present widely used on a range of ASIC and SoC parts including applications processors used in modern portable mobile devices like Smartphones.

AMBA was introduced by ARM Ltd in 1996. The first AMBA buses were highly developed Advanced System Bus (ASB) and Advanced Peripheral Bus (APB). In its 2nd version in 1999, AMBA 2.0, ARM added AMBA High-performance Bus (AHB) that is a single clock-edge procedure. In 2003, ARM introduced the 3rd generation, AMBA 3.0, with Advanced Extensible Interface (AXI) to reach even high performance inter-connects. In 2010, ARM introduced the 4<sup>th</sup> generation, AMBA 4.0, these includes the second version of AXI, AXI4. AXI4 provides improvements and enhancements to any Intellectual Property (IP) as it provides benefits to productivity, flexibility and availability [2]:

- Productivity: Developers need to learn only a single protocol for IP by standardizing on the AXI interface.

- **Flexibility:** There are three types of AXI4 which depends on the application:

- 1. AXI4 is for memory mapped interfaces and allows burst up to 256 data transfer cycles with just a single address phase.

- 2. AXI4-Lite is a light-weight, single transaction memory mapped interface. It has a small logic footprint and is a simple interface to work with both in design and usage.

- 3. AXI4-Stream is for high streaming data that can burst an unlimited amount of data.

- Availability: Many IP providers support the AXI protocol.

#### **1.2. Problem Statement**

There are a lot of differences between AXI4, AXI-Lite and AXI4-Stream as AXI4-Stream removes the requirement for an address phase altogether and allows unlimited data burst size. AXI4-Stream interfaces and transfers do not have address phases and are therefore not considered to be memory-mapped, unlike AXI4 and AXI4-Lite that are used for memory mapped interfaces.

Both AXI4 and AXI4-Lite interfaces consist of five different channels: Write Address Channel, Write Data Channel and Write Response Channel for Write transactions. Read Address Channel and Read Data Channel for Read transactions. Data can move in both directions between the master and the slave simultaneously, and data transfer sizes can vary. The limit in AXI4 is a burst transaction of up to 256 data transfers but AXI4-Lite allows only one data transfer per transaction as bursting is not supported.

The AXI4-Stream protocol defines a single channel for transmission of streaming data. The AXI4-Stream channel is modeled after the Write Data channel of the AXI4. Unlike AXI4, AXI4-Stream interfaces can burst an unlimited amount of data. There are additional, optional capabilities described in AXI Stream Specification [3]. The specification describes how AXI4-Stream-compliant interfaces can be split, merged, interleaved, upsized, and downsized. Unlike AXI4, AXI4-Stream transfers cannot be reordered.

The AXI4-Stream interface also supports a wide variety of different stream types such as: Transfer which is a single transfer of data across an AXI4-Stream interface, Packet which is a group of bytes that is similar to an AXI4 burst and Frame which is the highest level of byte grouping in an AXI-Stream that contains an integer number of packets unlike AXI4 that supports only bursts.

As the transactions are different between AXI4/AXI4-Lite and AXI4-Stream, the communication between these blocks would be difficult if they are in the same design unless there is an intermediate block to facilitate communication between them.

Note: Further information about each protocol will be discussed in chapter2.

3

### **1.3. Solution Approach**

If the communication is required between AXI4/AXI4-Lite and AXI4-Stream, Conversion of transactions between these interfaces (in both directions) is essential to make communication between them possible. At this point, the need for an intermediate block arises to make this mission, which is the role of AXI4-Stream FIFO.

AXI4 Stream FIFO converts from AXI4/AXI4-Lite transactions to AXI4-Stream transactions in one direction which is called the transmit path and converts from AXI4-Stream transactions to AXI4/AXI4-Lite transactions in the other direction which is called the receive path. These two paths are completely independent.

AXI4 Stream FIFO also allows memory mapped access to an AXI-Stream interface. The principal operation is to allow the write or read of data packets to or from a device without any concern over the AXI-Stream interface signaling. The AXI-Stream interface is transparent to the user.

### 1.4. Organization

The following chapters discuss Vivado AXI4-Stream architecture, the AXI4 protocols, the design blocks and its implementation, and testing of the design. The remainder of this thesis is organized as follows:

Chapter 2 provides background information on AXI protocols such as AXI4, AXI4-Lite and AXI4-Stream, discusses its architecture and the most important signals used.

Chapter 3 discusses Vivado AXI4-Stream FIFO design, provides information about the blocks and its implementation, block diagrams, flow charts and finite state machines that explain the functionality of each block in the transmit and receive paths.

Chapter 4 provides results of the synthesis and implementation of Vivado AXI4-Stream FIFO using Vivado suite showing the number of resources utilized on the chosen kit which is XCVU440-FLGA2892-1-C.

Chapter 5 discusses Verification part as it includes direct testing on each block and integration testing on the whole design then constrained random testing using Universal Verification Methodology (UVM) with further explanation of the blocks used in UVM and sequences that have been tested on transmit and receive paths.

Chapter 6 provides the results of the simulation of the whole design after constrained random testing using UVM on Questa-Sim (Behavioral Simulation).

Chapter 7 provides a brief overview of the findings, draws conclusions, and recommends directions for future work.

# Chapter 2. Background

As the AXI4-Stream FIFO core deals with AXI4/AXI4-Lite and AXI4-Stream interfaces, and each of them uses a different protocol then to fully understand the functionality of the core these protocols must be illustrated first in more details before getting into the design process.

In this chapter, the important general concerns in each protocol are illustrated such as the handshaking procedure, important features, etc. and further information can be found in each protocol standard mentioned in the References.

## 2.1. AXI4 Protocol

The AXI4 protocol is a transaction based protocol which relies on the handshake of the VALID and READY signal to complete any data or information transfer, a transaction is defined as the process of exchanging of the complete set of required information between master and slave.

It is also a burst-based which means it allows the transfer of multiple words of data in one transaction unlike the AXI4 – Lite which will be discussed later, the supported burst types are as follows:

The AXI4 protocol defines five independent channels, two for read transactions and three for write transactions which are as follows:

- Write Data Channel

Read Address Channel

- Write Response Channel

Read Data Channel

- Write Address Channel

Where Address channels are responsible for carrying all required signals and control information to define the transaction, while the Data channels carry the data to be exchanged between source and destination. The Write Response channel carries the response of the destination to the write transaction whether the write was a success or an error took place. The AXI4 relies on the handshake between the VALID and READY signals between the source and destination as mentioned above, the handshake is explained as follows:

The VALID signal is generated by the source which indicates the presence of valid control information or data on the bus to the destination.

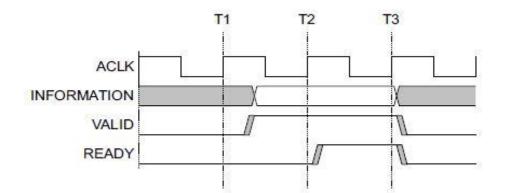

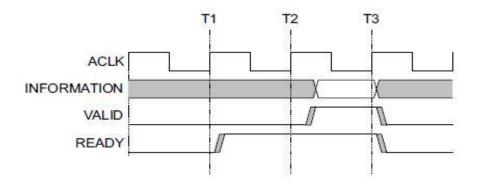

The READY signal is generated by the destination to indicate that it is ready to accept information at this moment, the transfer only takes place when both the VALID and READY signals are HIGH as shown in Figure 2-1 and 2-2.

As shown, there is no restriction on which of the two signals comes high first except for only one constraint, that the source is not allowed to wait for the READY signal to be high to assert its VALID signal, and for the READY signal, the destination can either wait for the VALID signal to be high to assert the READY or have the READY high whenever it's ready to receive information which saves one clock cycle.

Figure 2-1 VALID before READY handshake

Figure 2-2 READY before VALID handshake

| Write<br>address<br>channel | Read address<br>channel | Write data<br>channel | Read data<br>channel | Write<br>response<br>channel |

|-----------------------------|-------------------------|-----------------------|----------------------|------------------------------|

| AWADDR                      | ARADDR                  | WDATA                 | RDATA                | BRESP                        |

| AWLEN                       | ARLEN                   | WSTRB                 | RRESP                | BVALID                       |

| AWSIZE                      | ARSIZE                  | WLAST                 | RLAST                | BREADY                       |

| AWBURST                     | ARBURST                 | WVALID                | RVALID               |                              |

| AWVALID                     | ARVALID                 | WREADY                | RREADY               |                              |

| AWREADY                     | ARREADY                 |                       |                      |                              |

The Signals supported by the AXI4 are as follows in Table 2-1

| Table 2-1 | Supported | Signals | by AXI4 |

|-----------|-----------|---------|---------|

|-----------|-----------|---------|---------|

The following signals are what define the burst properties of the transaction

**AxBURST:** Determines the burst type of the transaction

AxSIZE: Determines the number of transferred bytes in each data transfer in a burst

AxLEN: Determines the number of data transfers in each transaction

Note: The "x" means that it could be for read or write channel, as an example AxBURST can be ARBURST or AWBURST.

The AXI4 protocol supports strobing on write transactions where each bit in the WSTRB signal corresponds to one byte of the WDATA (Write Data) bus, if the bit is pulled high it indicates the corresponding byte in the WDATA bus carries valid data to be stored otherwise the data on the corresponding byte is invalid, such feature is useful in unaligned memory access and in narrow bus width transfers.

### 2.2. AXI4 – Lite Protocol

Unlike AXI4, The AXI4 – Lite supports transactions of burst length of one only, thus the AxBurst, AxSIZE, AxLEN and LAST signals are not supported. The AXI4 – Lite supports the same channels and the same handshake process as the AXI4 protocol.

The Signals supported by the AXI4 - Lite are as follows in Table 2-2

| Write<br>address<br>channel | Read address<br>channel | Write data<br>channel | Read data<br>channel | Write<br>response<br>channel |

|-----------------------------|-------------------------|-----------------------|----------------------|------------------------------|

| AWADDR                      | ARADDR                  | WDATA                 | RDATA                | BRESP                        |

| AWVALID                     | ARVALID                 | WSTRB                 | RRESP                | BVALID                       |

| AWREADY                     | ARREADY                 | WVALID                | RVALID               | BREADY                       |

|                             |                         | WREADY                | RREADY               |                              |

Table 2-2 Supported signals by AXI4 - Lite

## 2.3. AXI4 –Stream

The AXI4–Stream is suitable to continuous transfer of data with low complexity, unlike the two previous protocols it only supports one channel, it also depends on the same handshake procedure between the TVALID and TREADY signals, where each time both the TVALID and TREADY are asserted together, an exchange of a beat or word of the packet to be transmitted can take place, the TLAST signal marks the packet boundary meaning that at the last beat of a packet the TREADY, TVALID and TLAST are all high.

The following byte definitions are used in this specification:

**Data byte:** A byte of data that contains valid information that is transmitted between the source and destination.

**Position byte:** A byte that indicates the relative positions of data bytes within the stream. This is a placeholder that does not contain any relevant data values that are transmitted between the source and destination.

**Null byte:** A byte that does not contain any data information or any information about the relative position of data bytes within the stream.

TSTRB signal acts as the WSTRB signal in the AXI4 protocol, where each bit of the TSTRB corresponds to one byte of the TDATA, if the bit is pulled high it indicates the corresponding byte in the TDATA bus is a Data byte to be stored otherwise the data on the corresponding byte is considered position byte (control data).

However, TSTRB is in effect only when TKEEP is asserted, otherwise if the TKEEP is low the corresponding byte is considered to be a NULL byte and must be removed from the stream bytes by the interconnect if the slave can't handle the NULL bytes.

| Signal | Description                                                           |

|--------|-----------------------------------------------------------------------|

| TDATA  | Carries the data transmitted from the source to destination           |

|        |                                                                       |

| TVALID | Generated from the source to indicate the presence of valid data on   |

|        | the bus                                                               |

| TREADY | Generated from the destination to indicate that it's ready to receive |

|        | data at this point                                                    |

| TLAST  | Generated from the source to mark the packet boundary                 |

|        |                                                                       |

| TKEEP  | A byte qualifier used to indicate whether the content of the          |

|        | associated byte must be transported to the destination.               |

| TSTRB  | A byte qualifier used to indicate whether the content of the          |

|        | associated byte is a data byte or a position byte.                    |

The Signals supported by the AXI4 -Stream in our design are shown in Table 2-3

Table 2-3 Supported Signalsby AXI4-Stream

# Chapter 3. Vivado AXI4 Stream FIFO Design

## **3.1.Block Introduction**

The AXI4-Stream FIFO v4.1 (Vivado Design Suite) is a logic core IP owned by Xilinx which is used to convert AXI4/AXI4-lite transactions to and from AXI4-Stream transactions, which is useful for interfacing between processors and data flow applications as DSP applications.

### Features supported by the core

- Independent TX and RX paths

- Simultaneous operations for both Transmit and Receive paths

- Two modes of operation: Store and Forward and Cut-Through

- Configurable FIFO depth

- Two Data interfaces for the user either AXI4 or AXI4-Lite

- Interrupts to show status of the core and occurrence of errors

### **Modes of operation**

The core supports two modes of operation

### Store and Forward Mode

In store and forward mode, the core must wait for the packet to be fully stored and its length of the full packet is written to the core before the start of packet transmission whether it was on TX or RX path, in this case the FIFO must be large enough to hold the complete packet.

### Cut-Through Mode

In Cut-Through Mode transmission behavior changes depending on whether the packet is being transmitted on the TX or RX path as follows:

**In case of TX:** The packet transmission starts when the Transmit FIFO is not empty however the last beat is transmitted only after the length of the whole packet is written to the core

**In case of RX:** The packet transmission starts as soon as a part of the packet is written into the Receive FIFO, meanwhile the packet length is stored and updated accordingly with total partial packet length, however last part of the packet is not transmitted till the length of the full packet is updated in the core

The FIFO doesn't need to be large enough to hold the complete packet

#### Interfaces

The Core offers AXI4 – Lite interface or AXI4 interface for the user to use to write or read data from the Core.

The AXI4 – Lite interface is mandatory for register access even if AXI4interface option is selected to deal with FIFO access.

This means that if AXI4 – Lite is selected then it has full access to all the registers in the register space, while if AXI4 option is selected then the AXI4 – Lite interface has access to all the registers in the register space except for the two registers responsible of writing and reading from the FIFOs while the AXI4 interface has access to those two registers only. Further information about these registers will be explained in details in section 3.3.3.

|                           | Parameter Name        | Default value |

|---------------------------|-----------------------|---------------|

| AXI4 – Lite data width    | C_S_AXI_DATA_WIDTH    | 32            |

| RX FIFO Depth             | C_RX_FIFO_DEPTH       | 512           |

| TX FIFO Depth             | C_TX_FIFO_DEPTH       | 512           |

| AXI4 Data Width           | C_S_AXI4_DATA_WIDTH   | 32            |

| AXI4 - Stream Data        | C_S_S_AXI4_DATA_WIDTH | 32            |

| Width                     |                       |               |

| Base Address for the      | C_BASEADDR            | 0             |

| Register Space            |                       |               |

| Full threshold for the    | full_threshold_data   | 0             |

| FIFOs (Amount of          |                       |               |

| locations left before the |                       |               |

| FIFO is considered        |                       |               |

| Full)                     |                       |               |

| Empty Threshold for       | empty_threshold_data  | 0             |

| the FIFOs                 |                       |               |

| Mode of operation         | enable_cut_through    | 0             |

| 1 for cut-through         |                       |               |

| 0 for store and forward   |                       |               |

Table 3-1Parameters that can be configured in design

#### Assumptions

The user is aware of the presence of the core and in order to interact with it the user needs to use correct addresses specified by the AXI4-Stream FIFO (Vivado Design Suit) to access each register via normal AXI4-Lite read or write transactions.

### **3.2. Design Overview**

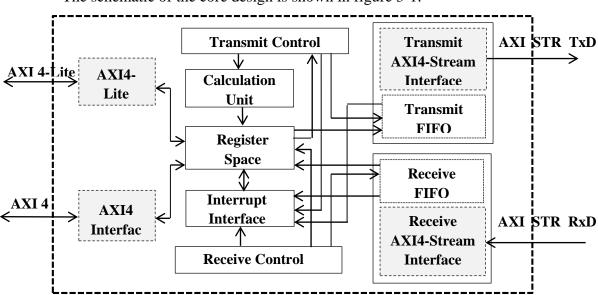

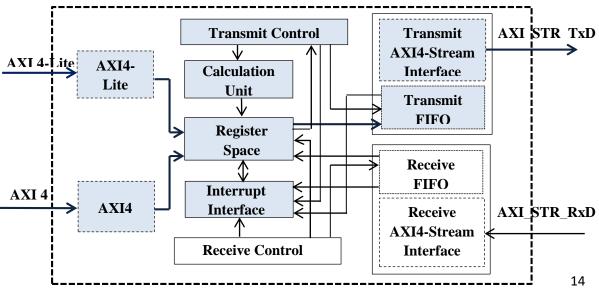

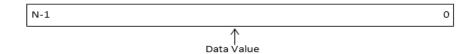

As mentioned in the features supported, the design is meant to be bidirectional which means that it has two independent paths. Both paths have nearly the same building blocks which are a Transmit/Receive control blocks, Transmit/Receive FIFOs and finally the Transmit/Receive Stream interfaces.

Clearly, the control blocks are monitoring the user's programming sequence and ensuring correct operation, while the FIFOs are the storing units for packets, and the stream interface is meant to communicate with Stream sides. The implementation of each path blocks is totally different as the Transmit and Receive logic are different. However, there may be some similar concepts between both paths such as FIFOs.

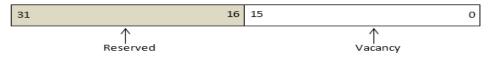

Each of the Transmit FIFO and Receive FIFO is split into 3 different FIFOs

- Data FIFO: The largest FIFO of them all and used to store the packets

- Length FIFO: Used to store the length of the packets in bytes

- Destination FIFO: Used to store destination of packets

The remaining block is the AXI4/AXI4-Lite interface which participates in both Receive and Transmit paths, as it has different channels for reading and writing operations and thus supporting full duplex operation.

In order to fully understand the core's correct operation and data flow from both interfacing sides, we need to separately study each path, which is illustrated in the upcoming two sections.

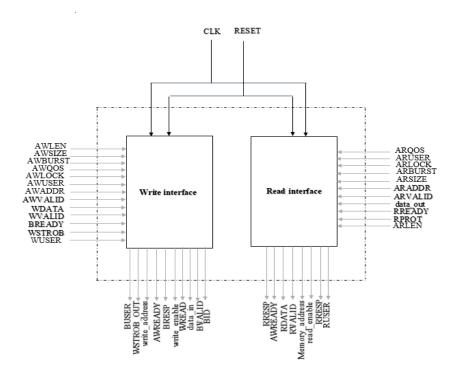

The schematic of the core design is shown in figure 3-1.

Figure 3-1 Schematic of Vivado AXI4-Stream FIFO

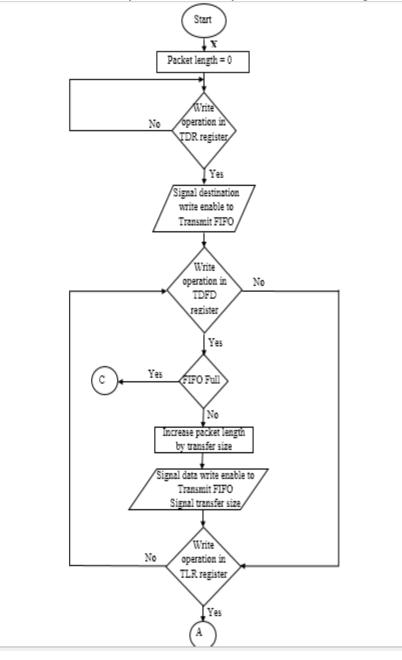

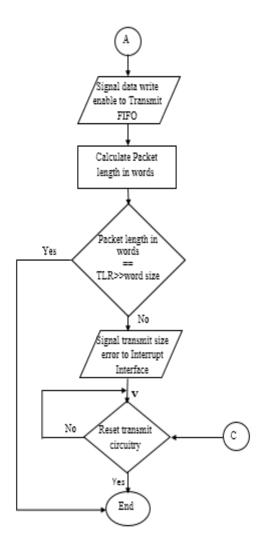

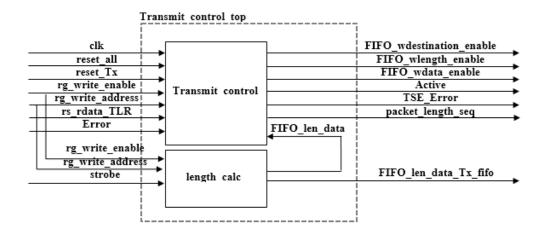

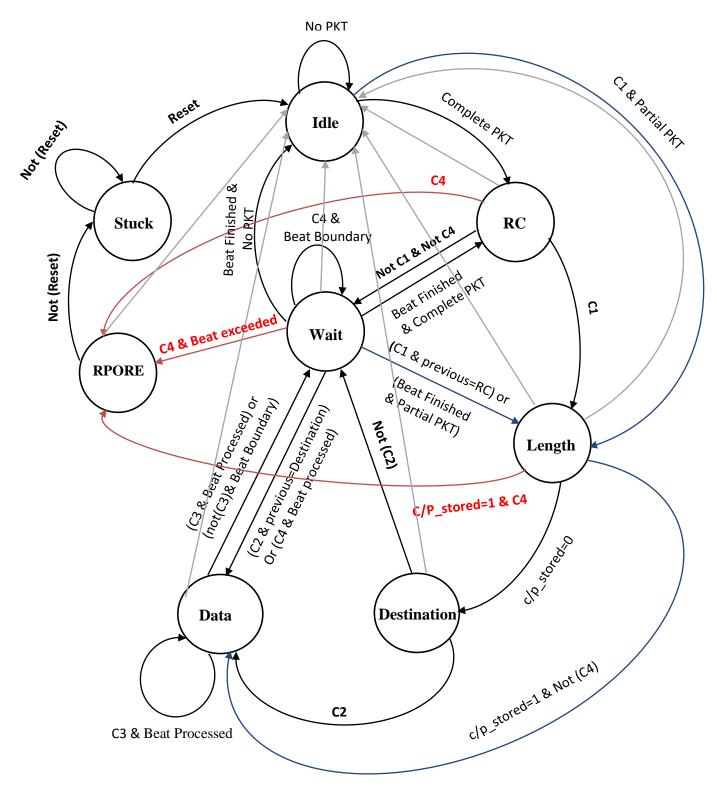

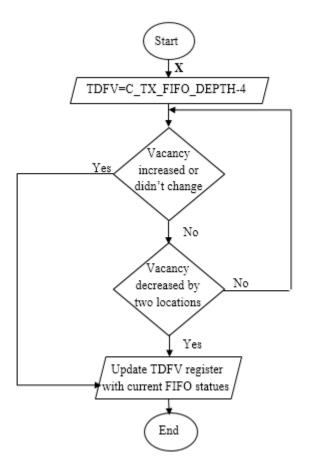

### **3.2.1.** Transmit Path

Transmit path is responsible for storing AXI4 or AXI4–Lite data write transactions in the Transmit FIFO (through passing by the Register Space first) till read transactions are initiated on the AXI4 stream interface, this is done as follows:

- 1- Programming sequence is applied from the user to the AXI4-Lite interface, passing information about the packet to the corresponding registers as destination, length and the written data.

- 2- By the end of this process the packet should be fully stored in the transmit FIFO and the Vacancy register is updated with number of vacant locations available to be written by the upcoming packets.

- 3- The packet is then transmitted over the AXI4-Stream Transmit interface when a handshake is initiated by the "application" on the other end of the interface.

The Transmit control block is responsible for coordinating the transfer of written data by the user from the Register Space to the Transmit FIFO and is also responsible for monitoring the programming sequence to allow a correct operation and to detect any error in the programming sequence that requires a reset for the Transmit Logic.

In case of Cut-Through mode of operation, the data packets that are written from the AXI4/AXI4-Lite don't need to be completely stored in the Transmit FIFO to start the transmission of the data into the AXI4-Stream interface, meaning that the transmission can start as soon as the Transmit FIFO is not empty.

Transmit path is illustrated in figure 3-2, where packet path and blocks engaged in transmission operation are highlighted.

Figure 3-2 Transmit Path

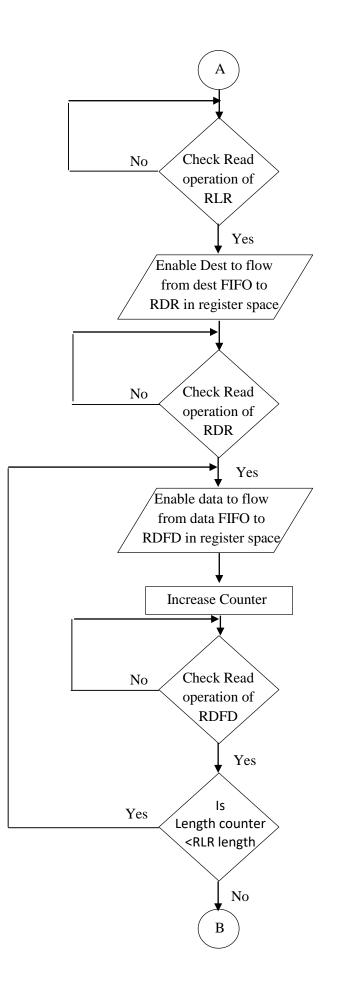

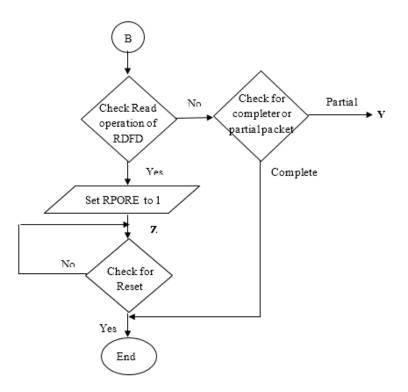

#### **3.2.2.** Receive Path

The Receive path stores incoming data from the AXI4-Stream interface in the Receive FIFO till read transactions are initiated from the user on AXI4-Lite interface, that's when the data is transferred from the Receive FIFO into AXI4/AXI4-Lite interface through the Register space, this is done as follows:

- 1- Packet received via the AXI4-Stream Receive interface is written to the Receive FIFO, and the length of the packet is calculated and written to the length FIFO, same goes for the destination FIFO.

- 2- By the end of this process the packet should be fully stored in the Receive FIFO and the Occupancy register is updated with number of locations occupied by the last successfully received packet.

- 3- The packet is then transmitted over the AXI4/AXI4-Lite interface when a handshake is initiated by the user on the other end of the interface, passing by the Register Space (the data reaches the interface through the Register Space that the user access)

The Receive control block is responsible for coordinating the transfer of written data from the Receive FIFO to the Register Space and is also responsible for monitoring the programming sequence to allow a correct operation and to detect any error in the programming sequence that requires a reset for the Receive Logic.

In case of Cut-Through mode of operation, the data packets that are written from the AXI4 Stream side don't need to be completely stored in the Receive FIFO to start the transmission of the data into the AXI4/AXI4-Lite interface, meaning that the transmission can start as soon as the Receive FIFO is not empty.

Receive path is illustrated in figure 3-3 where packet path and block engaged in the reception operation are highlighted.

#### **3.3. Individual Building Blocks**

## 3.3.1. AXI4-Lite Interface

#### Description

AXI4-Lite interface is the main interface with the core, it provides independent read and write channels where transactions mainly take place on a two stage handshake, first defines the all the required signals and control information to define the transaction and takes place when both the **AxVALID** and **AxREADY** signals are pulled high at the same time, while the second passes the data from the source to destination which takes place when both **xVALID** and **xREADY** signals are high at the same time.

The AXI4-Lite protocol supports only transactions of burst length 1, meaning that each transaction whether it was read or write is responsible for delivering one word only from the source to the destination. The supported data bus width in the core is 32 bits.

All data accesses use the full bus width, however only bytes containing valid data is stored in write transactions. Valid data is indicated by the strobe signal where each bit corresponds to one byte of the data bus.

The AXI4-Lite interface mainly deals with the Register Space within the core where all read/write operations are passed to the Register Space via the interface except when the AXI4 interface is chosen for data access to the core, then the AXI4-Lite doesn't have access to the Receive Data FIFO Data Read Port (RDFD) nor the Transmit Data FIFO Data Write Port (TDFD) in the Register Space.

# Interfacing

| Port name         | Port<br>mode | Connection        | Description                                |

|-------------------|--------------|-------------------|--------------------------------------------|

| Clk               | Input        | User              | Global interface clock                     |

| AXI4_lite_ARESET  | Input        | User              | Resets entire core                         |

| AXI4_lite_AWADDR  | Input        | User              | Address of a write transaction             |

| AXI4_lite_AWPROT  | Input        | User              | Not used                                   |

| AXI4_lite_AWVALID | Input        | User              | A valid write address is<br>available      |

| AXI4_lite_WDATA   | Input        | User              | Data of a write transaction                |

| AXI4_lite_WSTRB   | Input        | User              | Indicates which byte lanes have valid data |

| AXI4_lite_WVALID  | Input        | User              | A valid write data is available            |

| AXI4_lite_BREADY  | Input        | User              | Master can accept response<br>information  |

| AXI4_lite_ARADDR  | Input        | User              | Address of a read transaction              |

| AXI4_lite_ARPROT  | Input        | User              | Not used                                   |

| AXI4_lite_ARVALID | Input        | User              | A valid read address is available          |

| AXI4_lite_RREADY  | Input        | User              | Master can accept read data                |

| AXI4_lite_AWREADY | Output       | User              | Slave can accept read<br>information       |

| AXI4_lite_WREADY  | Output       | User              | Slave is ready to receive read<br>data     |

| AXI4_lite_BRESP   | Output       | User              | Status of a write transaction              |

| AXI4_lite_BVALID  | Output       | User              | A valid write response is available        |

| AXI4_lite_ARREADY | Output       | User              | Slave can accept read address              |

| AXI4_lite_RDATA   | Output       | User              | Data of a read transaction                 |

| AXI4_lite_RRESP   | Output       | User              | Status of a read transaction               |

| AXI4_lite_RVALID  | Output       | User              | A valid read data is available             |

| read_enable       | Output       | Register<br>space | Read enable signal                         |

| write_enable      | Output       | Register<br>space | Write enable signal                        |

| write_address     | Output       | Register<br>space | Address of a write operation               |

The AXI4-lite block contains I/O signals listed in Table 3-2.

| Memory_address | Output | Register | Address of a read operation    |

|----------------|--------|----------|--------------------------------|

|                |        | space    |                                |

| data_in        | Output | Register | Data of a write operation      |

|                |        | space    |                                |

| data_out       | Input  | Register | Data of a read operation       |

|                |        | space    |                                |

| STROBE_OUT     | Output | Transmit | Indicates which byte lanes has |

|                |        | control  | valid data                     |

Table 3-2AXI4-Lite I/O Signals

#### Functionality

The AXI4-Lite interface is responsible for read/write operations from/into Register Space; this is done through five channels:

- Write Address Channel: carries all required signals and control information to define a write transaction

- Write Data Channel: carries data written by master (source) into slave (destination)

- Write Response Channel: carries write response which gives information about write transaction statue.

- Read Address Channel: carries all required signals and control information to define a read transaction

- Read Data Channel: carries data to be read from slave (source) by master (destination)

The Write operation is done as follows

- The Address of the intended register to be written is carried out on the Write Address Channel, when the handshake between the AWVALID and AWREADY takes place, the core has read the address of the register to be written successfully

- Then the actual data is written on the Write Data Channel, when the handshake between the WVALID and WREADY takes place, this indicates that the core has read the data successfully

- The core then replies with a Response signal to feedback the write transaction statues and similarly BREADY and BVALID perform the handshake

The Read operation is done as follows

- The Address of the intended register to be read is written on the Read Address Channel, and the handshake between the ARVALID and ARREADY takes place, which indicates that the core has read the address of the register to be read successfully

- Then the data to be read is written from the core on the Read Data Channel, and the handshake between the RVALID and RREADY takes place, which indicates that the user has read the written data by the core successfully

- The RRESP signal is signaled from core to feedback the read transaction statues

Start v Ves Signal all output RESET = 0signals their default values No. AWREADY = 1No AWVALID = Yes Store AWADDR WREADY = No WVALID = 1Yes Store WDATA Signal BRESP, write\_address,, data\_in\_ BVALID=1, write\_enable=1 No BREADY = 1Yes End

Write operation in AXI4-lite is illustrated by the flow chart in figure 3-4

Figure 3-4 AXI4\_Lite Write Operation Flow Chart

Note: Resetting AXI4-lite at any point will result in going to start point (marked **X** at flow chart)

Read operation in AXI4-lite is illustrated by the flow chart in figure 3-5

Figure 3-5AXI4-Lite Read Operation Flow Chart

Note: Resetting AXI4-lite at any point will result in going to start point (marked **X** at flowchart)

#### Implementation

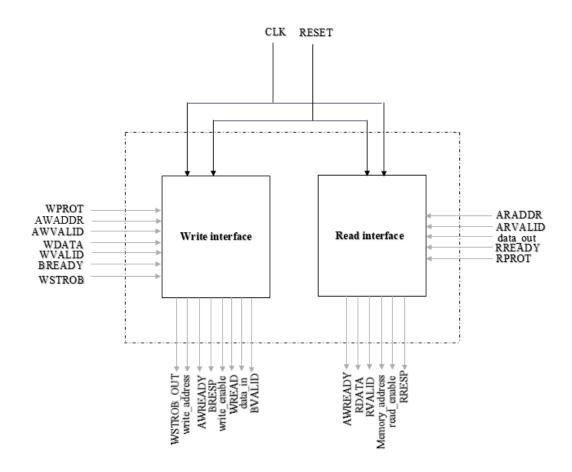

AXI4-lite unit is divided into two main blocks as illustrated in the figure 3-6; Write interface is responsible of write transactions and **Read interface** is responsible of read transactions, both of blocks are implemented by a Mealy FSM.

Figure 3-6 Block Diagram of AXI4-Lite

# Write Interface

The finite state machine states of write interface are illustrated in the table 3-3 and in figure 3-7

| State  | State | Description                                    |

|--------|-------|------------------------------------------------|

| Number |       |                                                |

| 1      | IDLE  | Idle state when AXI4-lite is not active        |

| 2      | ADDR  | Wait for AWVALID signal to be high             |

|        | WAIT  |                                                |

| 3      | DATA  | Wait for WVALID signal to be high              |

|        | WAIT  |                                                |

| 4      | DATA  | Handshaking is done and data is written in the |

|        |       | given address                                  |

| 5      | RESP  | Response of slave to indicate correct and      |

|        |       | incorrect write operation                      |

Table 3-3Write Interface States Illustration

Figure 3-7 write operation FSM of AXI4-lite

# **Read Interface**

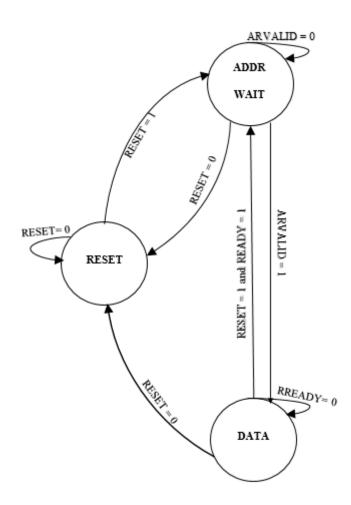

The finite state machine states of read interface are illustrated in the table 3.4 and figure 3-8

| State  | State | Description                                   |

|--------|-------|-----------------------------------------------|

| Number |       |                                               |

| 1      | IDLE  | Idle state when AXI4-lite is not active       |

| 2      | ADDR  | Wait for ARVALID signal to be high            |

|        | WAIT  |                                               |

| 3      | DATA  | Handshaking is done and data is read from the |

|        |       | given address                                 |

Table 3-4Read Operation States Illustration

Figure 3-8 Read Operation FSM of AXI4-Lite

#### 3.3.2. AXI4 Interface

#### Description

AXI4 interface is the secondary interface with the core, this interface has access only to two data registers in the Register Space; Transmit Data FIFO Data Write Port (TDFD) and Receive Data FIFO Data read Port (RDFD), it provides independent read and write channels where transactions take place on a two stage handshake which is very similar to AXI4-Lite interface.

The AXI4 protocol is very similar to AXI4-Lite interface except it supports more features; the AXI4 protocol supports three types of burst transactions specified by the signal **AxBURST** and a configurable burst length up to 256 transfers in incremental bursts and 16 transfers in fixed and wrapping bursts which is chosen by user and signaled by **AxLEN**.

The supported data bus width in the core is configurable and can be 32 bits or 64 bits.

The protocol supports full bus width or narrow transfers where the number of bytes used in data transfer are specified by the signal **AxSIZE**; however only bytes containing valid data is stored in write transactions. Valid data is indicated by the strobe signal where each bit corresponds to one byte of the data bus.

The AXI4 interface mainly deals with the data registers within the core where all read/write operations are passed to the Register Space via the interface and subsequently to data FIFOs if used has performed correct programming sequence, other information about data like packet destination and packet length must be written into core using AXI4-Lite interface.

# Interfacing

| Port name | Port<br>mode | Connection | Description                                                              |

|-----------|--------------|------------|--------------------------------------------------------------------------|

| ACLK      | Input        | User       | Global interface clock                                                   |

| ARESET    | Input        | User       | Resets entire core                                                       |

| AWADDR    | Input        | User       | Address of write transaction                                             |

| AWLEN     | Input        | User       | Number of transfers in a write<br>transaction                            |

| AWSIZE    | Input        | User       | Number of bytes used in each transfer in a write transaction             |

| AWBURST   | Input        | User       | Write transaction burst type                                             |

| AWVALID   | Input        | User       | Valid write address is available                                         |

| BREADY    | Input        | User       | Master ready to accept response                                          |

| ARADDR    | Input        | User       | Address of a read transaction                                            |

| ARLEN     | Input        | User       | Number of transfers in a read<br>transaction                             |

| ARSIZE    | Input        | User       | Number of bytes used in each transfer in a read transaction              |

| ARBURST   | Input        | User       | Read transaction burst type                                              |

| ARVALID   | Input        | User       | Valid read address is available                                          |

| RREADY    | Input        | User       | Master can accept read data                                              |

| WDATA     | Input        | User       | Data of a write transaction                                              |

| WSTRB     | Input        | User       | Indicates bytes lanes which contain<br>valid data in a write transaction |

| WVALID    | Input        | User       | Valid write data is available                                            |

| WLAST     | Output       | User       | Indicates last transfer in a write<br>transaction                        |

| WREADY    | Output       | User       | Slave can accept write data                                              |

| RDATA     | Output       | User       | Data of a read transaction                                               |

| RRESP     | Output       | User       | Status of a read transaction                                             |

| RLAST     | Output       | User       | Indicates last transfer in a read<br>transaction                         |

| RVALID    | Output       | User       | Valid data is available                                                  |

| ARREADY   | Output       | User       | Slave can accept read address                                            |

The AXI4 block contains I/O signals listed in Table 3-5.

| BRESP          | Output | User            | Statues of a write transaction                        |

|----------------|--------|-----------------|-------------------------------------------------------|

| BVALID         | Output | User            | Valid response is available in a write<br>transaction |

| AWREADY        | Output | User            | Slave can accept write address                        |

| read_enable    | Output | Register        | Read enable signal                                    |

|                |        | space           |                                                       |

| write_enable   | Output | Register        | Write enable signal                                   |

|                |        | space           |                                                       |

| write_address  | Output | Register        | Address of a write operation                          |

|                |        | space           |                                                       |

| Memory_address | Output | Register        | Address of a read operation                           |

|                |        | space           |                                                       |

| data_in        | Output | Register        | Data of a write operation                             |

|                | -      | space           | -                                                     |

| data out       | Input  | Register        | Data of a read operation                              |

| _              | 1      | space           | 1                                                     |

| STROBE OUT     | Output | Transmit        | Indicates which byte lanes contains                   |

| 2111022_001    | o mp m | control         | valid data in a write operation                       |

| WUSER          | Input  | User            | Not used                                              |

| WOBLIC         | mput   | 0.561           |                                                       |

| AWQOS          | Input  | User            | Not used                                              |

| AWPROT         | Input  | User            | Not used                                              |

| AWLOCK         | Input  | User            | Not used                                              |

| AWUSER         | Input  | User            | Not used                                              |

| ARQOS          | Input  | User            | Not used                                              |

| ARPROT         | Input  | User            | Not used                                              |

| ARLOCK         | Input  | User            | Not used                                              |

| ARUSER         | Input  | User            | Not used                                              |

| BUSER          | Output | User            | Not used                                              |

| BID            | Output | User            | Not used                                              |

| WUSER          | Input  | User            | Not used                                              |

| RID            | Output | User            | Not used                                              |

|                |        | Table 3-5AXI4 L |                                                       |

Table 3-5AXI4 I/O signals

#### Functionality

The AXI4 interface is responsible for read/write operations from/into two register in the Register Space (TDFD and RDFD); this is done through five channels similar to AXI4-Lite interface.

This AXI4 protocol has 3 modes of operation (burst types) for write and read transactions

- 1. Fixed Burst

- 2. Incrementing Burst

- 3. Wrapping Burst

Although AXI4- interface can support the three mode of operation; only fixed bursts are used since user will have access to only one register in each path (transmit path and receive path). Write and read transaction are performed by the same concept illustrated in AXI4-Lite interface; however, since AXI4 supports more advanced features; the write/read transactions are slightly different.

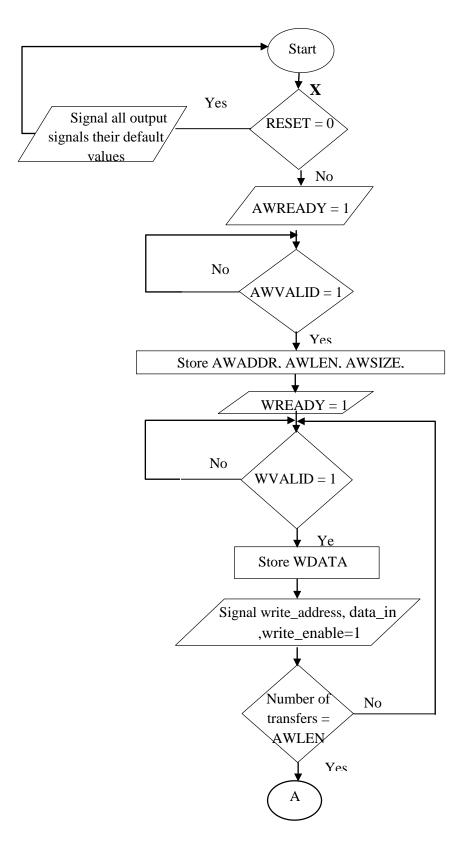

The Write operation is done as follows

- The Address of the intended register to be written in and burst information are carried out on the Write Address Channel, when the handshake between the AWVALID and AWREADY takes place, the core has read the address of the register to be written in successfully and information about the transaction like transaction size, length and burst type are stored.

- The actual data is written on the Write Data Channel, when the handshake between the WVALID and WREADY takes place, this indicates that the core has read the data successfully, this step is performed as many times as transaction length.

- The core then replies with a Response signal to feedback the write transaction statues and similarly BREADY and BVALID perform the handshake.

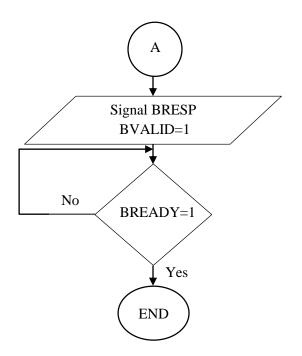

The Read operation is done as follows

- The Address of the intended register to be read from and burst information are written on the Read Address Channel, and the handshake between the ARVALID and ARREADY takes place, which indicates that the core has read the control signals successfully.

- Data to be read is written from the core on the Read Data Channel, and the handshake between the RVALID and RREADY takes place, which indicates that the user has read the written data by the core successfully. This step is performed as many times as transaction length.

• The RRESP signal is signaled from core to feedback the read transaction statues.

Write transaction over AXI4 channel is illustrated by the flow chart in figure 3-9

Figure 3-9AXI4 Write tranasaction FlowChart

Note: Resetting AXI4 at any point will result in going to start point (marked **X** at flow chart)

Read transaction over AXI4 channel is illustrated by the flow chart in figure 3.10

Figure 3-10 AXI4 Read transaction Flow Chart

Note: Resetting AXI4 at any point will result in going to start point (marked  $\mathbf{X}$  at flow chart

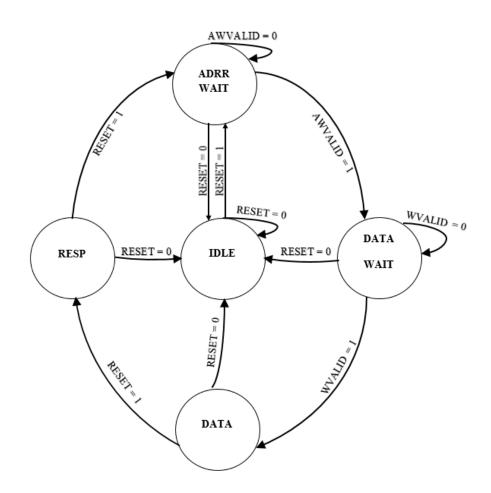

## Implementation

AXI4 unit is divided into two main blocks as illustrated in the figure 3.11; Write interface is responsible for write transactions and **Read interface** is responsible for read transactions, AXI4 Interface is implemented by two finite state machines.

Figure 3-11AXI4 block diagram

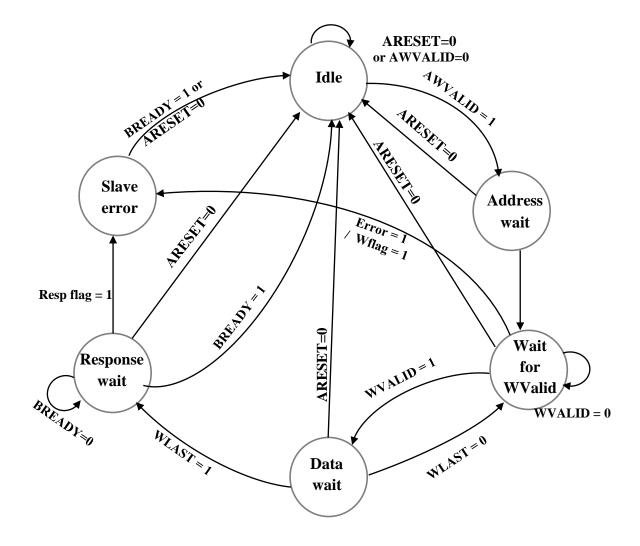

# Write Interface

The finite state machine of write operation states is illustrated in the table3-6 and figure3-12

| State<br>Number | State           | Description                                     |

|-----------------|-----------------|-------------------------------------------------|

| 1               | IDLE            | Idle state when write interface is not active   |

| 2               | Address wait    | Valid address is stored                         |

| 3               | Wait for WVALID | Waiting state for data to be available          |

| 4               | Data wait       | Valid data is written                           |

| 5               | Response wait   | Waiting state for master to accept write        |

|                 |                 | response                                        |

| 6               | Slave error     | Error state to feedback a slave error to master |

Table 3-6Write operation states illustration

Figure 3-12Write Operation FSM of AXI4

| Transition     | Description                                      | Condition   |

|----------------|--------------------------------------------------|-------------|

| condition      | -                                                |             |

| Reset          | Reset AXI4 interface and entire core             | ARREST=0    |

| Valid address  | Valid address and control signals are available  | AWVALID=1   |

| Valid data     | Valid data is available                          | WVALID=1    |

| Last           | Last transfer in a write transaction             | WLAST=1     |

|                |                                                  |             |

| Response ready | Master can accept write response                 | BREADY=1    |

|                |                                                  |             |

| Slave error    | Slave wishes to return an error condition to the | Error=1     |

|                | master                                           |             |

|                |                                                  |             |

| Time out write | Master has exceeded a parameterized maximum      | Wflag=1     |

| error          | number of clock cycles without a data transfer   |             |

| Time out       | Master has exceeded a parameterized maximum      | Respflag =1 |

| response error | number of clock cycles without responding to     |             |

|                | valid data                                       |             |

The finite state machine transition conditions are illustrated in the table 3-7

Table 3-7AXI4 Write Interface FSM transition conditions illustration

The finite state machine outputs corresponding to each state are illustrated in the table 3-8

| Outputs | State number |    |    |    |    |    |  |

|---------|--------------|----|----|----|----|----|--|

|         | 1            | 2  | 3  | 4  | 5  | 6  |  |

| AWREADY | 0            | 1  | 0  | 0  | 1  | 1  |  |

| WREADY  | 0            | 0  | 0  | 1  | 0  | 0  |  |

| BRESP   | 00           | 00 | 00 | 00 | 00 | 10 |  |

| BVALID  | 0            | 0  | 0  | 0  | 1  | 1  |  |

Table 3-8AXI4 write operation FSM outputs

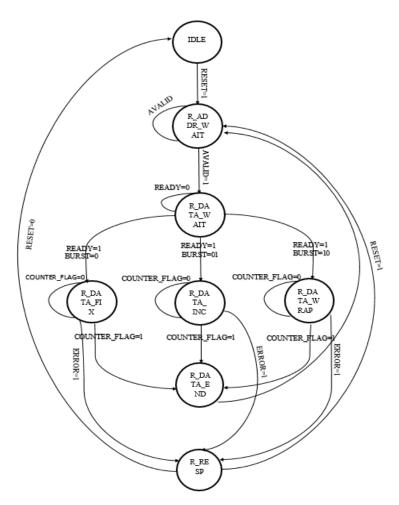

# **Read Interface**

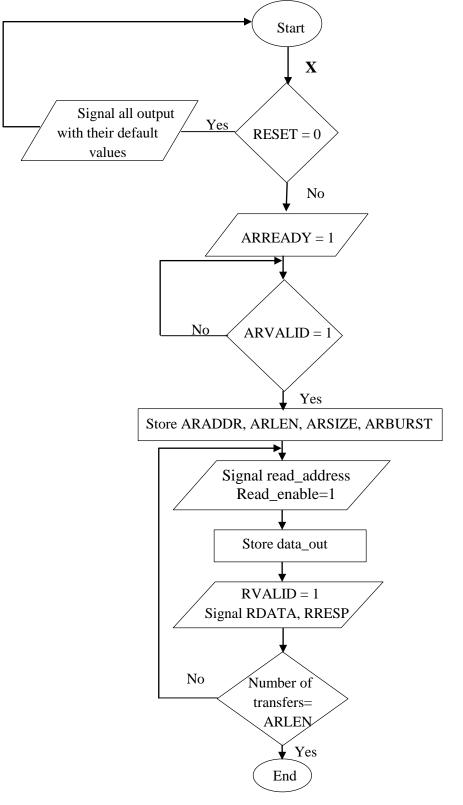

The finite state machine of read operation states are illustrated in the table.3.9 and figure 3.13

| State  | State       | Description                                      |  |  |  |  |

|--------|-------------|--------------------------------------------------|--|--|--|--|

| Number |             |                                                  |  |  |  |  |

| 1      | IDLE        | Idle state when AXI4-lite is not active          |  |  |  |  |

| 2      | R_ADR_WAIT  | Wait for AVALID signal to be high                |  |  |  |  |

| 3      | R_DATA_WAIT | Wait for READY signal to be high                 |  |  |  |  |

| 4      | R_DATA_FIX  | Move to this state if RBURST = "00" which        |  |  |  |  |

|        |             | indicates fixed mode                             |  |  |  |  |

| 5      | R_DATA_INCR | Move to this state if RBURST = "01" which        |  |  |  |  |

|        |             | indicates incrementing mode                      |  |  |  |  |

| 6      | R_DATA_WRAP | Move to this state if RBURST = "10" which        |  |  |  |  |

|        |             | indicates wrapping mode                          |  |  |  |  |

| 7      | R_DATA_END  | Move to this state after ending read transaction |  |  |  |  |

| 8      | R_RES       | Responsible for informing correct or incorrect   |  |  |  |  |

|        |             | read operation                                   |  |  |  |  |

Table 3-9AXI4 Read operation states

Figure 3-13 AXI4 Read Operation FSM

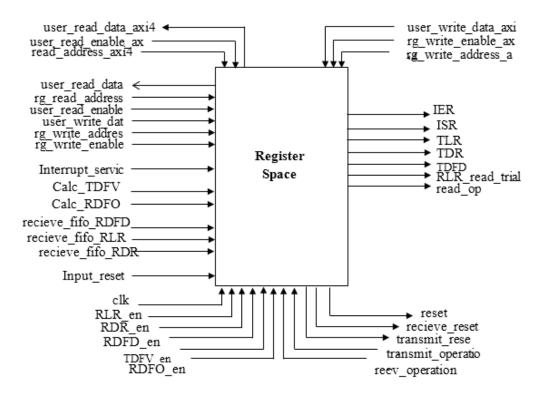

# 3.3.3. Register Space

# Description

The Register Space contains all the registers that the user needs to interact with the core whether through write or read operations to operate the block, it contains thirteen registers where the AXI4-lite interface have access to the thirteen registers in case of using AXI4-lite as data interface, while in case of using AXI4 as data interface the AXI4-lite has access to eleven of the thirteen registers while the AXI4 has access to the data interface registers Transmit Data FIFO Write port (TDFD) and the Receive Data FIFO Read port (RDFD).

# Interfacing

| Port Name              | Port   | Connection          | Description                |

|------------------------|--------|---------------------|----------------------------|

|                        | mode   |                     |                            |

| user_read_data         | Output | AXI4-lite interface | Outputs the stored value   |

| rg_read_address        | Input  |                     | in system registers to the |

| user_read_enable       | Input  |                     | user                       |

| user_read_data_axi4    | Output | AXI4 interface      | Outputs the value stored   |

| rg_read_address_axi4   | Input  |                     | in the RDFD register       |

| user_read_enable_axi4  | Input  |                     | <b>ONLY</b> to the user    |

| user_write_data        | Input  | AXI4-lite interface | Responsible of storing     |

| rg_write_address       | Input  |                     | the data written by the    |

| user_write_enable      | Input  |                     | user through the to the    |

|                        |        |                     | register of the            |

|                        |        |                     | corresponding address      |

| user_write_data_axi4   | Input  | AXI4 interface      | Responsible of storing     |

| rg_write_address_axi4  | Input  |                     | the data written by the    |

| user_write_enable_axi4 | Input  |                     | user to the TDFD           |

|                        |        |                     | register ONLY              |

| Calc_TDFV              | Input  | Calculation unit    | The values of the          |

| Calc_RDFO              | Input  |                     | vacancy and occupancy      |

|                        |        |                     | to be stored in the        |

|                        |        |                     | corresponding registers    |

| recieve_fifo_RDFD      | Input  | receive FIFO        | The values of the data,    |

| recieve_fifo_RLR       | Input  |                     | length and destination to  |

| recieve_fifo_RDR       | Input  |                     | be stored in the           |

|                        |        |                     | corresponding registers    |

|                        |        |                     |                            |

| RDFD_en                | Input  | Receive Control and | The enable signals to      |

| RLR_en                 | Input  | Transmit Control    | save the incoming data     |

| RDR_en                 | Input  |                     | to the corresponding       |

|                        | Input  |                     | register                   |

The I/O signal description is illustrated in Table 3-10

| TDFV_en           | Input    |                     |                             |

|-------------------|----------|---------------------|-----------------------------|

| _                 | Input    |                     |                             |

| RDFO_en           | <b>T</b> |                     |                             |

| input_reset       | Input    | AXI4-lite interface | The reset to the whole      |

|                   |          |                     | core                        |

| Interrupt_service | Input    | Interrupt Interface | The interrupt status of     |

|                   |          |                     | the system to be stored     |

|                   |          |                     | in the ISR                  |

| RLR_read_trial    | Output   | Interrupt Interface | Used to trigger receive     |

|                   | 1        | 1                   | underrun read interrupt     |

| Read_op           | Output   | Interrupt Interface | Used to trigger receive     |

|                   | o mp m   |                     | underrun interrupt          |

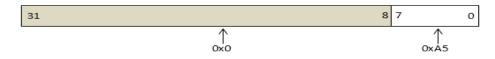

| Reset             | Output   | All other modules   | The general reset to the    |

| INDOL             | Julput   |                     | whole core which can be     |

|                   |          |                     |                             |

|                   |          |                     | triggered due to external   |

|                   |          |                     | reset or writing 0xA5 to    |

|                   | -        |                     | SRR                         |

| Receive_reset     | Output   | Receive Control     | Reset to the receive        |

|                   |          | Receive FIFO        | blocks only which is        |

|                   |          |                     | triggered due to writing    |

|                   |          |                     | 0xA5 to the RDFR            |

| Transmit_reset    | Output   | Transmit Control    | Reset to the transmit       |

|                   | -        | Transmit FIFO       | blocks only which is        |

|                   |          |                     | triggered due to writing    |

|                   |          |                     | 0xA5 to the TDFR            |

| ISR               | Output   | Interrupt Interface | To generate the interrupt   |

|                   | output   | interrupt interruce | bit                         |

| IER               | Output   | Interrupt Interface | To generate the interrupt   |

|                   |          |                     | bit                         |

| TLR               | Output   | Transmit Length     | Outputs the length          |

|                   | 1        | FIFO                | written by the user         |

| TDR               | Output   | Transmit            | Outputs the destination     |

|                   | -        | Destination FIFO    | written by the user         |

| TDFD              | Output   | Transmit Data FIFO  | Outputs the data written by |

|                   | Î        |                     | the user                    |

Table 3-10Register Space I/O signals

# Functionality

Register Space has thirteen registers that the user needs to operate the core, in the following section a brief description of each register.

The description of each register is as follows:

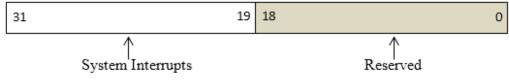

# **Interrupt Service Register (ISR)**

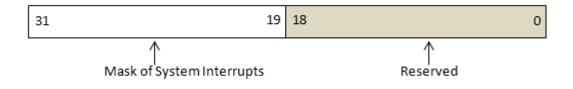

The System supports 13 different interrupts each is represented by one bit from bit 19 to bit 31, The ISR structure is shown in Figure 3.14. The supported interrupts and their corresponding bits in the ISR register are shown as follows in Table 3-11

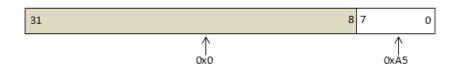

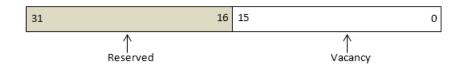

Figure 3-14 Interrupt Service Register (offset 0x00)

Core Access: Read/Clear on Write Reset Value: 0x01D00000 Description: returns the interrupts generated by the system

| Bits     | Name    | Core Access                     | Reset<br>Value | Description                                                                                                                                             |

|----------|---------|---------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-<br>18 | Reserve | Read                            | 0x0            | Reserved for future definition                                                                                                                          |

| 19       | RFPE    | Read/<br>Clear on<br>write of 1 | 0              | <b>Receive FIFO Programmable Empty:</b><br>triggered when the difference between read and write pointer of<br>receive FIFO equals the Empty threshold   |

| 20       | RFPF    | Read/<br>Clear on<br>write of 1 | 1              | <b>Receive FIFO Programmable Full:</b> triggered when the difference between read and write pointer of receive FIFO equals the Full threshold           |

| 21       | TFPE    | Read/<br>Clear on<br>write of 1 | 0              | <b>Transmit FIFO Programmable Empty:</b> triggered when<br>the difference between read and write pointer of transmit FIFO<br>equals the Empty threshold |

| 22       | TFPF    | Read/<br>Clear on<br>write of 1 | 1              | <b>Transmit FIFO Programmable Full:</b> triggered when the difference between read and write pointer of transmit FIFO equals the Full threshold         |

| 23       | RRC     | Read/<br>Clear on<br>write of 1 | 1              | <b>Receive Reset Complete:</b> the reset of receive logic has completed                                                                                 |